#### Design Methodologies for Single Flux Quantum VLSI Circuits

by

Gleb Krylov

Submitted in Partial Fulfillment

of the

Requirements for the Degree Doctor of Philosophy

Supervised by Professor Eby G. Friedman

Department of Electrical and Computer Engineering Arts, Sciences and Engineering Edmund A. Hajim School of Engineering and Applied Sciences

> University of Rochester Rochester, New York 2021

# Table of Contents

| В                         | iogra  | phical | Sketch                                    | 2    | < |

|---------------------------|--------|--------|-------------------------------------------|------|---|

| $\mathbf{A}$              | ckno   | wledgr | nents                                     | xiv  | V |

| $\mathbf{A}$              | bstra  | ıct    |                                           | XV   | i |

| $\mathbf{C}$              | ontri  | butors | and Funding Sources                       | xvii | i |

| $\mathbf{L}_{\mathbf{i}}$ | ist of | Table  | S                                         | XX   | K |

| $\mathbf{L}_{\mathbf{i}}$ | ist of | Figur  | es                                        | xxi  | i |

| 1                         | Intr   | oduct  | ion                                       | -    | 1 |

|                           | 1.1    | Types  | of computing systems                      | . 1  | 1 |

|                           | 1.2    | Remo   | te (cloud) computing                      | . 1  | 4 |

|                           | 1.3    | Super  | conductive electronics                    | . 10 | 6 |

|                           | 1.4    | Outlin | ne                                        | . 2  | 1 |

| <b>2</b>                  | Phy    | sics a | nd devices of superconductive electronics | 2    | 7 |

|                           | 2.1    | Introd | luction                                   | . 2' | 7 |

|                           | 2.2    | Theor  | ies of superconductivity                  | . 28 | 3 |

|                           |        | 2.2.1  | London theory                             | . 28 | 3 |

|                           |        | 2.2.2  | Ginzburg-Landau theory                    | . 3  | 1 |

|                           |        | 2.2.3  | Bardeen-Cooper-Schrieffer (BCS) theory    | . 32 | 2 |

|                           | 2.3    | Prope  | rties of superconductive materials        | . 33 | 3 |

|   |     | 2.3.1             | Meissner effect                                     |

|---|-----|-------------------|-----------------------------------------------------|

|   |     | 2.3.2             | Quantization of magnetic flux                       |

|   |     | 2.3.3             | Energy gap                                          |

|   |     | 2.3.4             | Quasiparticles                                      |

|   |     | 2.3.5             | London penetration depth                            |

|   |     | 2.3.6             | Critical field and critical current                 |

|   |     | 2.3.7             | Coherence length                                    |

|   |     | 2.3.8             | Type-I and type-II superconductors                  |

|   |     | 2.3.9             | Low and high temperature superconductors 45         |

|   |     | 2.3.10            | Kinetic inductance                                  |

|   | 2.4 | Joseph            | son junctions                                       |

|   |     | 2.4.1             | Josephson effects                                   |

|   |     | 2.4.2             | Josephson inductance                                |

|   |     | 2.4.3             | Josephson energy                                    |

|   |     | 2.4.4             | JJ circuit models                                   |

|   |     | 2.4.5             | Dynamics of Josephson junctions                     |

|   | 2.5 | Superc            | conductive devices                                  |

|   |     | 2.5.1             | Superconductive nanowire single photon detectors 60 |

|   |     | 2.5.2             | Cryotron                                            |

|   |     | 2.5.3             | Nanocryotron                                        |

|   |     | 2.5.4             | Superconductor-ferromagnetic devices                |

|   | 2.6 | Conclu            | sions                                               |

| 3 | Sup | $\mathbf{ercond}$ | luctive circuits 67                                 |

|   | 3.1 | SQUII             | D                                                   |

|   |     | 3.1.1             | Single junction SQUID                               |

|   |     | 3.1.2             | Two junction SQUID                                  |

|   | 3.2 | Voltag            | e level logic                                       |

|   | 3.3 | RSFQ              | Logic                                               |

|   | 3.4 | Recipr            | ocal quantum logic                                  |

|   | 3.5 | Adiaba            | atic superconductive logic                          |

|   |     | 3.5.1   | Reversible computing                                |

|---|-----|---------|-----------------------------------------------------|

|   |     | 3.5.2   | Adiabatic quantum flux parametron                   |

|   | 3.6 | Memo    | ry                                                  |

|   |     | 3.6.1   | Josephson memory                                    |

|   |     | 3.6.2   | Cryogenic CMOS memory                               |

|   |     | 3.6.3   | Spin-based memory                                   |

|   | 3.7 | Concl   | usions                                              |

| 4 | Rap | oid sin | gle flux quantum (RSFQ) circuits 93                 |

|   | 4.1 | Trans   | mission lines                                       |

|   |     | 4.1.1   | Josephson transmission lines                        |

|   |     | 4.1.2   | Passive transmission lines                          |

|   | 4.2 | Logic   | gates and flip flops                                |

|   |     | 4.2.1   | D flip flop                                         |

|   |     | 4.2.2   | Buffer                                              |

|   |     | 4.2.3   | Splitter                                            |

|   |     | 4.2.4   | Confluence buffer                                   |

|   |     | 4.2.5   | OR and AND gates                                    |

|   |     | 4.2.6   | Inverter                                            |

|   |     | 4.2.7   | Muller C element                                    |

|   |     | 4.2.8   | SFQ-to-DC and DC-to-SFQ converters                  |

|   | 4.3 | Bias n  | networks in RSFQ                                    |

|   |     | 4.3.1   | Bias distribution in RSFQ circuits                  |

|   |     | 4.3.2   | Energy efficient bias distribution in RSFQ circuits |

|   | 4.4 | Concl   | usions                                              |

| 5 | Syn | chroni  | zation 127                                          |

|   | 5.1 | Synch   | ronous RSFQ circuits                                |

|   |     | 5.1.1   | Common RSFQ clocking schemes                        |

|   |     | 5.1.2   | Hybrid clocking approaches                          |

|   |     | 5.1.3   | GALS                                                |

|   |     | 511     | Dynamic SEO                                         |

|   | 5.2 | Asynchronous RSFQ circuits |                                   |     |  |

|---|-----|----------------------------|-----------------------------------|-----|--|

|   |     | 5.2.1                      | Handshaking protocols             | 136 |  |

|   |     | 5.2.2                      | Dual-rail logic                   | 138 |  |

|   | 5.3 | AQFP                       | eircuits                          | 140 |  |

|   | 5.4 | Conclu                     | usions                            | 143 |  |

| 6 | Sup | ercono                     | luctive IC manufacturing          | 144 |  |

|   | 6.1 | Supero                     | conductive IC fabrication process | 145 |  |

|   |     | 6.1.1                      | Material deposition               | 148 |  |

|   |     | 6.1.2                      | Patterning                        | 153 |  |

|   |     | 6.1.3                      | Josephson junctions               | 154 |  |

|   | 6.2 | Manuf                      | facturing features and challenges | 155 |  |

|   |     | 6.2.1                      | Planarization                     | 156 |  |

|   |     | 6.2.2                      | High kinetic inductance layer     | 157 |  |

|   |     | 6.2.3                      | Self-shunted junctions            | 157 |  |

|   |     | 6.2.4                      | 3-D integration                   | 158 |  |

|   | 6.3 | Conclu                     | usions                            | 159 |  |

| 7 | ED  | A for s                    | superconductive electronics       | 161 |  |

|   | 7.1 | Cell li                    | brary design and characterization | 166 |  |

|   | 7.2 | RTL d                      | lesign and simulation             | 170 |  |

|   | 7.3 | Circui                     | t simulation                      | 174 |  |

|   | 7.4 | Induct                     | cance extraction                  | 178 |  |

|   | 7.5 | Logic                      | synthesis                         | 180 |  |

|   |     | 7.5.1                      | Logic representation              | 181 |  |

|   |     | 7.5.2                      | Path balancing                    | 184 |  |

|   | 7.6 | Layou                      | t synthesis                       | 185 |  |

|   | 7.7 | Timin                      | g analysis                        | 189 |  |

|   |     | 7.7.1                      | Timing constraints                | 190 |  |

|   |     | 7.7.2                      | STA techniques                    | 195 |  |

|   | 7.8 | Verific                    | eation and testability            | 195 |  |

|   | 7.9 | Concli                     | usions                            | 198 |  |

| 8  | Con  | npact 1 | model of superconductor-ferromagnetic transistor               | 200 |

|----|------|---------|----------------------------------------------------------------|-----|

|    | 8.1  | Introdu | $\operatorname{uction}$                                        | 201 |

|    | 8.2  | Compa   | act model of the SFT device                                    | 202 |

|    |      | 8.2.1   | SFT device operation                                           | 202 |

|    |      | 8.2.2   | Critical current and suppression of superconductive energy gap | 204 |

|    |      | 8.2.3   | Gain and threshold voltage model                               | 206 |

|    |      | 8.2.4   | Reactive parameters of the injector                            | 206 |

|    |      | 8.2.5   | Asymmetry parameter                                            | 207 |

|    | 8.3  | Model   | verification                                                   | 209 |

|    | 8.4  | Conclu  | sions                                                          | 211 |

| 9  | Indu | uctive  | coupling noise in multilayer superconductive ICs               | 212 |

|    | 9.1  | Source  | s of inductive noise coupling                                  | 214 |

|    |      | 9.1.1   | PTL noise coupling                                             | 214 |

|    |      | 9.1.2   | Coupling of bias current                                       | 216 |

|    |      | 9.1.3   | Techniques for coupling evaluation                             | 216 |

|    | 9.2  | Induct  | ive coupling for common circuit structures                     | 217 |

|    |      | 9.2.1   | Existing experimental data                                     | 217 |

|    |      | 9.2.2   | Coupling between parallel PTL lines                            | 218 |

|    |      | 9.2.3   | Coupling between perpendicular PTL lines with and without      |     |

|    |      |         | overlap                                                        | 221 |

|    |      | 9.2.4   | Coupling between M0 bias lines and logic gates                 | 223 |

|    | 9.3  | Effects | of coupling on circuits and mitigation guidelines              | 224 |

|    |      | 9.3.1   | Effects of PTL noise coupling                                  | 224 |

|    |      | 9.3.2   | Effects of bias current coupling                               | 226 |

|    | 9.4  | Conclu  | sions                                                          | 227 |

| 10 | Sens | se amp  | olifier for spin-based cryogenic memory cell                   | 228 |

|    | 10.1 | Circuit | components                                                     | 229 |

|    |      | 10.1.1  | Memory cell readout $\dots$                                    | 230 |

|    |      | 10.1.2  | Synchronous DC/SFQ converter as memory sense amplifier         | 232 |

|    |      | 10.1.3  | Sense amplifier topologies                                     | 234 |

|           | 10.2 | Simulation results                                           | 235 |

|-----------|------|--------------------------------------------------------------|-----|

|           | 10.3 | Conclusions                                                  | 238 |

| 11        | Dyn  | amic single flux quantum majority gates                      | 240 |

|           | 11.1 | Introduction                                                 | 241 |

|           | 11.2 | Dynamic SFQ storage loops                                    | 243 |

|           | 11.3 | Circuit design of dynamic loops                              | 246 |

|           | 11.4 | Majority gates                                               | 249 |

|           | 11.5 | Applications and advantages                                  | 256 |

|           | 11.6 | Conclusions                                                  | 260 |

| <b>12</b> | Desi | gn guidelines for ERSFQ bias networks                        | 261 |

|           | 12.1 | Introduction                                                 | 262 |

|           | 12.2 | Example circuit and analysis methodology                     | 264 |

|           | 12.3 | Trends and guidelines of ERSFQ bias networks                 | 271 |

|           |      | 12.3.1 Bias inductance                                       | 272 |

|           |      | 12.3.2 Topology of FJTL stage                                | 274 |

|           |      | 12.3.3 Bias margins of FJTL                                  | 276 |

|           |      | 12.3.4 Size of FJTL                                          | 278 |

|           |      | 12.3.5 Inductance of bias bus                                | 281 |

|           | 12.4 | Distributed FJTL methodology                                 | 285 |

|           | 12.5 | Conclusions                                                  | 288 |

| <b>13</b> | Part | itioning RSFQ Circuits for Current Recycling                 | 290 |

|           | 13.1 | Introduction                                                 | 291 |

|           | 13.2 | Current recycling                                            | 292 |

|           | 13.3 | Partitioning of arbitrary RSFQ circuits during placement     | 294 |

|           |      | 13.3.1 Unbalanced partitioning of RSFQ circuits with padding | 294 |

|           |      | 13.3.2 Partitioning during placement                         | 296 |

|           |      | 13.3.3 Coarse placement                                      | 298 |

|           |      | 13.3.4 Partitioning using Fiduccia-Mattheyses heuristic      | 300 |

|           |      | 13.3.5 Geometric partitioning with simulated annealing       | 305 |

|    | 13.4 | Conclusions                                                           | 307         |

|----|------|-----------------------------------------------------------------------|-------------|

| 14 | Wav  | ve Pipelining in DSFQ Circuits                                        | 308         |

|    | 14.1 | Path balancing and wave pipelining in RSFQ systems                    | 309         |

|    | 14.2 | Path delay balancing in DSFQ circuits                                 | 311         |

|    |      | 14.2.1 Delay balancing                                                | 312         |

|    |      | 14.2.2 Inverter propagation                                           | 314         |

|    |      | 14.2.3 Benchmark circuits                                             | 316         |

|    |      | 14.2.4 DSFQ circuits without path balancing                           | 318         |

|    | 14.3 | Partial path balancing and wave pipelining                            | 320         |

|    |      | 14.3.1 Necessary conditions for wave pipelining                       | 320         |

|    |      | 14.3.2 Full path balancing                                            | 321         |

|    |      | 14.3.3 Partial path balancing                                         | 323         |

|    | 14.4 | Conclusions                                                           | 328         |

| 15 | GAI  | LS clocking and shared interconnect for large scale SFQ systems       | <b>32</b> 9 |

|    | 15.1 | Introduction                                                          | 330         |

|    | 15.2 | GALS clocking scheme for SFQ circuits                                 | 331         |

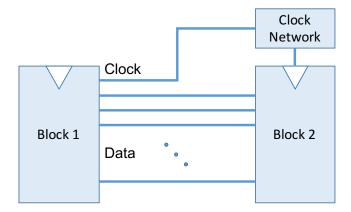

|    |      | 15.2.1 Ambiguity of clock and data                                    | 332         |

|    |      | 15.2.2 Clock generation and distribution                              | 333         |

|    |      | 15.2.3 Clock activation scheme                                        | 334         |

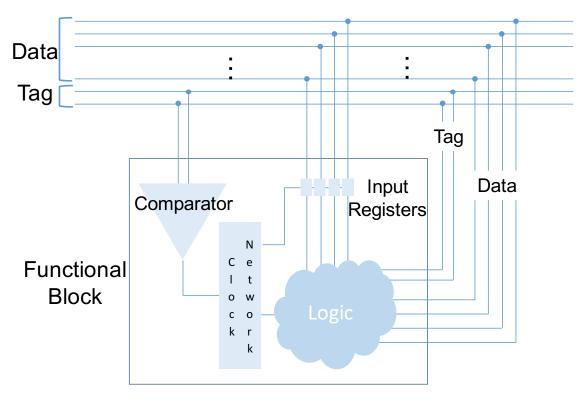

|    | 15.3 | Shared interconnect                                                   | 336         |

|    |      | 15.3.1 Types of SFQ interconnect                                      | 336         |

|    |      | 15.3.2 Input discrimination                                           | 337         |

|    |      | 15.3.3 Bus topology                                                   | 337         |

|    | 15.4 | Behavioral characteristics                                            | 339         |

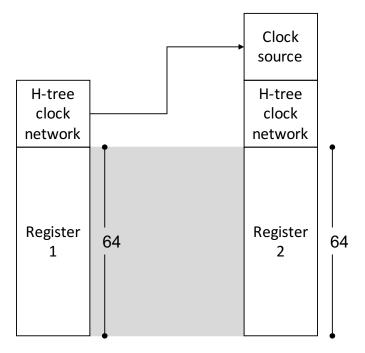

|    |      | 15.4.1 Behavior of H-tree clock networks                              | 340         |

|    |      | 15.4.2 Behavior of H-tree and concurrent networks                     | 341         |

|    |      | 15.4.3 Approaches for clock activation and distribution               | 343         |

|    |      | 15.4.4 Multi-chip modules                                             | 344         |

|    |      | 15.4.5 Compatibility of energy efficient SFQ with proposed approaches | 344         |

|    | 15.5 | Conclusions                                                           | 345         |

| 16        | Desi          | ign for | testability of SFQ circuits                                    | 347  |

|-----------|---------------|---------|----------------------------------------------------------------|------|

|           | 16.1          | Introd  | uction                                                         | 348  |

|           | 16.2          | Reduc   | ing DFT overhead                                               | 351  |

|           |               | 16.2.1  | Replacing multiplexers                                         | 351  |

|           |               | 16.2.2  | Blocking gates                                                 | 352  |

|           | 16.3          | Test p  | oint insertion for SFQ circuits                                | 359  |

|           |               | 16.3.1  | Test process                                                   | 361  |

|           |               | 16.3.2  | Comparison of blocking gates with multiplexers                 | 362  |

|           |               | 16.3.3  | Advantages and disadvantages of test point insertion $\dots$   | 365  |

|           | 16.4          | Set/sc  | an chains for SFQ circuits                                     | 365  |

|           | 16.5          | Conclu  | isions                                                         | 369  |

| <b>17</b> | 7 Future work |         |                                                                | 370  |

|           | 17.1          | Novel   | DSFQ circuits                                                  | 371  |

|           |               | 17.1.1  | Novel DSFQ functions                                           | 372  |

|           |               | 17.1.2  | DSFQ nonimplication logic                                      | 373  |

|           |               | 17.1.3  | SFQ pulse gating and SFQ pulse source for asynchronous circuit | s374 |

|           | 17.2          | Design  | techniques to improve performance of DSFQ circuits             | 375  |

|           |               | 17.2.1  | Modifying retention time after placement                       | 375  |

|           |               | 17.2.2  | Integrating splitters into standard cells                      | 376  |

|           |               | 17.2.3  | Exploiting latching function of RSFQ gates                     | 377  |

|           |               | 17.2.4  | Changing routing priority for different paths                  | 378  |

|           | 17.3          | Cryoge  | enic memory circuits                                           | 379  |

| 18        | Con           | clusio  | ns                                                             | 381  |

| Bi        | bliog         | raphy   |                                                                | 385  |

### Biographical Sketch

Gleb Krylov graduated from the National Research Nuclear University MEPhI (former Moscow Engineering Physics Institute) in Moscow, Russia in 2014, with the Specialist degree in computer science and engineering. Between 2011 and 2015, he held a variety of software and hardware engineering positions in Moscow, Russia. He received the M.S. degree in electrical engineering from the University of Rochester in Rochester, New York in 2017, where he is currently working toward the Ph.D. degree in electrical and computer engineering. He was an intern with Hypres Inc., Elmsford, New York, in 2017 and with Synopsys Inc., Mountain View, California in 2018. His current research interests include cryogenic and superconductive electronics, quantum computing, and electronic design automation. The following publications are a result of the work conducted during his doctoral study.

#### Book

1. **G. Krylov** and E. G. Friedman, *Single Flux Quantum Integrated Circuit Design*, Springer, ISBN # 978-3-030-76884-3, 2022 (in press).

#### Journal papers

1. **G. Krylov**, J. Kawa, and E. G. Friedman, "Design Automation of Superconductive Digital Circuits," *IEEE Nanotechnology Magazine*, in submission

- 2. **G. Krylov** and E. G. Friedman, "Wave Pipelining in DSFQ Circuits," *IEEE Transactions on Applied Superconductivity*, in submission

- 3. **G. Krylov** and E. G. Friedman, "Inductive Noise Coupling in Multilayer Superconductive ICs," *Microelectronics Journal*, in submission

- 4. **G. Krylov** and E. G. Friedman, "Partitioning RSFQ Circuits for Current Recycling," *IEEE Transactions on Applied Superconductivity*, Vol. 31, No. 5, pp. 1–6, Art no. 1301706, August 2021.

- 5. T. Jabbari, **G. Krylov**, J. Kawa, and E. G. Friedman, "Splitter Trees in Single Flux Quantum Circuits," *IEEE Transactions on Applied Superconductivity*, Vol. 31, No. 5, pp. 1–6, Art no. 1302606, August 2021.

- 6. T. Jabbari, **G. Krylov**, and E. G. Friedman, "Logic Locking in SFQ Technology," *IEEE Transactions on Applied Superconductivity*, Vol. 31, No. 5, pp. 1–5, Art no. 1301605, August 2021.

- T. Jabbari, G. Krylov, S. Whiteley, J. Kawa, and E. G. Friedman, "Repeater Insertion in SFQ Interconnect," *IEEE Transactions on Applied Superconductiv*ity, Vol. 30, No. 8, pp. 1–8, December 2020.

- 8. **G. Krylov** and E. G. Friedman, "Design Methodology for Distributed Large Scale ERSFQ Bias Networks," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, Vol. 28, No. 11, pp. 2438–2447, November 2020.

- 9. **G. Krylov** and E. G. Friedman, "Asynchronous Dynamic Single Flux Quantum Majority Gates," *IEEE Transactions on Applied Superconductivity*, Vol. 30, No. 5, pp. 1–7, Art no. 1300907, August 2020.

- H. Kumar, T. Jabbari, G. Krylov, K. Basu, E. G. Friedman, and R. Karri, "Toward Increasing the Difficulty of Reverse Engineering of RSFQ Circuits," IEEE Transactions on Applied Superconductivity, Vol. 30, No. 3, pp. 1–13, Art no. 1700213, April 2020.

- G. Krylov and E. G. Friedman, "Globally Asynchronous, Locally Synchronous Clocking and Shared Interconnect for Large-Scale SFQ Systems," *IEEE Transactions on Applied Superconductivity*, Vol. 29, No. 5, pp. 1–5, Art no. 3603205, August 2019.

- 12. **G. Krylov** and E. G. Friedman, "Sense Amplifier for Spin-Based Cryogenic Memory Cells," *IEEE Transactions on Applied Superconductivity*, Vol. 29, No. 5, pp. 1–4, August 2019.

- 13. T. Jabbari, **G. Krylov**, S. Whiteley, E. Mlinar, J. Kawa, and E. G. Friedman, "Interconnect Routing for Large-Scale RSFQ Circuits," *IEEE Transactions on Applied Superconductivity*, Vol. 29, No. 5, pp. 1–5, Art no. 1102805, August 2019.

- 14. **G. Krylov** and E. G. Friedman, "Design for Testability of SFQ Circuits," *IEEE Transactions on Applied Superconductivity*, Vol. 27, No. 8, pp. 1–7, Art no. 1302307, December 2017.

#### Conference papers

- 1. **G. Krylov** and E. G. Friedman, "Inductive Noise Coupling in Superconductive Passive Transmission Lines," *Proceedings of the IEEE International Midwest Symposium on Circuits and Systems*, August 2021 (in press)

- 2. S. Whiteley, E. Mlinar, G. Krylov, T. Jabbari, E. G. Friedman, and J. Kawa, "An SFQ Digital Circuit Technology with Fully-Passive Transmission Line Interconnect," *Proceedings of the Applied Superconductivity Conference*, November 2020.

- 3. **G. Krylov** and E. G. Friedman, "Bias Distribution in ERSFQ VLSI Circuits," *Proceedings of the IEEE International Symposium on Circuits and Systems*, pp. 1–5, October 2020.

- 4. **G. Krylov** and E. G. Friedman, "Bias Networks for High Complexity Energy Efficient Single Flux Quantum Circuits," *Proceedings of the Government Microcircuit Applications & Critical Technology Conference*, March 2020.

- 5. T. Jabbari, **G. Krylov**, S. Whiteley, J. Kawa, and E. G. Friedman, "Resonance Effects on SFQ Interconnect," *Proceedings of the Government Microcircuit Applications & Critical Technology Conference*, March 2020.

- 6. T. Jabbari, G. Krylov, S. Whiteley, J. Kawa, and E. G. Friedman, "Global Signaling for Large Scale RSFQ Circuits," *Proceedings of the Government Microcircuit Applications & Critical Technology Conference*, March 2019.

- G. Krylov and E. G. Friedman, "Behavioral Verilog-A Model of Superconductor-Ferromagnetic Transistor," Proceedings of the IEEE International Symposium on Circuits and Systems, May 2018.

- 8. **G. Krylov** and E. G. Friedman, "Test Point Insertion for RSFQ Circuits," *Proceedings of the IEEE International Symposium on Circuits and Systems*, pp. 2022–2025, May 2017.

### Acknowledgments

Graduate school has been a long and transformative journey for me, and many people helped me along the way. I am grateful to everyone who supported me during this time.

First of all, I would like to thank my academic advisor and mentor, Professor Eby G. Friedman, for the enormous amount of professional and personal guidance he has given me over these years. Your continuous support and enthusiasm provides an excellent environment for doctoral study, while the scope and effect of your mentoring extends far beyond academic matters.

I would like to thank my dissertation and defense committee – Professor Mark Bocko, Professor Roman Sobolewski, Professor Selçuk Köse, Professor Yonathan Shapir, Doctor Stephen Whiteley, and Professor Sreepathi Pai. Your comments, critical corrections, and insight helped improve this work.

I am grateful to Dr. Oleg Mukhanov of Hypres Inc. and Jamil Kawa of Synopsys Inc. for giving me fantastic internship opportunities, as well as for their insightful comments and technical guidance.

Over these years I have been surrounded by my outstanding collegaues of the High Performance VLSI/IC Design and Analysis Laboratory – Prof. Inna Vaisband, Dr. Ravi Patel, Dr. Alexander Shapiro, Dr. Mohammad Kazemi, Dr. Ange Maurice, Prof. Boris Vaisband, Dr. Albert Ciprut, Dr. Kan Xu, Douglas McIlrath, Abd-Elrahman Quotb, Rassul Bairamkulov, Tahereh Jabbari, Nurzhan Zhuldassov, and Ana Mitrovic. Thank you for your support, guidance, and company. I greatly enjoyed our conversations and the time we spent together. Special thanks to RuthAnn Williams, for her support with administrative tasks, interesting conversations, and alternative perspectives.

I am grateful to my friends – Alexey Kashkin, Michael Pyzhov, and Dmitry Utyamishev, for their patience and moral support.

I thank my mother Marina, who tirelessly supported and encouraged me in all my efforts, and whose wise advice I should heed more often.

I thank my wife Anastasia, for always being by my side, and for the countless precious moments we shared.

### Abstract

Rapid single flux quantum (RSFQ), the most widely adopted type of superconductive digital logic, is a beyond-CMOS technology particularly appropriate for large scale, efficient, stationary computing such as supercomputers and data centers. The fabrication capabilities of modern superconductive foundries currently approach a million logic gates per IC; the complexity of practical systems, however, does not currently exceed several thousand gates. This "design gap" exists due to the lack of efficient computer aided design tools; in particular, methodologies aware of the issues inherent to very large scale integrated (VLSI) superconductive circuits.

In this dissertation, issues and solutions to enable VLSI RSFQ circuits and systems are presented. Topics such as memory, synchronization, bias networks, and testability are described, and models, circuits, algorithms, and design methodologies are proposed.

A simplified compact model of a superconductor-ferromagnetic transistor (SFT) is developed, to enable simulation and analysis of SFT-based memory circuits. A

sense amplifier topology is also presented to read memory cells composed of magnetic tunnel junctions and nanocryotrons, providing a flexible and area efficient solution for reading spin-based memory. A globally asynchronous, locally synchronous clocking scheme and a network-on-chip topology are described, where the ambiguity of clock and data in RSFQ technology is exploited. Moreover, asynchronous dynamic SFQ (DSFQ) majority gates are also proposed. The use of asynchronous logic gates simplifies the clock network, while majority gates reduce the logic depth, enhancing performance. Synthesis optimization techniques to increase the performance of DSFQ circuits are presented. A methodology for the distributed placement of bias structures in large scale energy efficient RSFQ circuits is proposed, enabling precise control of the parasitic inductances within a bias network while also reducing area and power. A methodology for partitioning RSFQ circuits during the placement process is also described to enable current recycling and reduce the total current, complexity, and inductive noise coupling in the bias network. Sources of parasitic inductive coupling in superconductive circuits are characterized and mitigation solutions are proposed. Test point insertion and set/scan chain techniques compatible with RSFQ logic are proposed, and circuit techniques to reduce the area required by these test structures are described.

### Contributors and Funding Sources

This work was supervised by a dissertation committee consisting of Professor Eby G. Friedman (advisor), Professor Mark Bocko, Professor Selçuk Köse of the Department of Electrical and Computer Engineering, Professor Yonathan Shapir of the Department of Physics and Astronomy, Dr. Stephen Whiteley of Synopsys Inc., and Professor Sreepathi Pai of the Department of Computer Science (committee chairman). All of the work described in the dissertation was completed independently by the student.

This research is supported in part by the Department of Defense Agency – Intelligence Advanced Research Projects Activity through the U.S. Army Research

Office under Contract Nos. W911NF-14-C0089 and W911NF-17-9-0001, by the National Science Foundation under Grant Nos. CCF-1329374, CCF-1526466, and CCF-1716091, AIM Photonics under Award No. 059447-007, the Intel Collaborative Research Institute for Computational Intelligence, Singapore Ministry of Education under Grant Nos. MOE2014-T2-2-105 and MOE2019-T2-2-075, and by grants from Cisco Systems, OeC, Qualcomm, Synopsys, and Google.

The content of the information does not necessarily reflect the position or the policy of the U.S. Government, and no official endorsement should be inferred.

# List of Tables

| 2.1  | Superconductive materials commonly used in electronics             | 44  |

|------|--------------------------------------------------------------------|-----|

| 9.1  | Comparison of mutual inductance extracted in FastHenry with exper- |     |

|      | imental data. The experimental data and layout topology are based  |     |

|      | on [340]                                                           | 218 |

| 11.1 | Comparison of different logic types for (11.1)                     | 258 |

| 13.1 | Results of FM partitioning on modified ISCAS'89 benchmark circuits |     |

|      | and the AMD2901 ALU                                                | 300 |

| 13.2 | Results of geometric partitioning on modified ISCAS'89 benchmark   |     |

|      | circuits and the AMD2901 ALU                                       | 304 |

| 14.1 | Characteristics of ISCAS'85 benchmark circuits mapped to RSFQ cell |     |

|      | library with path balancing                                        | 317 |

| 14.2 | Characteristics of ISCAS'85 benchmark circuits mapped to a DSFQ |     |

|------|-----------------------------------------------------------------|-----|

|      | cell library with and without splitters                         | 319 |

| 14.3 | Characteristics of ISCAS'85 benchmark circuits mapped to a DSFQ |     |

|      | library with full path balancing                                | 323 |

| 16.1 | Number of junctions per function [23], see (16.1) to (16.6)     | 364 |

# List of Figures

| 1.1 | New York Times newspaper article from February 6, 1957 [7] foreshad-                           |    |

|-----|------------------------------------------------------------------------------------------------|----|

|     | owing cubic foot sized computers. Ubiquitous at the time, the vacuum                           |    |

|     | tube (top) is shown next to an early transistor (left), and cryotron                           |    |

|     | $(right). \ \ldots \ $ | 9  |

| 1.2 | Photograph of the ETL-JC1 computer [20]. Several superconductive                               |    |

|     | ICs form a multi-chip module                                                                   | 6  |

| 1.3 | Computing systems classified by total power consumption and approx-                            |    |

|     | imate time of development. All of these computing applications are in                          |    |

|     | common use today                                                                               | Ć  |

| 1.4 | Evolution of remote access in computing systems                                                | 10 |

| 1.5 | Delay (performance) and power (energy dissipation) per operation for                           |    |

|     | CMOS and SCE technologies [40], [41]                                                           | 18 |

| 1.6 | Large scale, layered cryogenic computing system [33], [39],                                    | 10 |

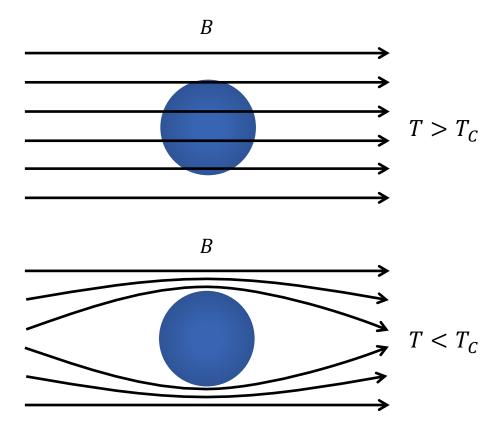

| 2.1  | Meissner effect. Magnetic field lines are expelled from the supercon-                   |    |

|------|-----------------------------------------------------------------------------------------|----|

|      | ductive material [62]                                                                   | 35 |

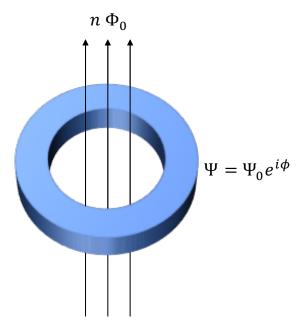

| 2.2  | Quantization of magnetic flux                                                           | 37 |

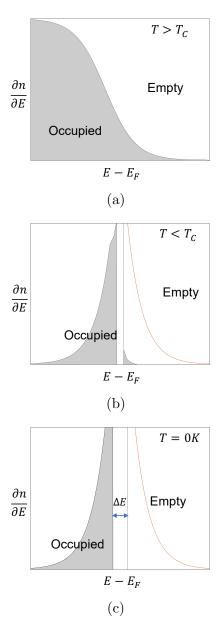

| 2.3  | Density of states in a superconductor for different temperatures; (a)                   |    |

|      | $T > T_C$ , (b) $T < T_C$ , and (c) $T = 0$ K. The energy gap $\Delta E$ is the         |    |

|      | empty space around the Fermi level $E_F$                                                | 39 |

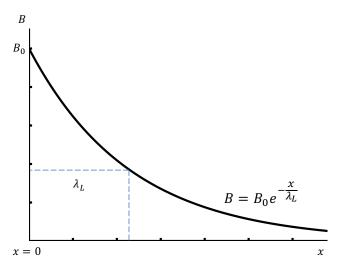

| 2.4  | Magnetic field inside a bulk superconductor. $\lambda_L$ is the London pene-            |    |

|      | tration depth                                                                           | 41 |

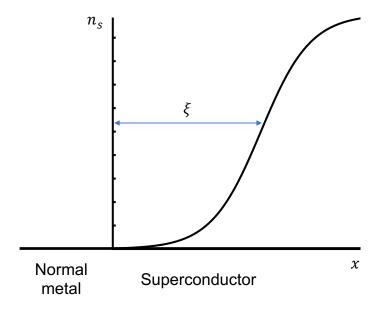

| 2.5  | Density of superconductive electrons at the boundary of a supercon-                     |    |

|      | ductive region. The coherence length is $\xi$                                           | 43 |

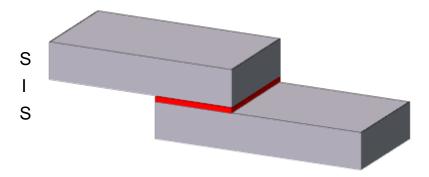

| 2.6  | Thin film Josephson junction. ${\cal I}$ denotes an insulating material, and ${\cal S}$ |    |

|      | is a superconductive material                                                           | 49 |

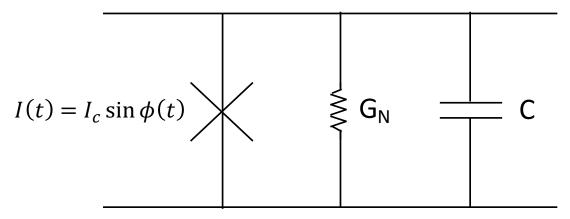

| 2.7  | Equivalent circuit of the RCSJ model of a JJ                                            | 54 |

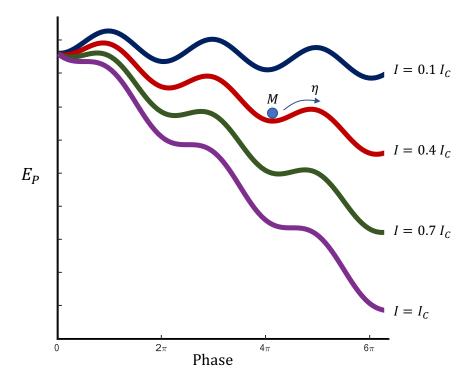

| 2.8  | Analogy of tilted washboard potential illustrating the dynamics of a                    |    |

|      | JJ. Different curves correspond to different bias currents as compared                  |    |

|      | to the critical current $I_C$                                                           | 56 |

| 2.9  | Analogy of mechanical pendulum illustrating the dynamics of a JJ.   .                   | 57 |

| 2.10 | Current-voltage characteristics of a JJ, a) overdamped, and b) under-                   |    |

|      | damped                                                                                  | 59 |

| 2.11 | Typical structure of a superconductive nanowire single photon detector                  |     |

|------|-----------------------------------------------------------------------------------------|-----|

|      | [80]                                                                                    | 61  |

| 2.12 | Cryotron                                                                                | 62  |

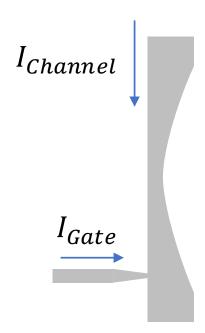

| 2.13 | Nanocryotron (nTron)                                                                    | 62  |

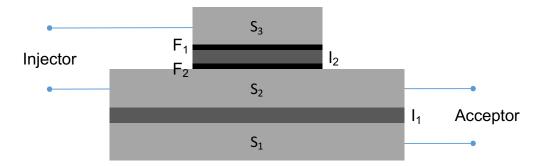

| 2.14 | Structure of a three terminal SFT device. The superconductor layers                     |     |

|      | are marked as $S_1$ , $S_2$ , and $S_3$ , ferromagnetic layers as $F_1$ and $F_2$ , and |     |

|      | insulator layers as $I_1$ and $I_2$                                                     | 64  |

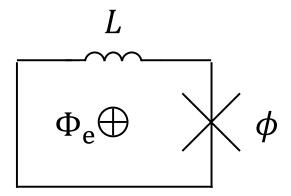

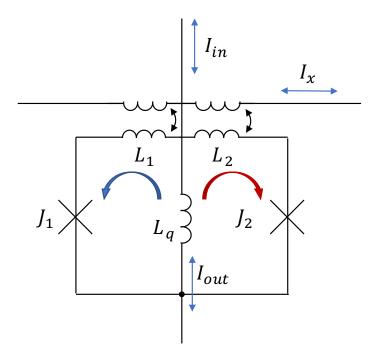

| 3.1  | RF SQUID                                                                                | 70  |

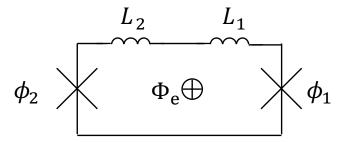

| 3.2  | Two junction SQUID                                                                      | 73  |

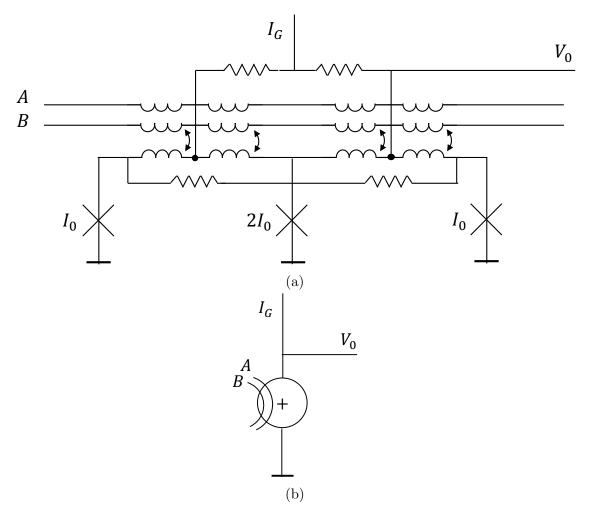

| 3.3  | Voltage level OR gate [100], (a) circuit schematic, and (b) logic symbol.               | 75  |

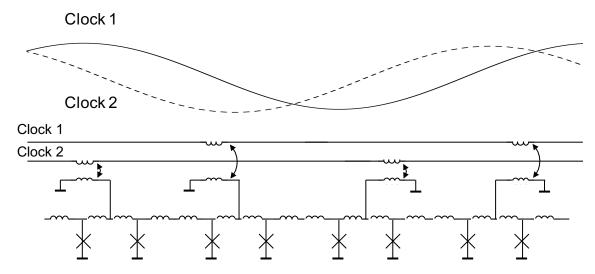

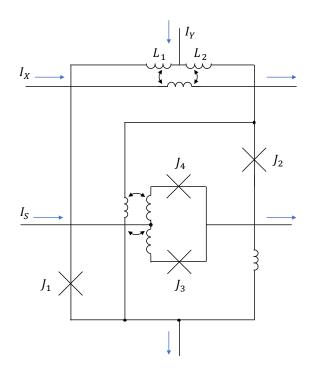

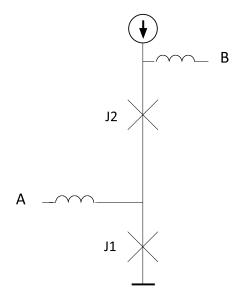

| 3.4  | Basic RSFQ circuit – transmission line                                                  | 78  |

| 3.5  | Reciprocal quantum logic transmission line [106]                                        | 80  |

| 3.6  | RQL transmission line with a typical clock/bias topology [107]                          | 81  |

| 3.7  | Quantum flux parametron device [24]                                                     | 84  |

| 3.8  | Vortex transitional memory cell [110]                                                   | 87  |

| 3.9  | Suzuki stack [124]                                                                      | 89  |

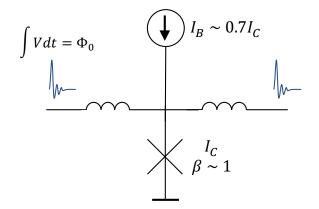

| 4.1  | Josephson transmission line                                                             | 95  |

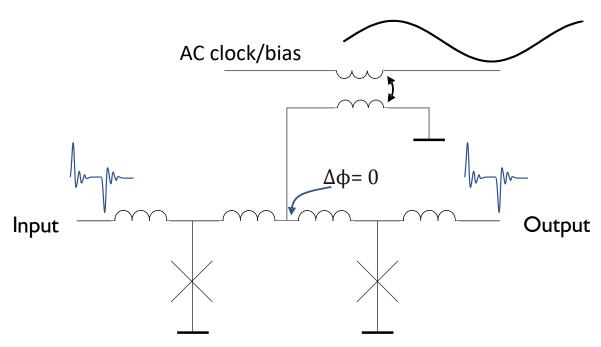

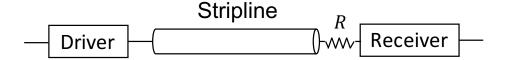

| 4.2  | Passive transmission line for SFQ signals                                               | 98  |

| 4.3  | RSFQ D flip flop                                                                        | 100 |

| 4.4  | Basic RSFQ storage loop                                                                 | 101 |

| 4.5  | RSFQ balanced comparator (decision making pair)                           | 102 |

|------|---------------------------------------------------------------------------|-----|

| 4.6  | RSFQ buffer                                                               | 103 |

| 4.7  | RSFQ splitter                                                             | 105 |

| 4.8  | RSFQ binary splitter tree                                                 | 105 |

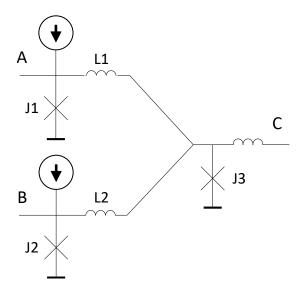

| 4.9  | RSFQ confluence buffer                                                    | 107 |

| 4.10 | RSFQ OR (AND) gate                                                        | 108 |

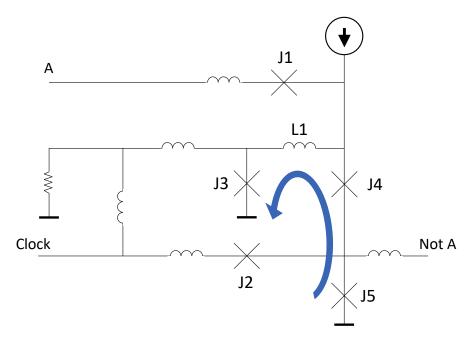

| 4.11 | RSFQ inverter. Arrow denotes the SFQ storage loop                         | 109 |

| 4.12 | RSFQ Muller C element                                                     | 110 |

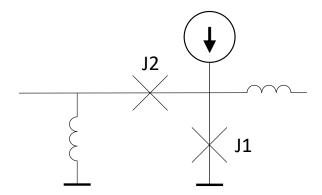

| 4.13 | DC-to-SFQ converter                                                       | 111 |

| 4.14 | SFQ-to-DC converter                                                       | 112 |

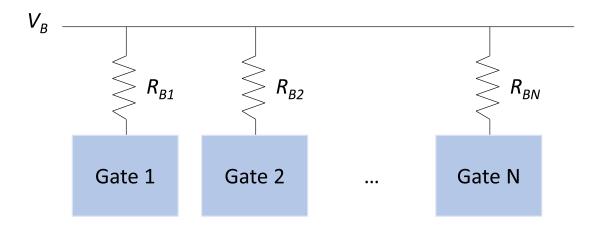

| 4.15 | Bias current distribution in conventional RSFQ circuits                   | 114 |

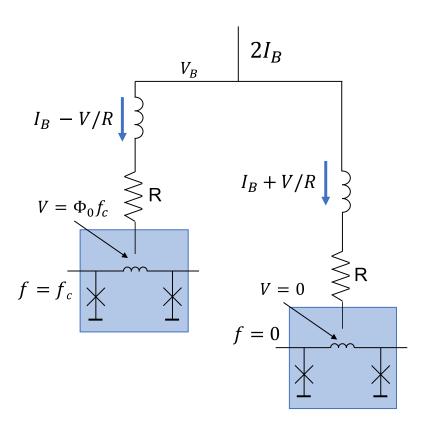

| 4.16 | Data dependent redistribution of bias current in RSFQ circuits [154].     | 116 |

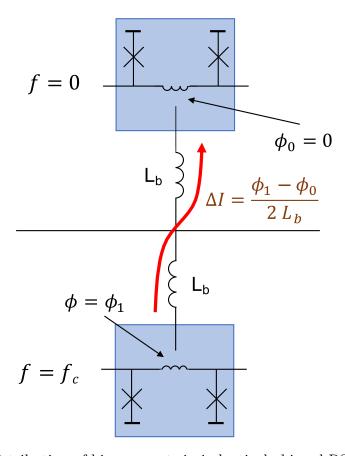

| 4.17 | Redistribution of bias currents in inductively biased RSFQ circuits [33]. | 118 |

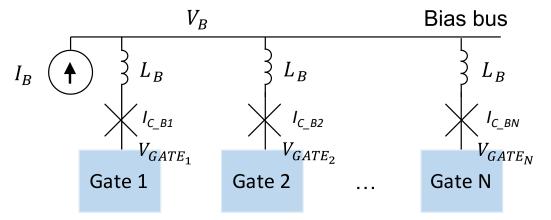

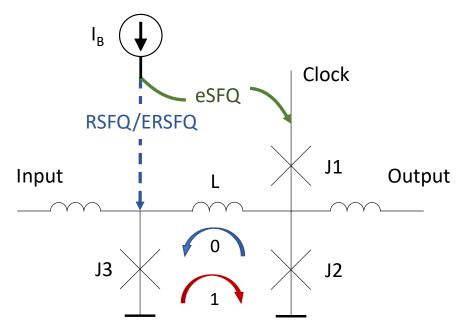

| 4.18 | Bias distribution in ERSFQ circuits                                       | 121 |

| 4.19 | Feeding JTL connected to an SFQ clock line acting as a voltage reference. | 122 |

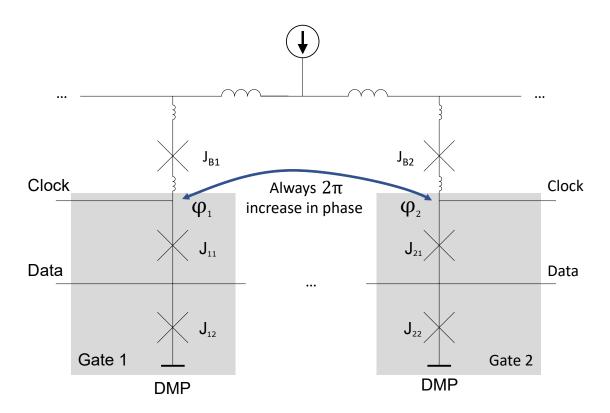

| 4.20 | Phase balance across different decision making pairs [165]                | 124 |

| 4.21 | Conversion of regular RSFQ DFF into an eSFQ DFF [165]                     | 125 |

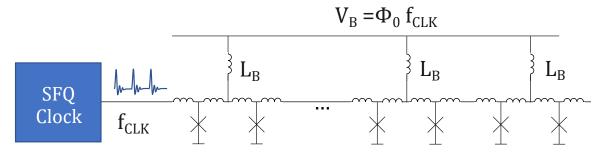

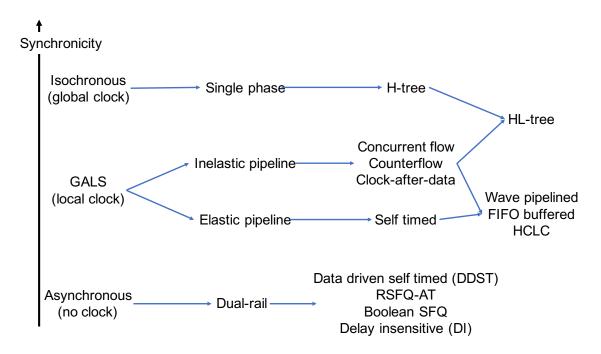

| 5.1  | Clocking approaches for RSFQ circuits [166]                               | 128 |

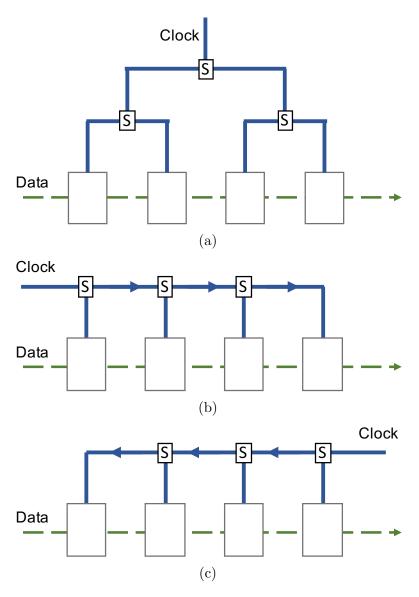

| 5.2 | Synchronous clocking schemes for RSFQ circuits, (a) H-tree, (b) con-                    |     |

|-----|-----------------------------------------------------------------------------------------|-----|

|     | current flow, and (c) counterflow. The letter "S" denotes an RSFQ                       |     |

|     | splitter                                                                                | 130 |

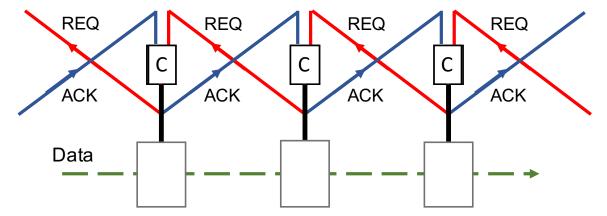

| 5.3 | Handshaking mechanism based on C elements                                               | 137 |

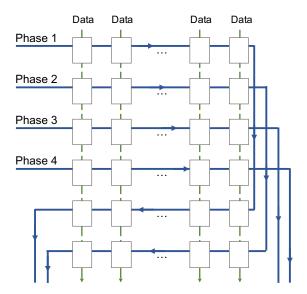

| 5.4 | Meander topology for the clock distribution network in AQFP circuits                    |     |

|     | [203]                                                                                   | 141 |

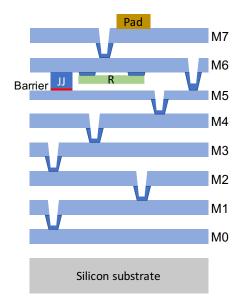

| 6.1 | Simplified layer stack in modern SCE circuits based on the MIT LL                       |     |

|     | SFQ5ee process. The white areas are filled with inter-layer dielectric.                 | 147 |

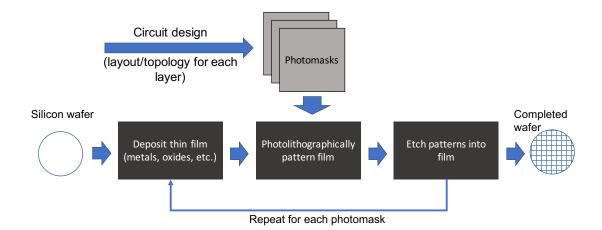

| 6.2 | Simplified flowchart highlighting the primary steps of an SCE fabrica-                  |     |

|     | tion process [211]                                                                      | 148 |

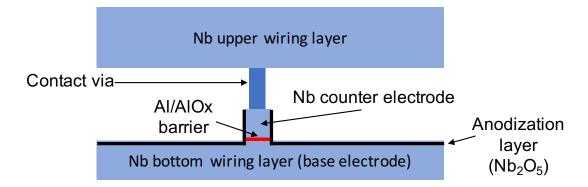

| 6.3 | Cross section of a thin film $\mathrm{Nb/Al/AlO}_x/\mathrm{Nb}$ Josephson junction. The |     |

|     | space in the middle is filled with silicon dioxide                                      | 154 |

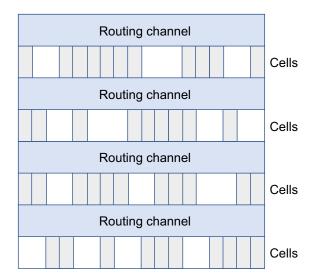

| 7.1 | Row-based standard cell placement methodology with channel routing.                     | 162 |

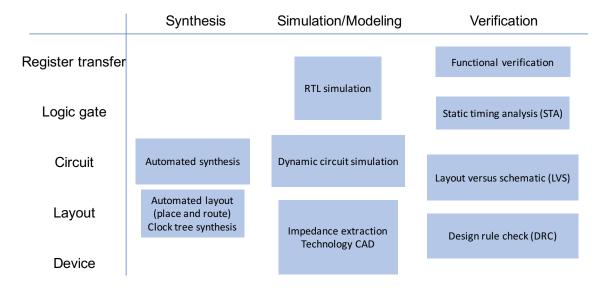

| 7.2 | EDA flow for integrated circuits                                                        | 163 |

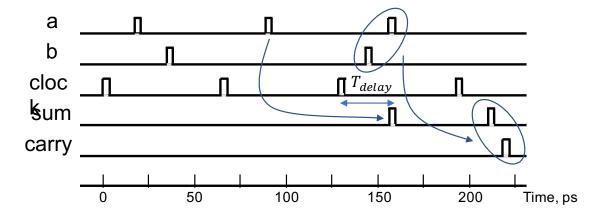

| 7.3 | HDL simulation of an RSFQ half adder [251]                                              | 171 |

| 7.4 | Circuit simulation of a two stage JTL. The voltages across the input                    |     |

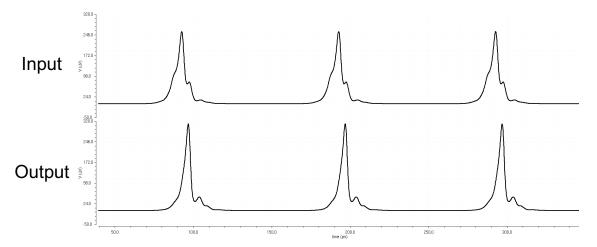

|     | and output JJs are shown                                                                | 176 |

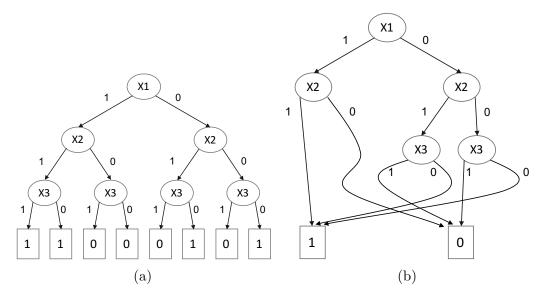

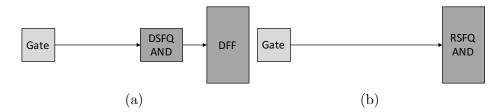

| 7.5 | Graph representations of a circuit used in the synthesis process, (a)                   |     |

|     | binary decision tree, and (b) binary decision diagram (BDD)                             | 181 |

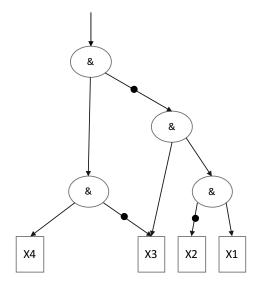

| 7.6         | And-Inverter graph (AIG). The black dots on the edges denote the        |     |

|-------------|-------------------------------------------------------------------------|-----|

|             | inversion operation                                                     | 182 |

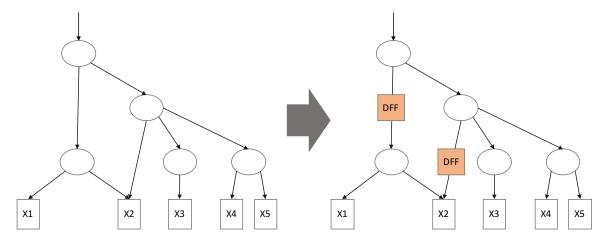

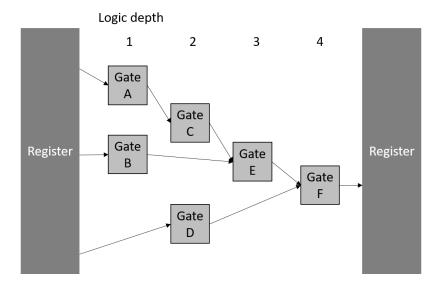

| 7.7         | Insertion of path balancing D flip flops into RSFQ logic paths          | 184 |

| 7.8         | Retiming of a logic path with path balancing DFFs                       | 185 |

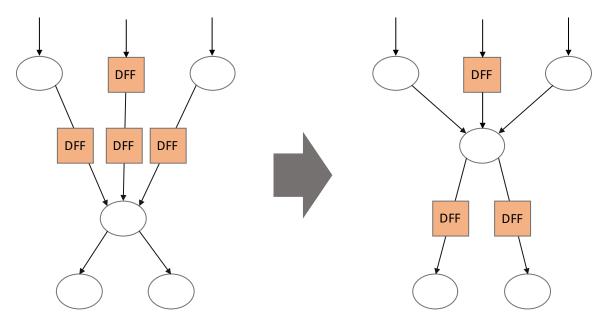

| 7.9         | Pulse timing based on a phase change of a JJ. The voltage and phase     |     |

|             | across a JJ are shown during switching. The dashed horizontal line      |     |

|             | denotes a $75\%$ increase in the phase of the JJ                        | 191 |

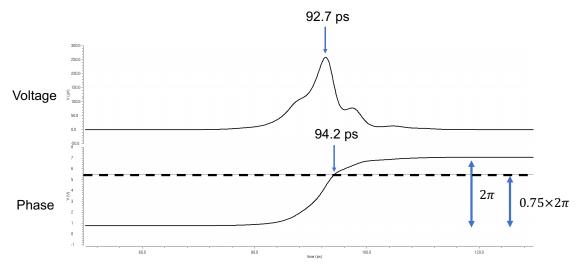

| 7.10        | Critical timing constraints in RSFQ circuits, (a) setup time, (b) hold  |     |

|             | time, and (c) separation time                                           | 193 |

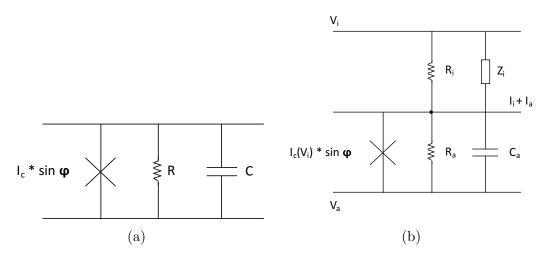

| 8.1         | Equivalent electrical circuit, a) RCSJ model of Josephson junction, and |     |

|             | b) model of a SFIFSIS device                                            | 203 |

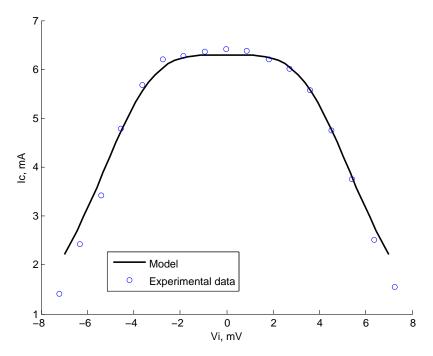

| 8.2         | $I_c - V_i$ characteristic of the proposed model. The experimental data |     |

|             | are shown as circles.                                                   | 208 |

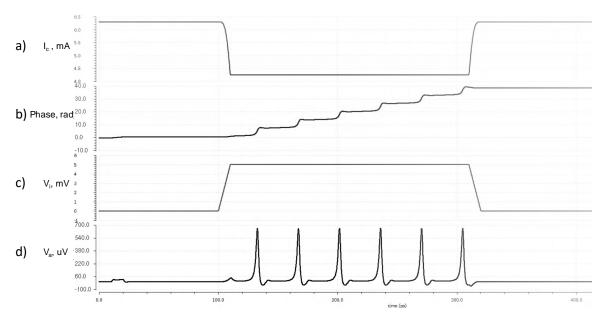

| 8.3         | Transient response of an SFT device based on the proposed model, a)     |     |

|             | critical current of the acceptor, b) phase of the acceptor, c) injector |     |

|             | voltage, and d) acceptor voltage                                        | 210 |

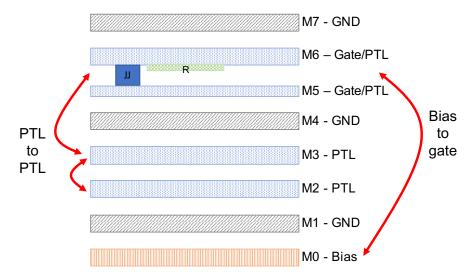

| 9.1         | Sources of inductive coupling noise in a superconductive IC (based on   |     |

| 0.1         | MIT LL SFQ5ee process)                                                  | 213 |

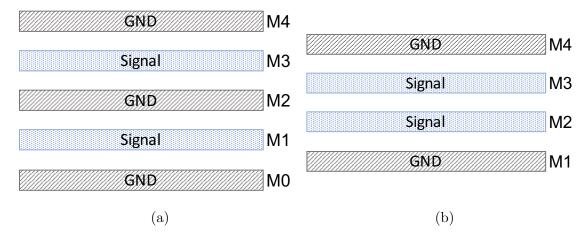

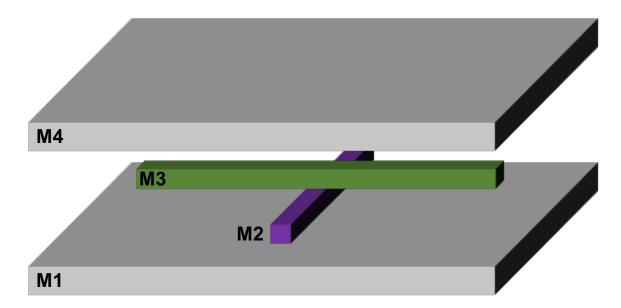

| 9.2         | Topologies to allocate metal layers for two PTL routing strategies, (a) | 210 |

| J. <u>L</u> |                                                                         | 915 |

|             | three ground planes [339], and (b) two ground planes [246]              | 215 |

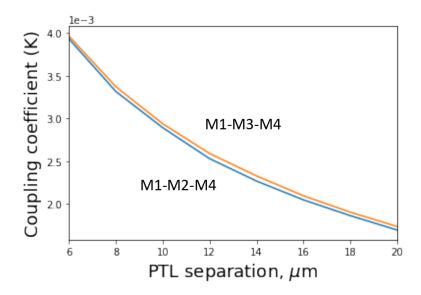

| 9.3  | Coupling between two identical parallel PTLs within the same layers      |     |

|------|--------------------------------------------------------------------------|-----|

|      | with signal lines in M2 and M3                                           | 219 |

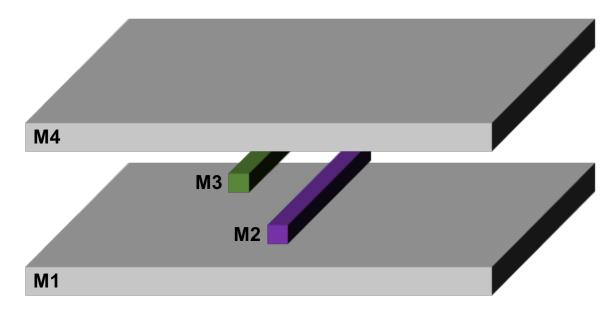

| 9.4  | Two identical parallel PTLs in adjacent layers with signal lines in M2   |     |

|      | and M3                                                                   | 220 |

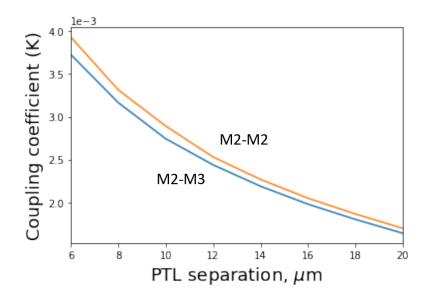

| 9.5  | Coupling between two identical parallel PTLs in adjacent layers with     |     |

|      | signal lines in M2 and M3                                                | 220 |

| 9.6  | Two perpendicular PTLs in adjacent layers with signal lines in $M2$ and  |     |

|      | M3                                                                       | 221 |

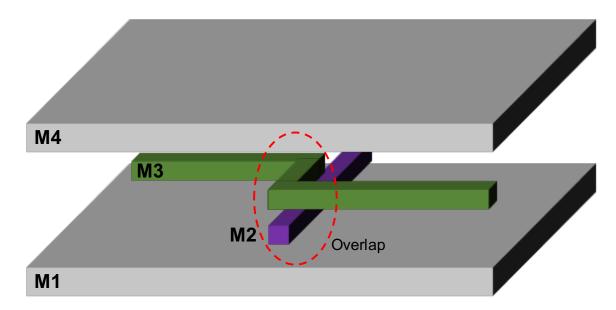

| 9.7  | Two perpendicular PTLs in adjacent layers with signal lines in $M2$ and  |     |

|      | M3 with a short overlap                                                  | 222 |

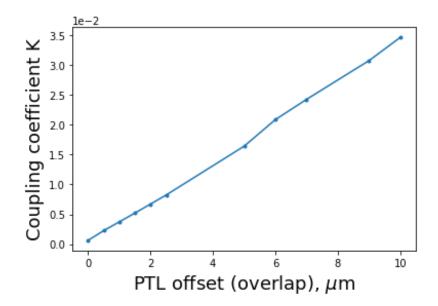

| 9.8  | Coupling between two perpendicular PTLs in adjacent layers with sig-     |     |

|      | nal lines in M2 and M3 with a short overlap (see Figure 9.7)             | 223 |

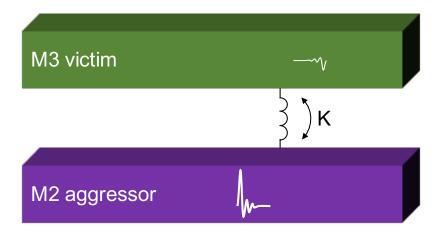

| 9.9  | Inductive coupling between parallel PTLs showing the aggressor and       |     |

|      | victim lines                                                             | 225 |

| 9.10 | Effects of bias coupling from the M0 bias line on current distribution   |     |

|      | within a DFF in M5-M6. $I_{BL}$ is the current carried by the bias line. |     |

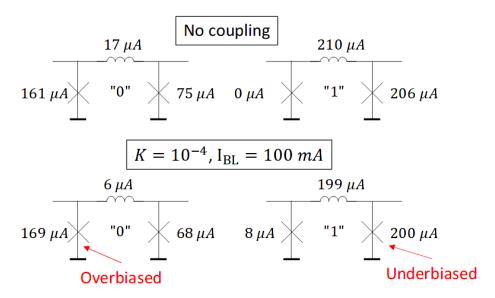

|      | The stored state is shown in the middle of the storage loop              | 226 |

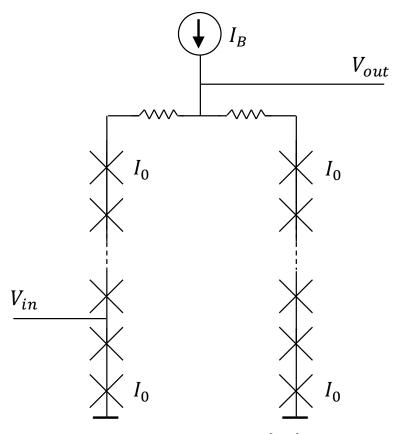

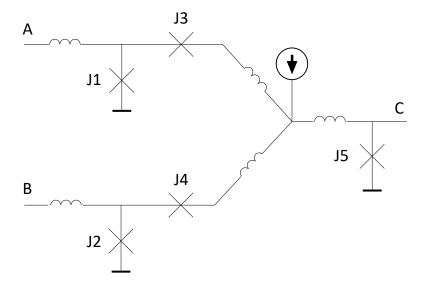

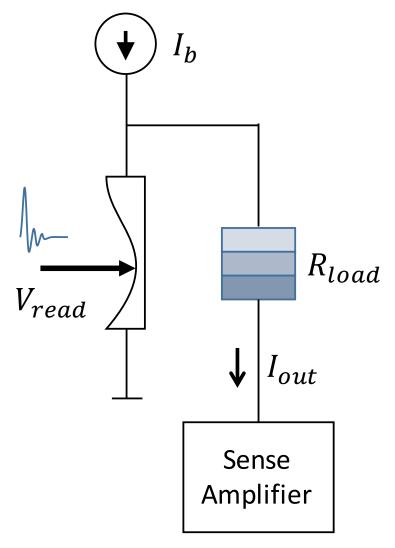

| 10.1 | Memory cell readout circuit. $V_{read}$ is the read enable SFQ pulse, $I_b$ is             |     |

|------|--------------------------------------------------------------------------------------------|-----|

|      | the bias current for the readout circuit, $R_{load}$ is a spin valve element               |     |

|      | exhibiting a variable resistance, and $I_{out}$ is the output current of the               |     |

|      | readout circuit                                                                            | 231 |

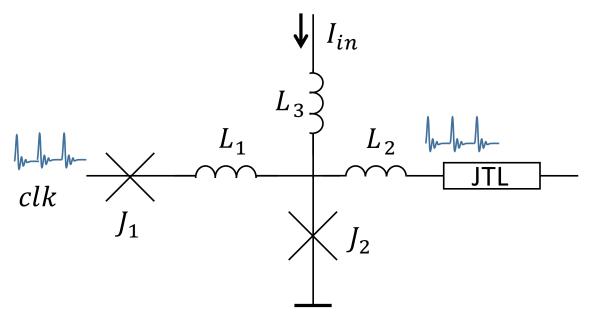

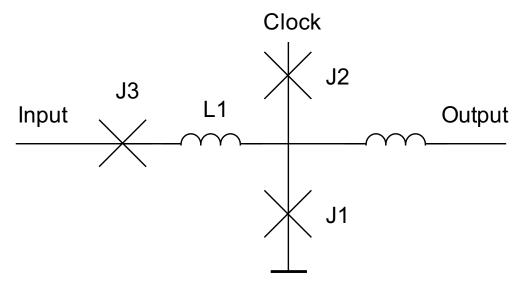

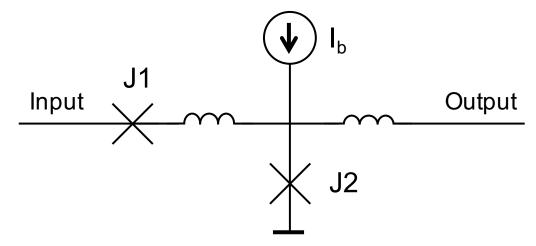

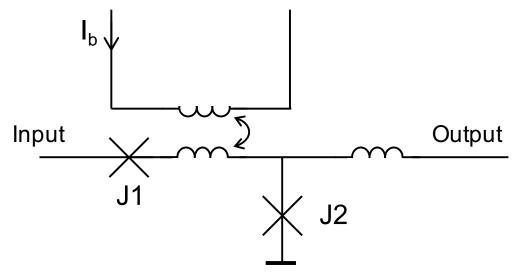

| 10.2 | Clocked DC-to-SFQ converter. $J_1$ and $J_2$ make up the decision making                   |     |

|      | pair of Josephson junctions. The SFQ clock signal passes through the                       |     |

|      | circuit and is modulated by the input current $I_{in}$ , which functions as                |     |

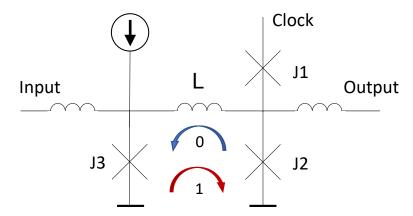

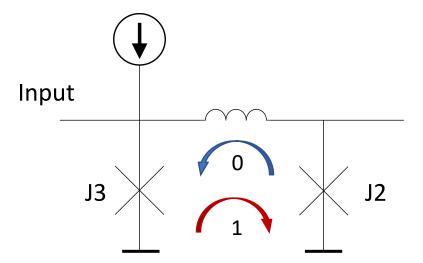

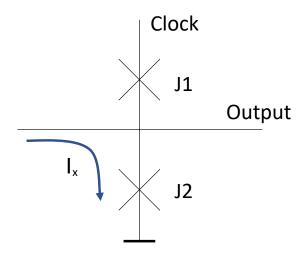

|      | a bias current for $J_2$                                                                   | 232 |

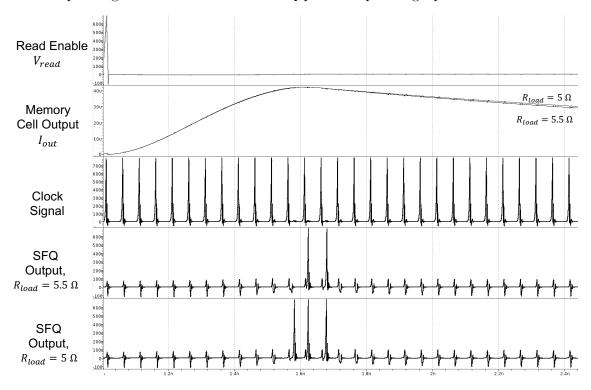

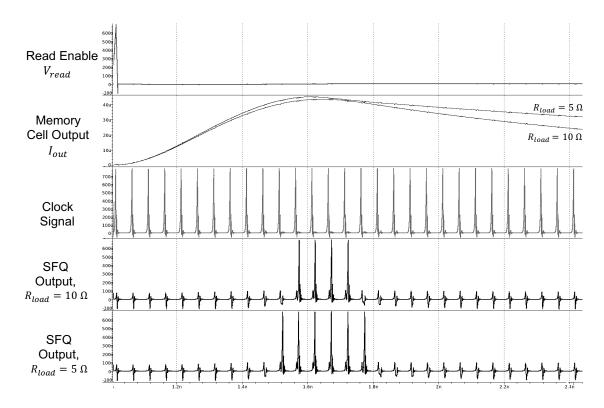

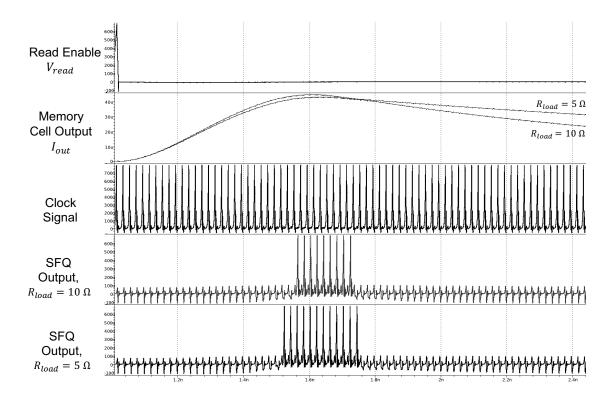

| 10.3 | Low MR waveforms. The clock frequency is 20 GHz. $R_{load}$ is 5 $\Omega$ to               |     |

|      | 5.5 $\Omega$ . The bias current is 74 $\mu$ A. The sense amplifier output is two to        |     |

|      | three SFQ pulses                                                                           | 237 |

| 10.4 | High MR waveforms. The clock frequency is 20 GHz. $R_{load}$ is 5 $\Omega$ to              |     |

|      | 10 $\Omega$ . The bias current is 76.6 $\mu A$ . The sense amplifier output is four        |     |

|      | to six SFQ pulses                                                                          | 238 |

| 10.5 | High MR and high frequency waveforms. The clock frequency is 50                            |     |

|      | GHz. $R_{load}$ is 5 $\Omega$ to 10 $\Omega$ . The bias current is 76.6 $\mu$ A. The sense |     |

|      | amplifier output is nine to twelve SFQ pulses                                              | 239 |

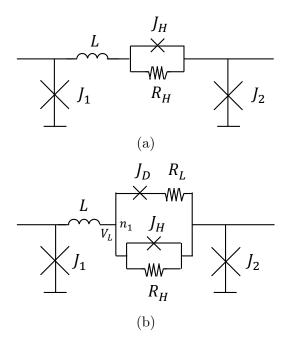

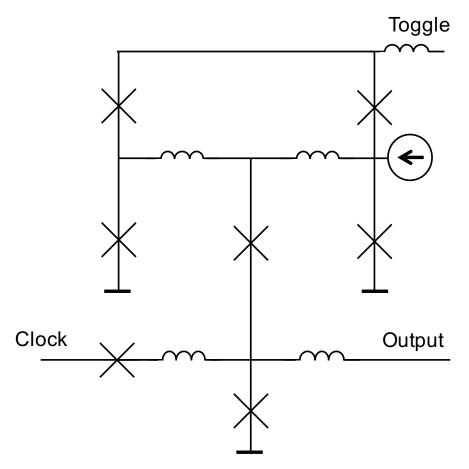

| 11.1 | Dynamic SFQ storage loops, a) traditional dynamic loop, and b) novel                       |     |

|      | dynamic loop introduced in [187]                                                           | 244 |

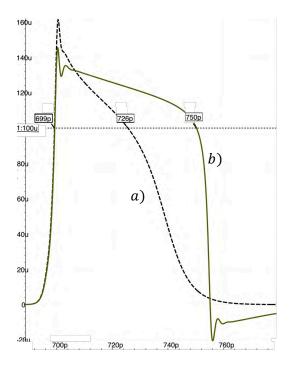

| 11.2  | Loop current a) within a loop with a single time constant (dashed line),                      |     |

|-------|-----------------------------------------------------------------------------------------------|-----|

|       | and b) within a loop with dual time constants (solid line)                                    | 245 |

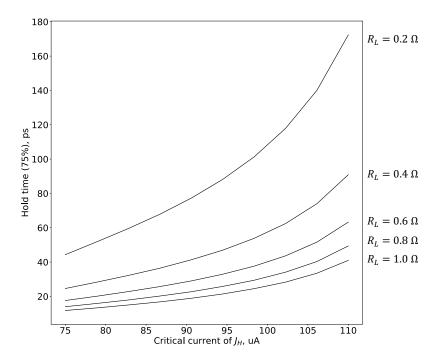

| 11.3  | Dependence of $\tau_H$ on $R_L$ and $I_C(J_H)$                                                | 247 |

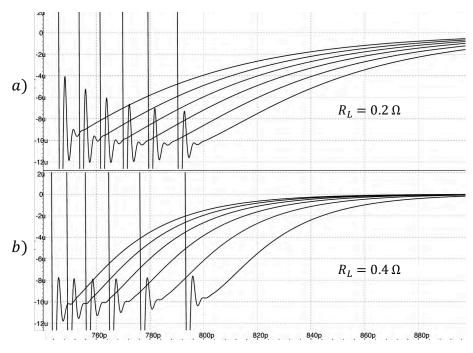

| 11.4  | Dependence of $\tau_R$ on $R_L$ for similar $\tau_H$ ( $\sim 45$ to $\sim 90$ ps), a) $R_L =$ |     |

|       | 0.2 $\Omega$ , and b) $R_L = 0.4 \Omega$                                                      | 247 |

| 11.5  | Timing behavior of $I_C(J_D)$ in DSFQ loops, a) dependence of $\tau_H$ on                     |     |

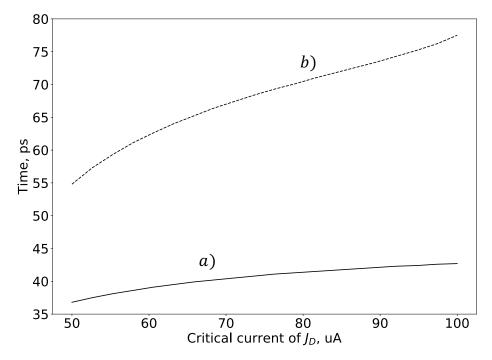

|       | $I_C(J_D)$ (solid line), and b) dependence of $\tau_R$ on $I_C(J_D)$ (dashed line).           | 248 |

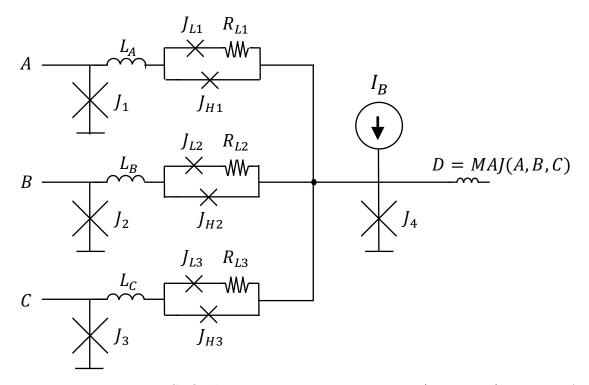

| 11.6  | Dynamic SFQ three input majority gate. $I_C(J1, J2, J3) = 120 \mu A$ ,                        |     |

|       | critically damped. $L1, L2, L3 = 9.5$ pH (the input JJs and part of                           |     |

|       | the inductance are shared with the input JTLs). $I_c(J_{L1}, J_{L2}, J_{L3}) =$               |     |

|       | 50 $\mu$ A, unshunted. $I_c(J_{H1}, J_{H2}, J_{H3}) = 106 \mu$ A, critically damped.          |     |

|       | $R_{L1},R_{L2},R_{L3}=1.4~\Omega.~I_c(J_4)=160~\mu\mathrm{A},$ critically damped. $I_B=$      |     |

|       | 82 μA                                                                                         | 250 |

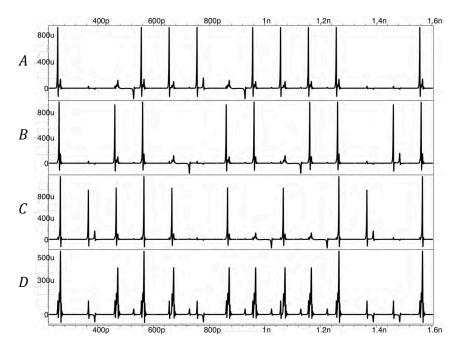

| 11.7  | Operation of the proposed three input majority gate. $A,B,C$ – inputs                         |     |

|       | and $D$ – output                                                                              | 251 |

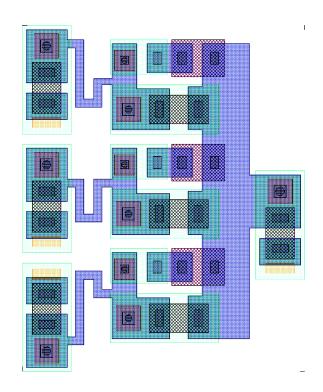

| 11.8  | Layout of a three input majority gate in the Hypres $4.5~\mathrm{kA/cm^2}$ tech-              |     |

|       | nology [210]                                                                                  | 252 |

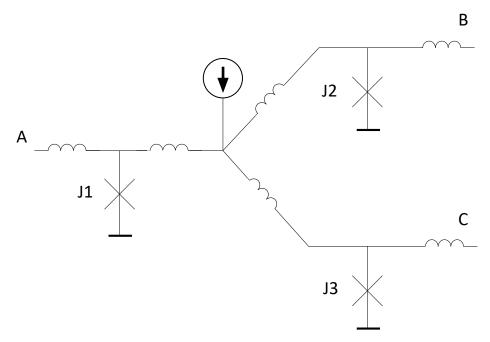

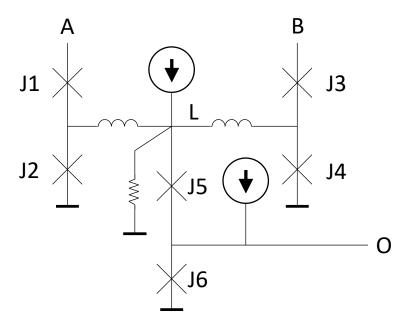

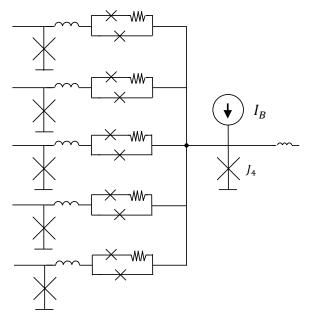

| 11.9  | Dynamic SFQ five input majority gate                                                          | 254 |

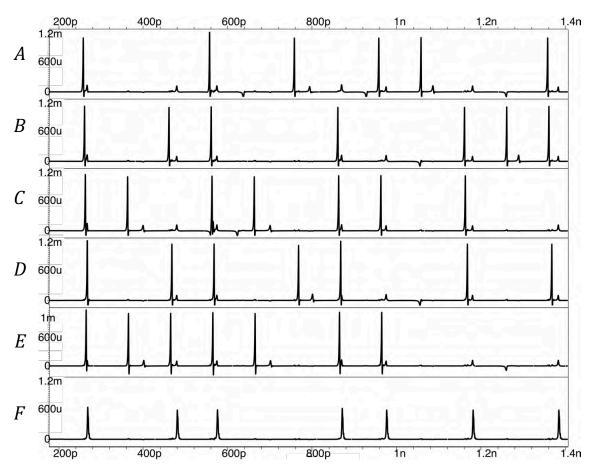

| 11.10 | Operation of the proposed five input majority gate. $A, B, C, D, E$                           |     |

|       | inputs and $F$ – output                                                                       | 255 |

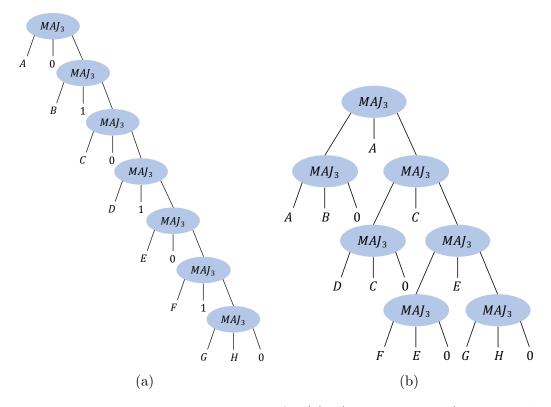

| 11.11 | l Majority-inverter graph for (1), a) original, and b) optimized                      | 256 |

|-------|---------------------------------------------------------------------------------------|-----|

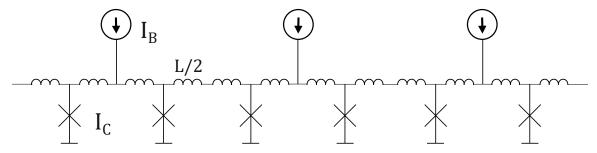

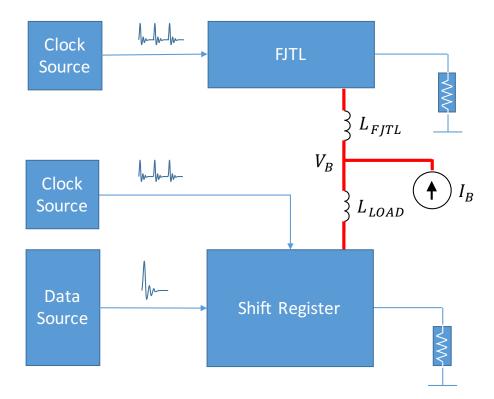

| 12.1  | Example topology of the ERSFQ biased circuit used in this analysis.                   | 265 |

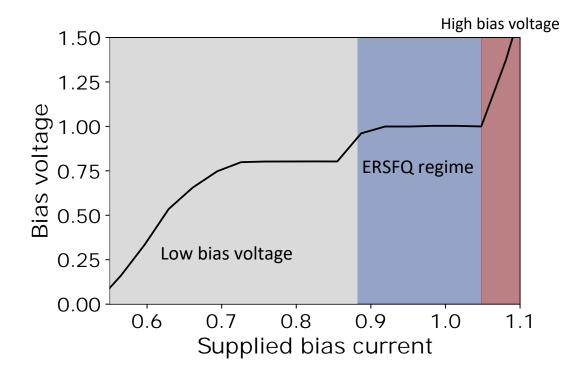

| 12.2  | Regions of operation of ERSFQ system                                                  | 270 |

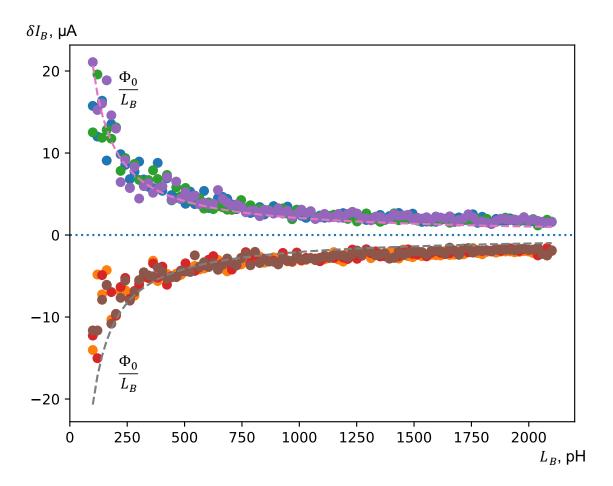

| 12.3  | Dependence of current variations on the bias inductance. The dashed                   |     |

|       | line is the analytic expression                                                       | 273 |

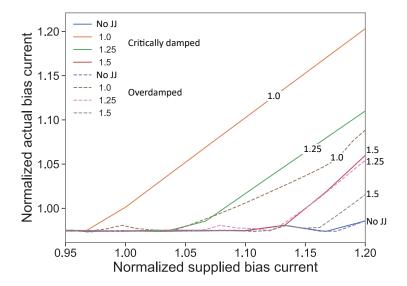

| 12.4  | Dependence of load bias current on supplied bias current for the crit-                |     |

|       | ically damped and overdamped bias JJs within a FJTL. The example                      |     |

|       | FJTL contains 64 stages, corresponding to $50\%$ of the load bias cur-                |     |

|       | rent. The critical current of the bias JJ is normalized to 350 $\mu A$ .              |     |

|       | Three different sizes of bias JJs (standard size, $25\%$ greater size, and            |     |

|       | 50% greater size) are considered, as well as the absence of a bias JJ                 | 275 |

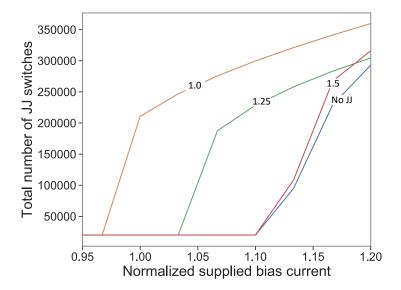

| 12.5  | Dependence of total number of bias JJ switches and FJTL switches on                   |     |

|       | supplied bias current. The critical current of the bias JJ is normalized              |     |

|       | to 350 $\mu\mathrm{A}.$ Three different sizes of bias JJs (standard size, 25% greater |     |

|       | size, and $50\%$ greater size) are considered, as well as the absence of a            |     |

|       | bias JJ                                                                               | 276 |

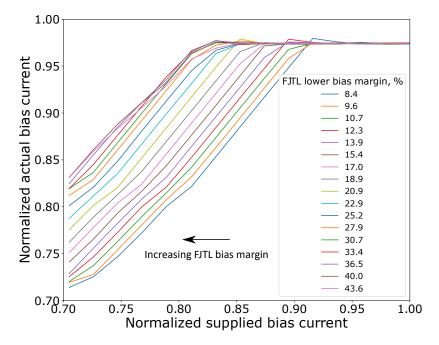

| 12.6  | Dependence of load bias current on supplied bias current for FJTL                     |     |

|       | with the same size and different bias margins $(8.4\% \text{ to } 43.6\%)$            | 277 |

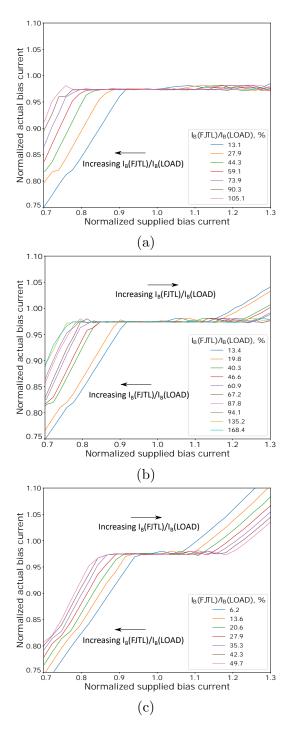

| 12.7 | Dependence of load bias current on the supplied bias current, a) 8 bit                                                                  |      |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|------|

|      | load (21.31 mA), b) 16 bit load (44.27 mA), and c) 32 bit load (90.19                                                                   |      |

|      | $mA). \ \ldots $ | 279  |

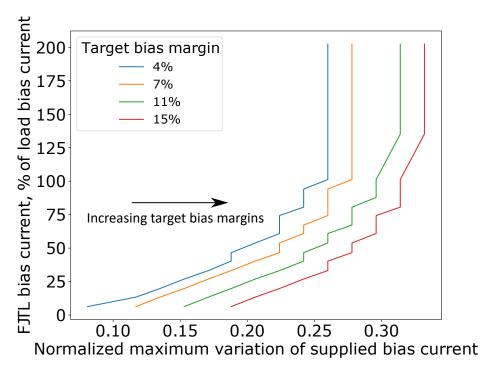

| 12.8 | Dependence of FJTL size on desired bias variations and expected sup-                                                                    |      |

|      | ply variations                                                                                                                          | 280  |

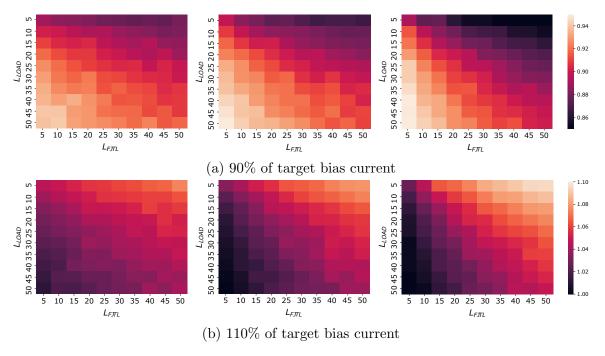

| 12.1 | 1Bias current in the load normalized to the target bias current in the                                                                  |      |

|      | load. The bias current supplied to the system is momentarily changed                                                                    |      |

|      | to a) 90%, and b) $110\%$ of the nominal current. The three different                                                                   |      |

|      | FJTL sizes (bias currents) correspond to, respectively left to right,                                                                   |      |

|      | 12.5%, $25%$ , and $50%$ of the load bias current. The brighter areas                                                                   |      |

|      | represent higher current                                                                                                                | 284  |

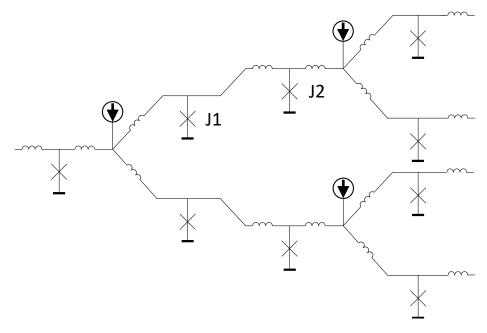

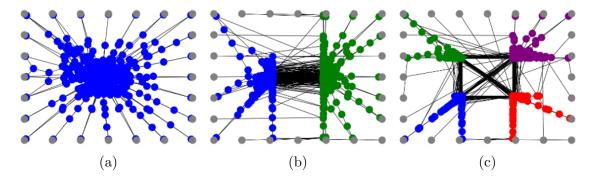

| 13.1 | Coarse placement and partitioning with FM heuristic of a benchmark                                                                      |      |

|      | circuit, (a) initial placement, (b) bipartitioning and placement, and (c)                                                               |      |

|      | four way partitioning and placement. Different shaded circles (nodes)                                                                   |      |

|      | correspond to individual cells in different partitions, while the lines                                                                 |      |

|      | (edges) represent signal connections                                                                                                    | 300  |

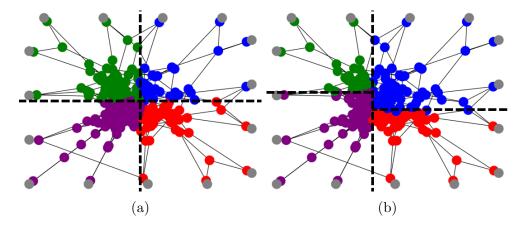

| 13.2 | Coarse placement and geometric partitioning of a benchmark circuit,                                                                     |      |

|      | (a) simple geometric partitioning with equal area, and (b) geometric                                                                    |      |

|      | partitioning with partition boundaries optimized by simulated annealing                                                                 | .305 |

| 14.1 | Pipelined logic path                                                                                                                    | 309  |

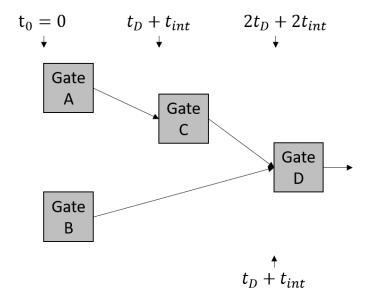

| 14.2 | Delay imbalance in DSFQ logic path. The pulse arrival time for the               |     |

|------|----------------------------------------------------------------------------------|-----|

|      | gates is highlighted. $t_D$ and $t_{int}$ are, respectively, the gate and inter- |     |

|      | connect delays                                                                   | 312 |

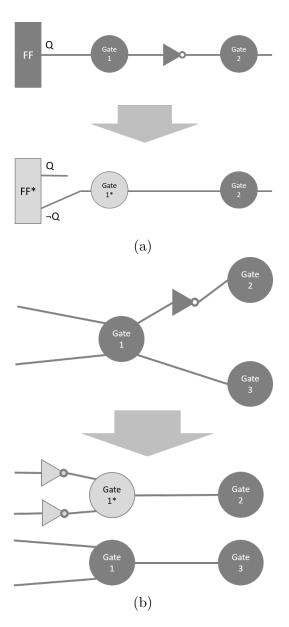

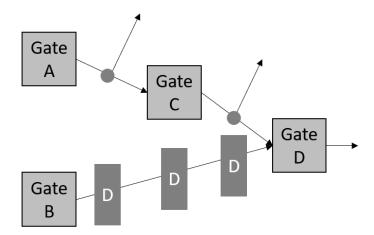

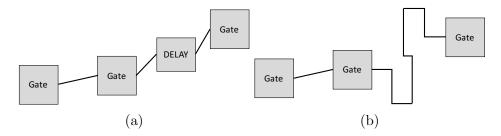

| 14.3 | Inverter propagation process, a) at edge of the pipeline stage, and b)           |     |

|      | complicated by the presence of splitters. The unchanged gates are                |     |

|      | depicted in the darker shading                                                   | 315 |

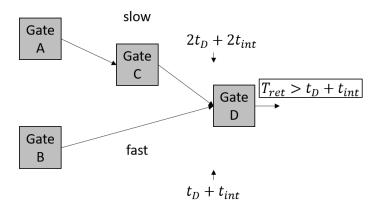

| 14.4 | Delay imbalance in DSFQ logic path. Faster and slower signal paths               |     |

|      | are highlighted. The circuit operates correctly if the retention time is         |     |

|      | sufficient                                                                       | 318 |

| 14.5 | DSFQ pipelined signal path supporting multiple data waves                        | 321 |

| 14.6 | Full path balancing in DSFQ circuits. The difference in path delays              |     |

|      | related to the gates and splitters (shown as circles) in the slower (top)        |     |

|      | path, is balanced in the faster (bottom) path by delay elements ${\bf D}.$ .     | 322 |

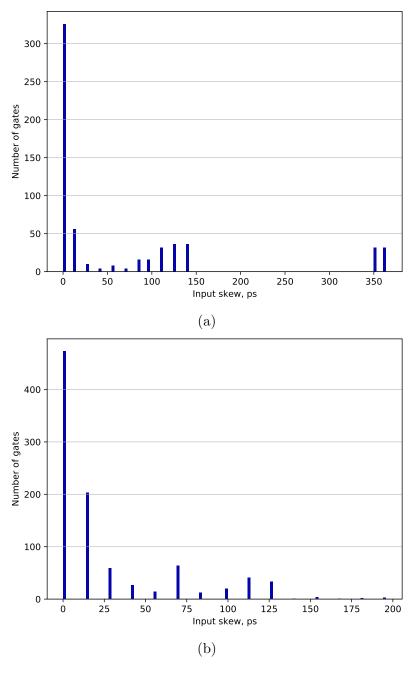

| 14.7 | Statistical distribution of input skews for DSFQ ISCAS'85 benchmark              |     |

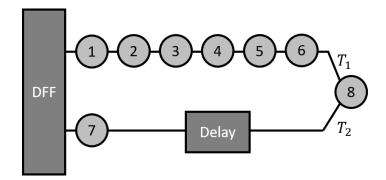

|      | circuits, a) c1355, and b) c2670                                                 | 324 |

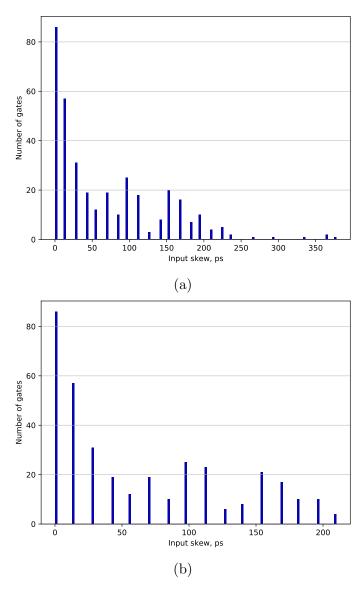

| 14.8 | Statistical distribution of input skews for DSFQ ISCAS'85 benchmark              |     |

|      | circuit c880, a) before partial path balancing, and b) after partial path        |     |

|      | balancing                                                                        | 326 |

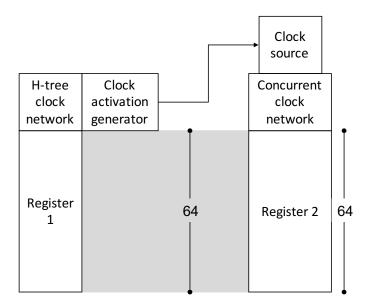

| 15.1 | Proposed GALS scheme                                                             | 335 |

| 15.2 | Proposed shared bus topology                                                     | 338 |

| 15.3 | 64-bit GALS clock activation scheme for two registers with an H-tree       |     |

|------|----------------------------------------------------------------------------|-----|

|      | clock distribution network                                                 | 340 |

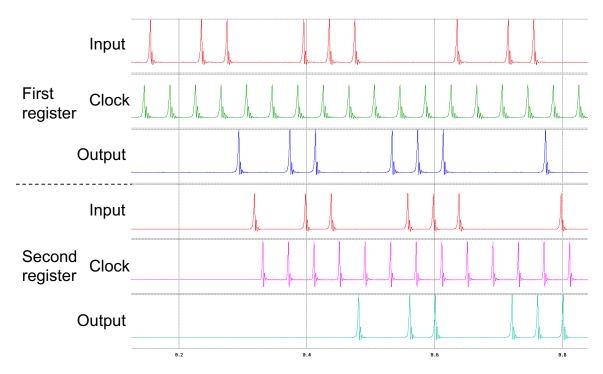

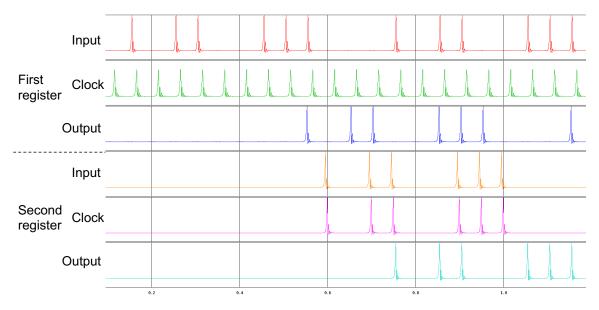

| 15.4 | Waveforms of a one bit slice of the circuit shown in Fig. 15.3             | 341 |

| 15.5 | 64-bit GALS clock activation scheme for an H-tree clocked shift register   |     |

|      | connected to a shift register synchronized by a concurrent clock network.  | 342 |

| 15.6 | Waveforms of a one bit slice of the circuit shown in Fig. 15.5             | 342 |

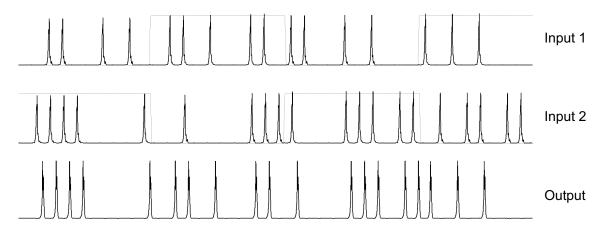

| 16.1 | DFF as a clocked blocking gate                                             | 353 |

| 16.2 | NDRO T flip flop                                                           | 354 |

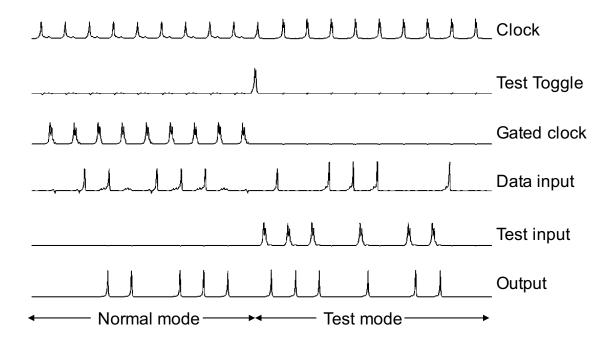

| 16.3 | Waveforms illustrating multiplexer operation performed by a blocking       |     |

|      | gate and a merger                                                          | 356 |

| 16.4 | Combination of a clocked blocking gate and a merger used for test          |     |

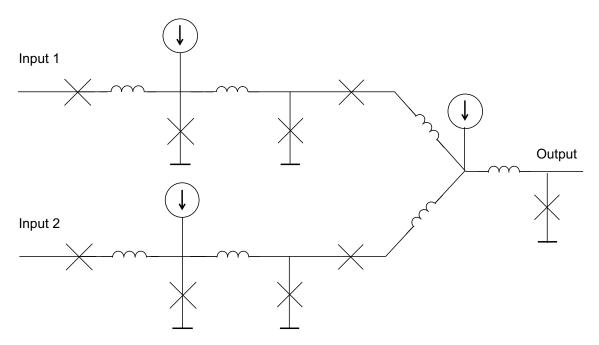

|      | point insertion                                                            | 356 |

| 16.5 | Current controlled blocking gate                                           | 357 |

| 16.6 | Multiplexer composed of two current controlled blocking gates and a CB     | 358 |

| 16.7 | Waveforms illustrating multiplexer operation performed by a current        |     |

|      | controlled blocking gate and a CB. The bias current levels are shown       |     |

|      | as dotted lines overlapping the corresponding channel inputs               | 358 |

| 16.8 | Current controlled blocking gate with inductively coupled flux bias [399]. | 360 |

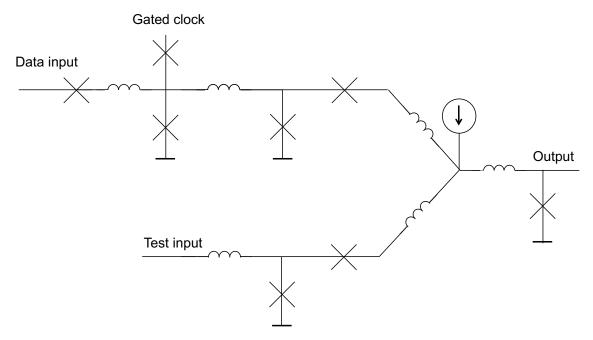

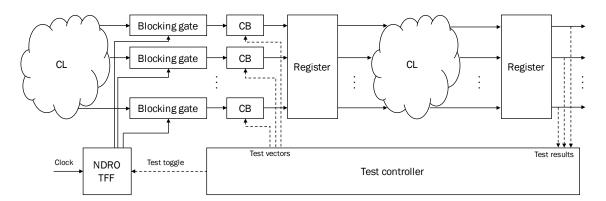

| 16.9  | Proposed test point insertion method. The dashed lines are active                         |     |

|-------|-------------------------------------------------------------------------------------------|-----|

|       | connections during test mode. A test point consists of blocking gates                     |     |

|       | and a CB (similar to the circuits shown in Figures 16.4 and 16.6) on                      |     |

|       | every bit of a data path. In this figure, the blocking gates are supplied                 |     |

|       | with a regular clock signal. This clock signal is gated by a NDRO T                       |     |

|       | flip flop controlled by a test controller                                                 | 360 |

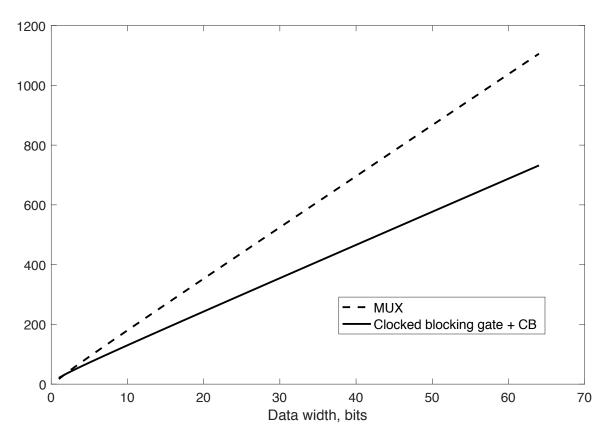

| 16.10 | Number of junctions in clocked blocking gates and confluence buffers                      |     |

|       | as compared to multiplexers for different data widths                                     | 364 |

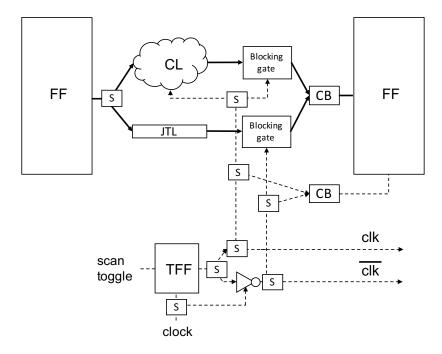

| 16.11 | Set/scan chain insertion method. The blocking gates are realized as                       |     |

|       | clocked blocking gates. A T flip flop and inverter generate complemen-                    |     |

|       | tary clock signals, $clk$ and $\overline{clk}$ . Only one of the logic paths is active at |     |

|       | any time – either regular mode (upper) or set/scan mode (lower). The                      |     |

|       | data connections are shown as bold lines, and the control signals are                     |     |

|       | shown as dashed lines                                                                     | 366 |

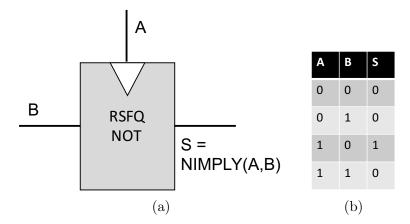

| 17.1  | DSFQ material nonimplication gate based on an RSFQ inverter, a)                           |     |

|       | circuit schematic, and b) truth table                                                     | 373 |

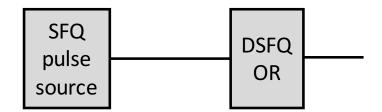

| 17.2  | SFQ pulse source for asynchronous circuits                                                | 375 |

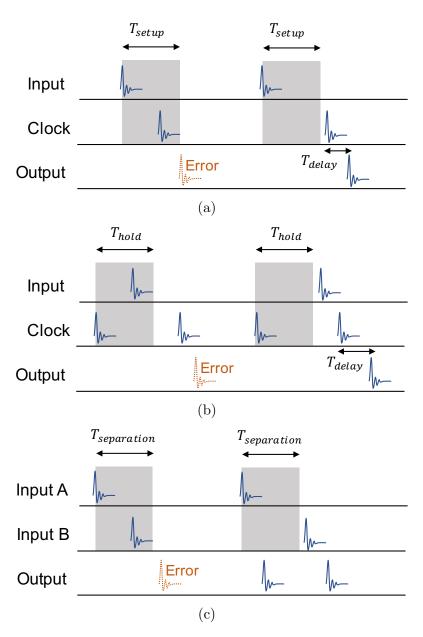

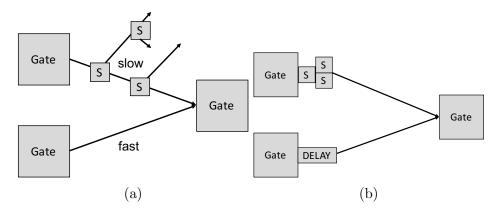

| 17.3  | Integration of splitters into standard cells to equalize gate delays with                 |     |

|       | different fanout, a) initial circuit exhibiting large input skew, and b)                  |     |

|       | modified circuit with reduced skew.                                                       | 377 |

| 17.4 | Merging of DSFQ gates with DFFs to reduce area, a) initial DSFQ           |     |

|------|---------------------------------------------------------------------------|-----|

|      | circuit with separate latch, and b) merged RSFQ/DSFQ circuit. $$          | 377 |

| 17.5 | Changing path delay by reducing routing priority, a) initial circuit with |     |

|      | delay element, and b) delay is increased by increasing wire length        | 378 |

# Chapter 1

# Introduction

A computer is a complex system of interlinked devices. The history of computing, starting with the ancient mechanical calculators, is a history of improving both the organization of these systems and the underlying device technology. From the earliest mechanical calculators, to sophisticated mechanical systems developed during the early 20<sup>th</sup> century, to electromechanical computers of the 1940's, to vacuum tube electronics of the 1950's, to transistors of the 1960's, to integrated circuits of the 1970's, culminating in very large scale integration (VLSI) over the past several decades – the computing industry has experienced over the last century multiple dramatic leaps in computing power. All of these leaps occured when the switching devices at the core of the computing system evolved, followed by a long and incremental process of component and system-level enhancements. The primary incentives for enhancing modern computing systems are to further improve performance and power efficiency.

Many different materials, devices, and technologies to build a computer exist. This book is focused on one group of technologies – superconductive electronics. This technology has the potential to vastly improve the performance and efficiency of next generation computing systems. Superconductivity is a unique phenomenon that exists in specific materials at low temperatures, first discovered in 1911 by Heike Kamerlingh Onnes [1]. The electrical resistance in a superconductive material disappears below a specific temperature. Semiconductor materials, in which the resistance drastically changes due to a variety of factors, have been known since the 19th century [2]. Theoretical explanations for both of these unusual materials were first proposed in the 1930's with the advancement of quantum theory.

Both semiconductor and superconductor electronics have evolved in parallel. The first semiconductor switching device – the transistor – was invented in 1947 by J. Bardeen, W. Brattain, and W. Shockley [3], although proposed earlier by J. E. Lilienfeld in 1925 [4]. The first superconductive switching device – the cryotron – was developed around 1954 by D. A. Buck [5], starting the field of superconductive electronics (SCE). At that time, computers primarily utilized vacuum tube elements. These early electronic computing machines were created for military applications, were expensive, and occupied significant area. Both of these new switching technologies, semiconductor-based and superconductor-based, could enable smaller and cheaper computers, as shown in Figure 1.1. Although the first cryotrons, such as the

Figure 1.1: New York Times newspaper article from February 6, 1957 [7] foreshadowing cubic foot sized computers. Ubiquitous at the time, the vacuum tube (top) is shown next to an early transistor (left), and cryotron (right).

device depicted in Figure 1.1, were composed of individual wires, the simple structure of the device enabled thin film fabrication [6] and further miniaturization. The possibility of more compact and robust computers intrigued the nascent computing industry.

Integrated circuits (IC) promised to further shrink the size of switching devices. Jack Kilby in 1958 was the first to develop a semiconductor IC, where multiple transistors were integrated on a piece of germanium [8]. Around the same time, 1957 to 1962,

the first superconductive ICs integrating multiple cryotrons and the first cryotron-based, relatively compact memory arrays were produced [9]. Cryotrons were based on a simple structure – two different metals separated by an insulator – as opposed to transistors, which required more precise control of the interaction between the dopant and semiconducting material. The superconductive nature of the devices meant that the current, representing a specific state, could circulate indefinitely without dissipation – an important advantage over transistor-based memory, which requires special latching circuits or regeneration (refresh) procedures [6]. Despite these major advantages of superconductivity, by the end of the 1960's, early semiconductor fabrication issues were resolved, and investments primarily concentrated on semiconductor electronics [9].

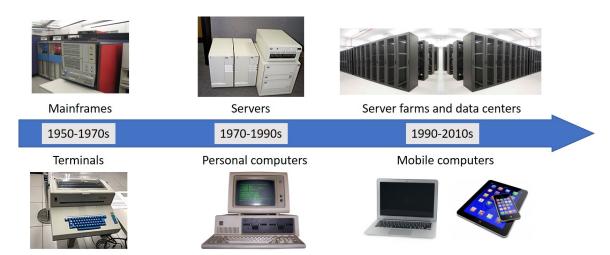

With the advancement of transistor-based electronics and integrated circuits, computing machines became more widespread and suitable for a broader variety of tasks; in particular, science and business. The number of these large (mainframe) machines, however, remained limited, and an organization often only owned a single system. Companies and universities gradually began to use these systems in a time sharing fashion, where the computing time was divided among multiple users. With the increasing number of users, operating systems were designed to automate the time sharing process [10]. Specialized terminals were used to input commands and

programs, as well as remotely analyze the results of computations. While early terminals were essentially an input device (a teletype), more advanced terminal computers contained display and additional circuits for specialized processing [11].

With further increases in the complexity of semiconductor ICs, relatively small microcomputers (personal computers) became feasible for some of the less complex computing tasks. These machines were significantly less expensive and could be installed at a workplace or even at home. For more complex tasks, these machines were used as terminals to connect over a network to a mainframe or server computers within an organization. Another application of these smaller computing systems was embedded and on-board computers. These machines were initially primarily used for military and space applications, but later adapted to a wider variety of tasks.

These applications were enabled by the shrinking size and reduced power consumption and cost of semiconductor-based ICs. The scaling of semiconductor ICs began [12] and is continuing to this day. Cryotron electronics, requiring a cryogenic environment to operate, were not competitive for these applications, and development stalled.

A major event for superconductive electronics occurred in 1962 when Brian Josephson discovered what became known as the Josephson effect, used in a novel device – the Josephson junction (JJ) [13]. This device combined a simple structure (an insulator between two layers of metal) with sub-nanosecond switching times [14]. During

Figure 1.2: Photograph of the ETL-JC1 computer [20]. Several superconductive ICs form a multi-chip module.

the 1960's and 1970's, this switching speed was rarely achieved by contemporary bipolar, NMOS, and PMOS semiconductor digital circuits [15]. Although certain semiconductor-based switching elements, such as tunnel diodes [16], have demonstrated comparable switching speeds [17], the development of diode logic was stalled by the advances of CMOS integrated circuits. A significant research effort was concentrated at IBM during this time, and later in other companies, to develop high performance JJ-based systems [18]. This effort culminated in the late 1980's with the development of ETL-JC1 in Japan, shown in Figure 1.2 – a multi-chip four bit JJ-based computer [19].

During the 1980's to 1990's, the continuing advancement of complementary metal oxide semiconductor (CMOS) electronics, fueled by interest from the rapidly growing

computing industry, enabled mobile (portable) computers. The rapid growth of this application area, and therefore increasing investment, did not help the development of superconductive electronics. Despite the comparable size of the basic devices, superconductive circuits required bulky and costly cryogenic equipment to operate, restricting this technology to large stationary systems. Simultaneously, semiconductor transistors, first bipolar, followed by NMOS and then CMOS, achieved switching speeds comparable to the early superconductive circuits. Superconductive electronics lost attractiveness due to the limitations of the primary application area, stationary computing. The development of superconductive electronics as a technology once again slowed.

In 1986, J. G. Bednorz and K. A. Müller discovered superconductivity at a temperature much higher than previously observed – a phenomenon called high temperature superconductivity (HTS) [21], as opposed to conventional low temperature superconductivity (LTS). These novel ceramic materials exhibited unusual properties which could not be explained by existing theories of superconductivity. Significant research efforts were soon dedicated to this novel area. One aspect of these efforts focused on the search for even higher temperature superconductors, with an expectation that eventually room temperature superconductivity will be discovered. Other efforts targeted HTS electronics. SCE using HTS materials could operate at significantly higher

temperatures, drastically reducing the cost of cryogenic refrigeration. These materials and circuits, however, exhibit a number of issues that complicate the design and fabrication of HTS circuits as compared to LTS circuits, making scaling complexity difficult [22].

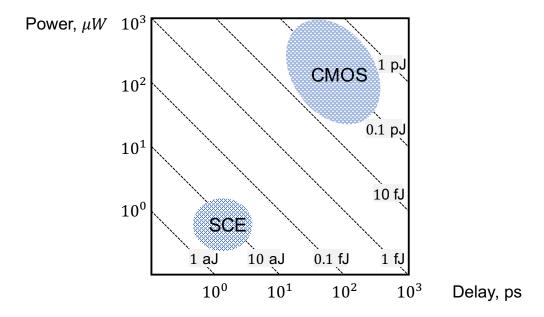

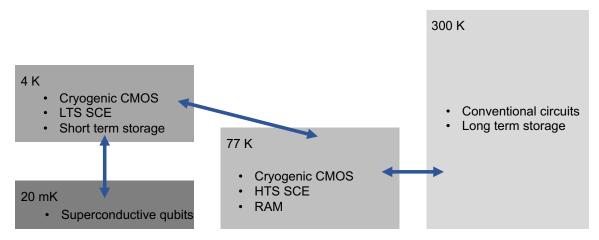

By the end of the 1980's, novel types of superconductive circuits, different from the early cryotron and JJ-based circuits, were proposed [6]. These new circuits – rapid single flux quantum (RSFQ) [23] and quantum flux parametron (QFP) [24] – exploited two primary advantages of superconductive circuits, respectively, extremely high speed and excessively low power per operation; each technology targeting high performance digital computing. Despite these advantages, the increasing speed and decreasing power consumption of CMOS circuits without requiring refrigeration, combined with the proliferation of mobile computing, prevented the widespread adoption of superconductive circuits. In addition, the novel field of HTS electronics attracted significant attention, further redirecting investment from conventional LTS circuits [6], [18]. Only a few specific niche applications, such as voltage standards and analog-to-digital conversion, remained commercially viable. Superconductive circuits for digital applications, however, continued to evolve; modern superconductive circuits have the potential to provide a significant performance advantage over conventional room temperature semiconductor-based electronics.

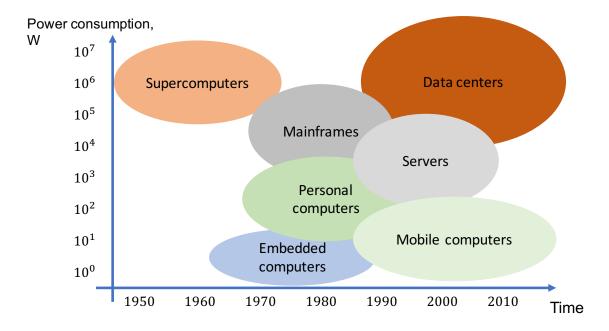

Figure 1.3: Computing systems classified by total power consumption and approximate time of development. All of these computing applications are in common use today.

Computer technology also evolved as have novel ways to use computers. As the area of applications for computers widened, the target power consumption of computing systems also widened, as shown in Figure 1.3. The rapid increase in sophistication and decrease in the size and power requirements of semiconductor ICs and systems culminated in hand-held mobile computers. Combined with the communications capability of the mobile phone, also enabled by increasingly complex ICs, smart phones are currently a primary market for integrated circuits. Conversely, over the years, large scale computing systems became even larger. Modern supercomputers and data centers frequently occupy an entire building, and consume megawatts of power [25]. From mainframes to servers to workstations to laptops to cell phones, these computing

Figure 1.4: Evolution of remote access in computing systems.

systems of all sizes and levels of power consumption are now ubiquitous, commonly used in dramatically different ways. These different computing systems are classified in Section 1.1 based on the total power consumption.

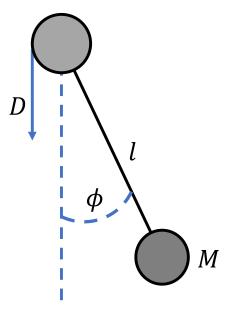

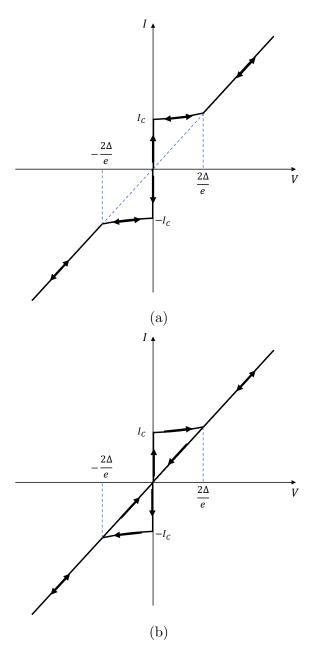

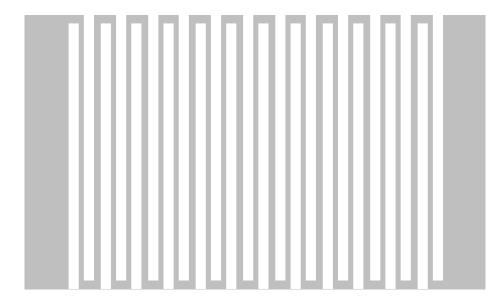

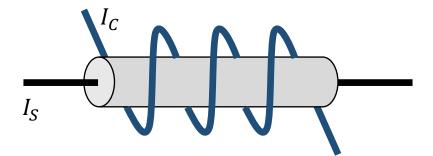

The continuing increase in the complexity of integrated circuits has enabled the advancement of computer networking technology and the Internet. The capability to access remote computers has been evolving for a long time, as shown in Figure 1.4. Modern ICs support high speed wired networks and wireless communications by providing computing power for efficient encoding and transmission of data. By combining these communications technologies with highly efficient computing hardware, modern smart phones possess the capability to access remote servers to perform complex computations which would otherwise be infeasible for these small devices. These remote stationary large scale systems, so-called "cloud" systems, are an essential part