#### Graph Algorithms for VLSI Power and Clock Networks

by

Rassul Bairamkulov

Submitted in Partial Fulfillment

of the

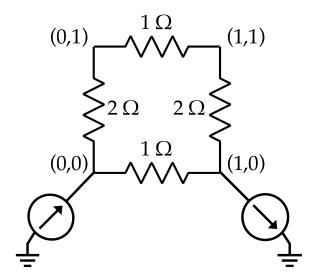

Requirements for the Degree Doctor of Philosophy

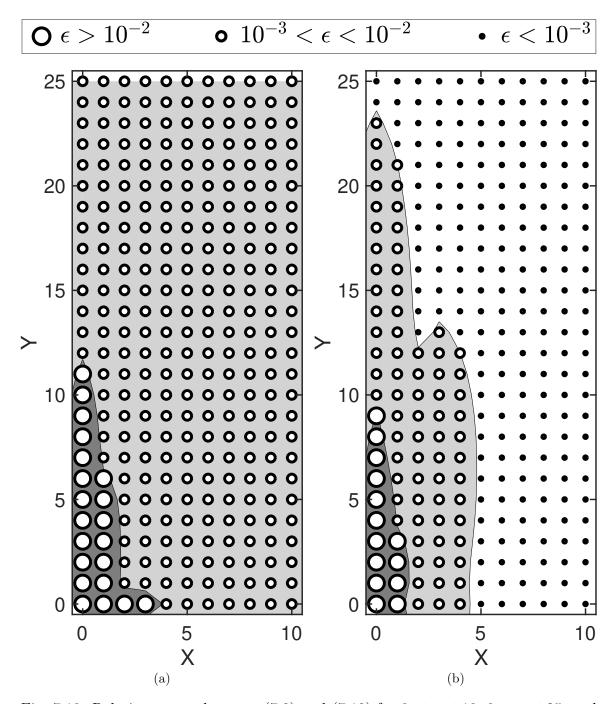

Supervised by Professor Eby G. Friedman

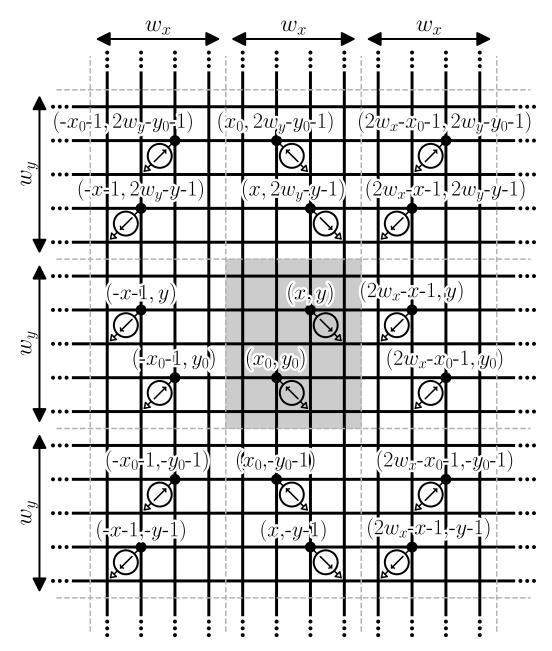

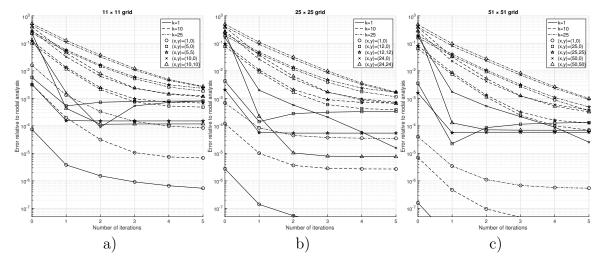

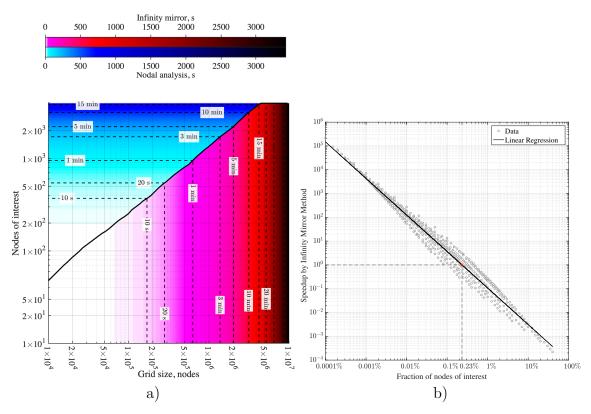

Department of Electrical and Computer Engineering

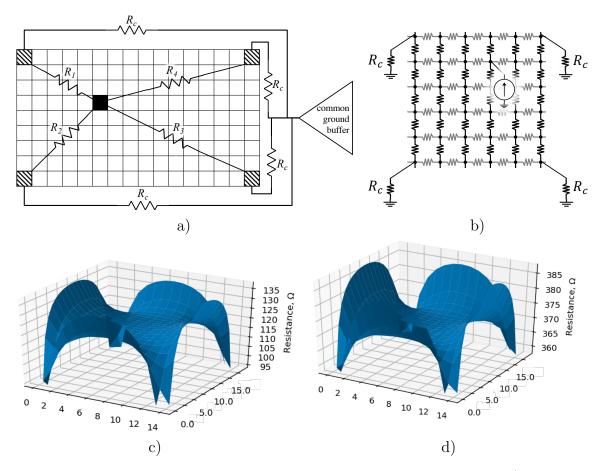

Arts, Sciences and Engineering

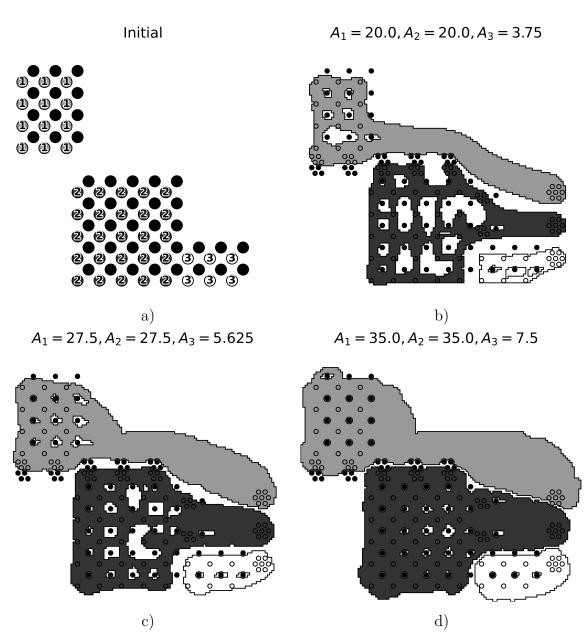

Edmund A. Hajim School of Engineering and Applied Sciences

University of Rochester Rochester, New York 2022

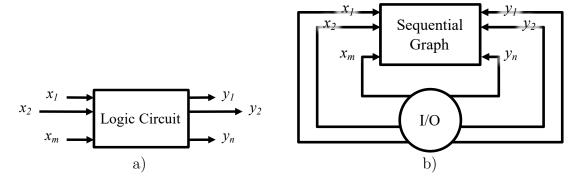

## Table of Contents

| Bi         | Biographical Sketch              |                    |      |  |  |

|------------|----------------------------------|--------------------|------|--|--|

| A          | f Acknowledgments                |                    |      |  |  |

| <b>A</b> l | Abstract                         |                    |      |  |  |

| Co         | Contributors and Funding Sources |                    |      |  |  |

| Li         | ist of Tables x                  |                    |      |  |  |

| Li         | st of                            | Figures            | xxii |  |  |

| 1          | Intr                             | roduction          | 1    |  |  |

|            | 1.1                              | Precursors of VLSI | 5    |  |  |

|            | 1.2                              | The rise of VLSI   | 10   |  |  |

|            | 1.3                              | Proposal outline   | 18   |  |  |

| Gra | ph fundamentals                               | 23                                                                                                                                                                                                                                                                                                                                                                   |

|-----|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1 | Graph categories                              | 27                                                                                                                                                                                                                                                                                                                                                                   |

|     | 2.1.1 Hypergraph                              | 28                                                                                                                                                                                                                                                                                                                                                                   |

|     | 2.1.2 Graphs with parallel edges              | 31                                                                                                                                                                                                                                                                                                                                                                   |

|     | 2.1.3 Graphs without parallel edges           | 34                                                                                                                                                                                                                                                                                                                                                                   |

|     | 2.1.4 Weighted graph                          | 34                                                                                                                                                                                                                                                                                                                                                                   |

|     | 2.1.5 Directed graph                          | 36                                                                                                                                                                                                                                                                                                                                                                   |

| 2.2 | Inter-graph relationships                     | 39                                                                                                                                                                                                                                                                                                                                                                   |

| 2.3 | Graph exploration                             | 41                                                                                                                                                                                                                                                                                                                                                                   |

| 2.4 | Bipartite graph                               | 43                                                                                                                                                                                                                                                                                                                                                                   |

| 2.5 | Directed acyclic graph                        | 44                                                                                                                                                                                                                                                                                                                                                                   |

| 2.6 | Tree                                          | 46                                                                                                                                                                                                                                                                                                                                                                   |

| 2.7 | Common problems in graph theory               | 50                                                                                                                                                                                                                                                                                                                                                                   |

|     | 2.7.1 Pathfinding                             | 52                                                                                                                                                                                                                                                                                                                                                                   |

|     | 2.7.2 Spanning tree                           | 68                                                                                                                                                                                                                                                                                                                                                                   |

|     | 2.7.3 Graph coloring                          | 83                                                                                                                                                                                                                                                                                                                                                                   |

|     | 2.7.4 Topological sorting                     | 90                                                                                                                                                                                                                                                                                                                                                                   |

| 2.8 | Summary                                       | 95                                                                                                                                                                                                                                                                                                                                                                   |

| Gra | phs in VLSI circuits and systems              | 96                                                                                                                                                                                                                                                                                                                                                                   |

|     | 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7 | 2.1.1 Hypergraph 2.1.2 Graphs with parallel edges 2.1.3 Graphs without parallel edges 2.1.4 Weighted graph 2.1.5 Directed graph 2.1 Inter-graph relationships 2.3 Graph exploration 2.4 Bipartite graph 2.5 Directed acyclic graph 2.6 Tree 2.7 Common problems in graph theory 2.7.1 Pathfinding 2.7.2 Spanning tree 2.7.3 Graph coloring 2.7.4 Topological sorting |

|   | 3.1 | Graph  | as as a VLSI abstraction tool             | 102 |

|---|-----|--------|-------------------------------------------|-----|

|   | 3.2 | Regist | er transfer level                         | 104 |

|   |     | 3.2.1  | Register allocation                       | 106 |

|   |     | 3.2.2  | Task scheduling                           | 113 |

|   |     | 3.2.3  | Synchronization                           | 119 |

|   | 3.3 | Gate l | layer                                     | 126 |

|   |     | 3.3.1  | Ordered binary decision diagram           | 130 |

|   |     | 3.3.2  | And-inverter graph                        | 133 |

|   | 3.4 | Circui | t layer                                   | 136 |

|   |     | 3.4.1  | Laplacian matrix of a circuit graph       | 137 |

|   | 3.5 | Physic | cal layer                                 | 146 |

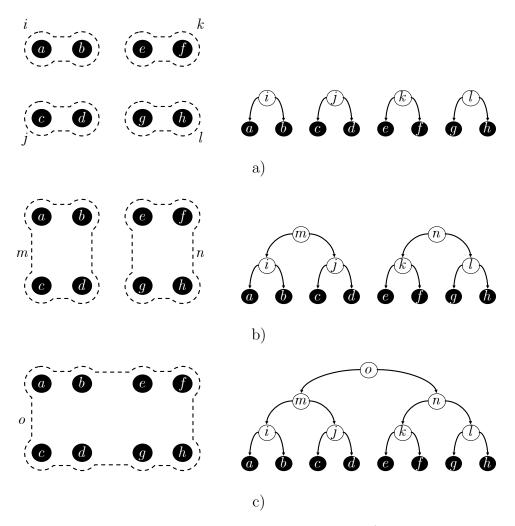

|   |     | 3.5.1  | Partitioning                              | 149 |

|   |     | 3.5.2  | Floorplanning                             | 155 |

|   |     | 3.5.3  | Placement                                 | 158 |

|   |     | 3.5.4  | Routing                                   | 161 |

|   | 3.6 | Summ   | nary                                      | 167 |

| 4 | Syn | chroni | zation in VLSI                            | 169 |

|   | 4.1 | Graph  | n-based timing analysis                   | 176 |

|   |     | 4.1.1  | Timing constraints in synchronous systems | 178 |

|   |     |        |                                           |     |

|   | 4.2  | Clock   | skew scheduling              | 198 |

|---|------|---------|------------------------------|-----|

|   |      | 4.2.1   | Robustness                   | 198 |

|   |      | 4.2.2   | Performance                  | 208 |

|   |      | 4.2.3   | Power                        | 217 |

|   | 4.3  | Clock   | tree synthesis               | 222 |

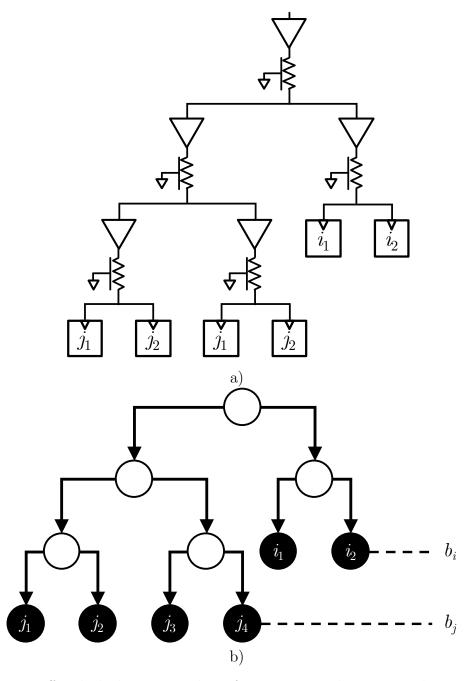

|   |      | 4.3.1   | Clock tree topology          | 225 |

|   |      | 4.3.2   | Clock tree embedding         | 238 |

|   |      | 4.3.3   | Methods of means and medians | 239 |

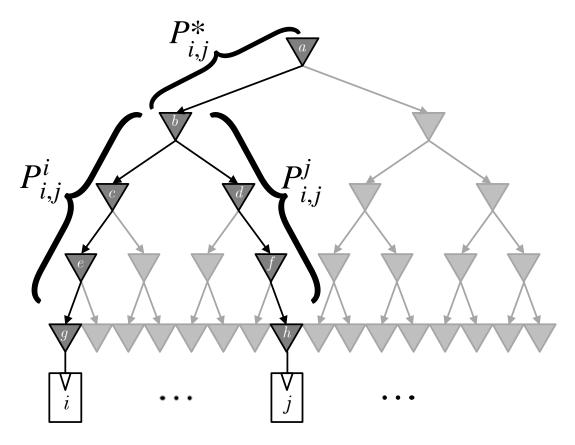

|   |      | 4.3.4   | Deferred merge embedding     | 240 |

|   |      | 4.3.5   | Elmore delay                 | 243 |

|   |      | 4.3.6   | Bounded skew tree            | 244 |

|   |      | 4.3.7   | Useful skew tree             | 246 |

|   | 4.4  | Summ    | ary                          | 247 |

| 5 | Circ | cuit an | aalysis                      | 249 |

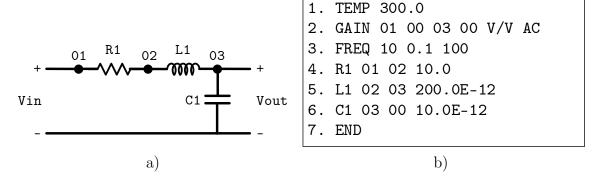

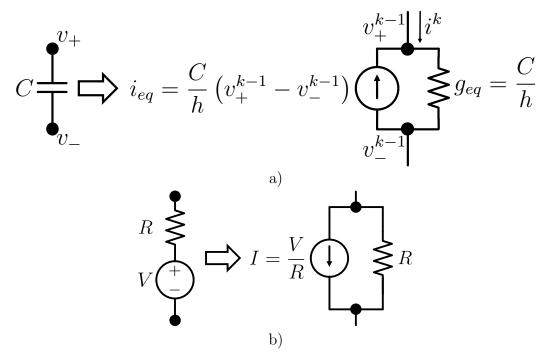

|   | 5.1  |         | ied nodal analysis           | 252 |

|   |      |         | ·                            |     |

|   | 5.2  | Iterati | ive numerical methods        | 260 |

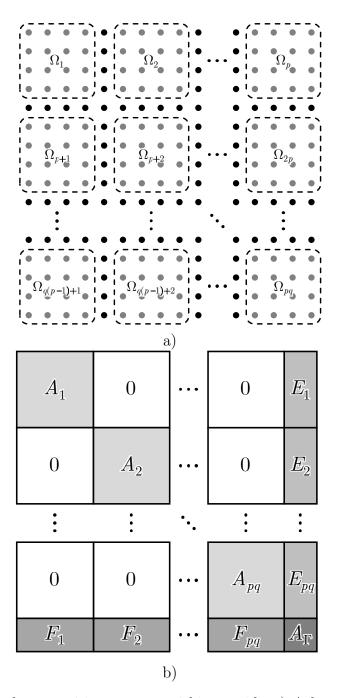

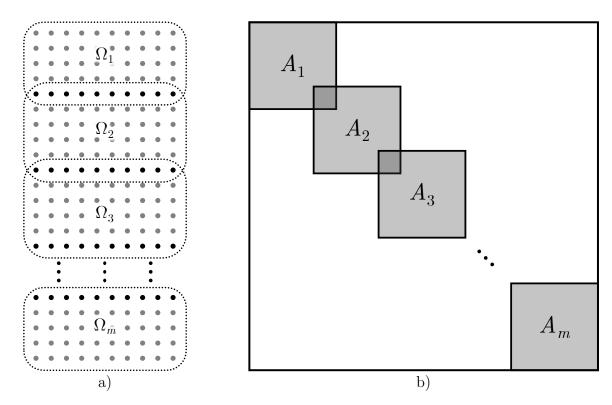

|   |      | 5.2.1   | Domain decomposition         | 266 |

|   |      | 5.2.2   | ${\cal H}	ext{-matrix}$      | 272 |

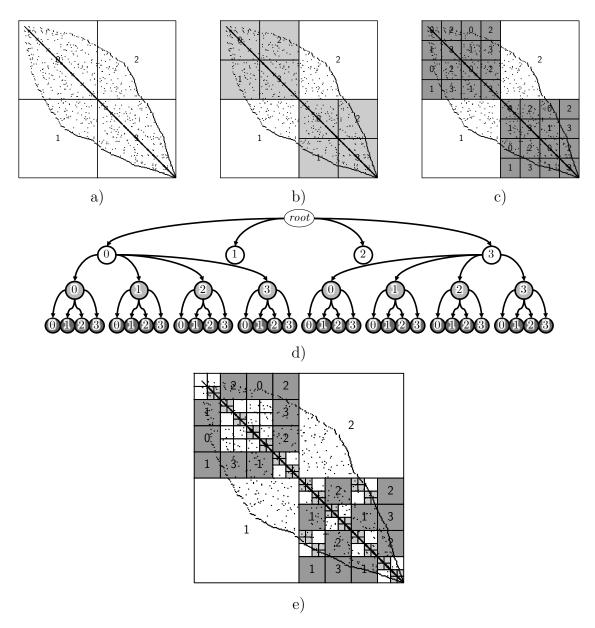

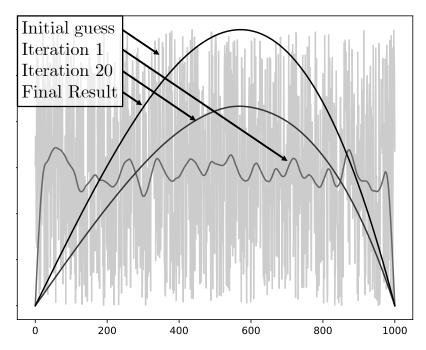

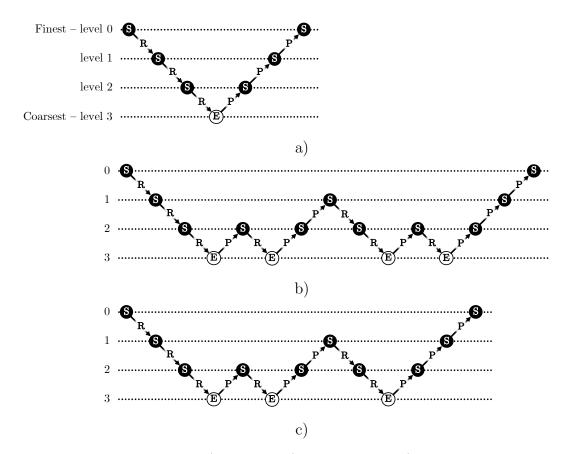

|   |      | 5.2.3   | Multigrid methods            | 273 |

|   | 5.3  | Non-MNA techniques                                  | 280 |

|---|------|-----------------------------------------------------|-----|

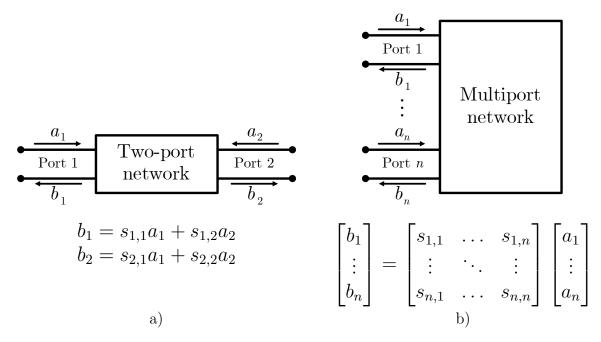

|   |      | 5.3.1 Scattering parameters                         | 280 |

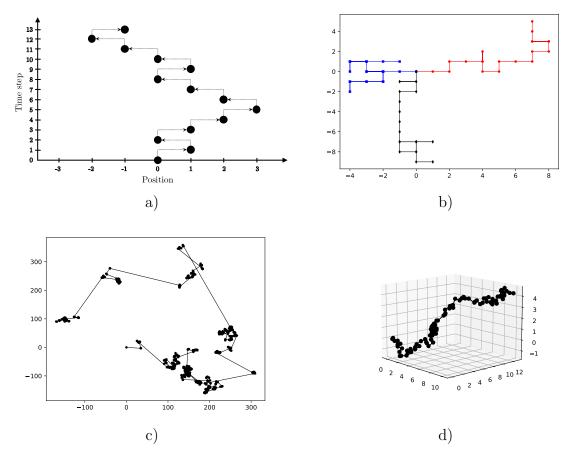

|   |      | 5.3.2 Random walks                                  | 283 |

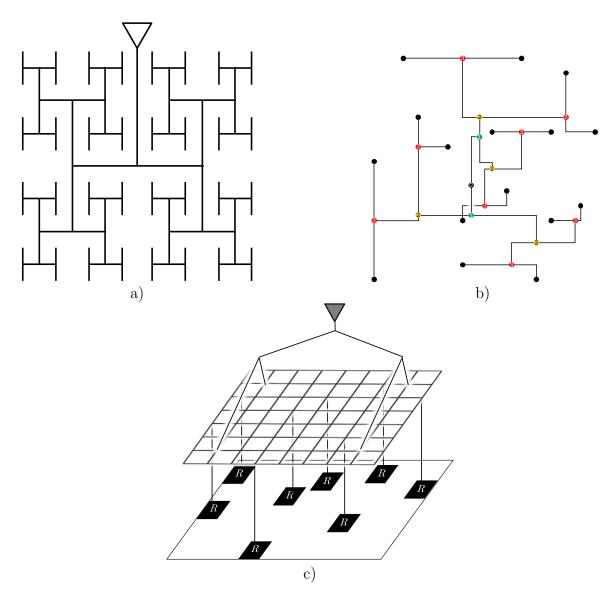

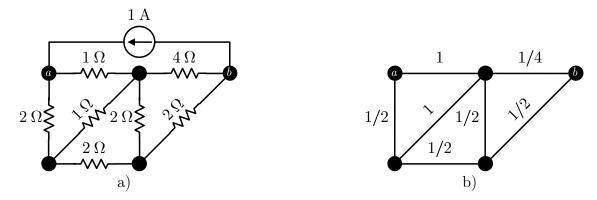

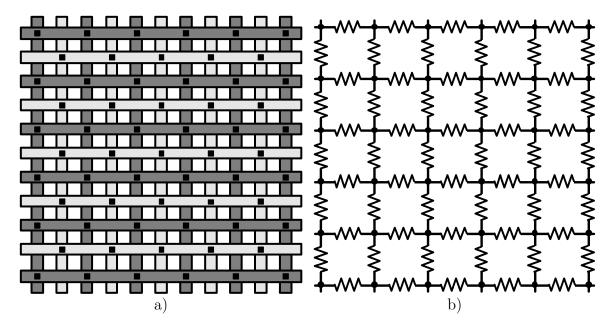

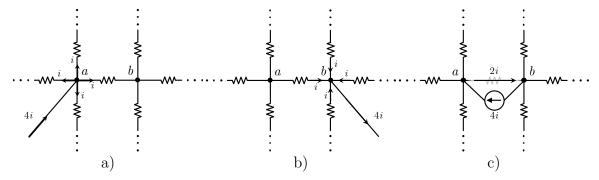

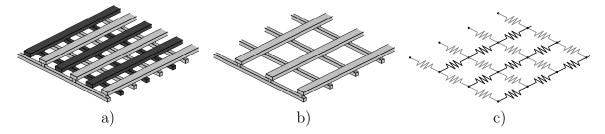

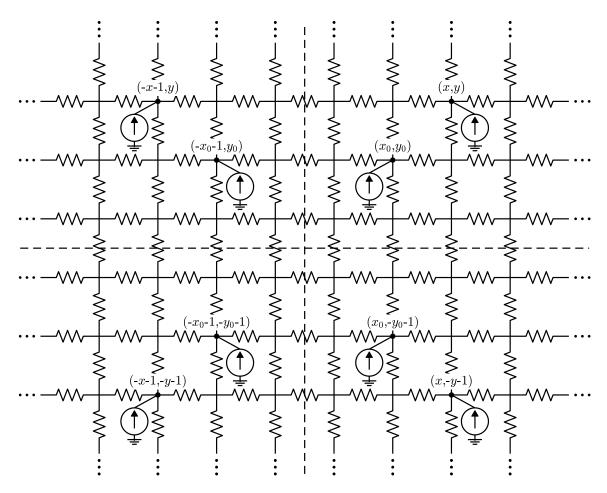

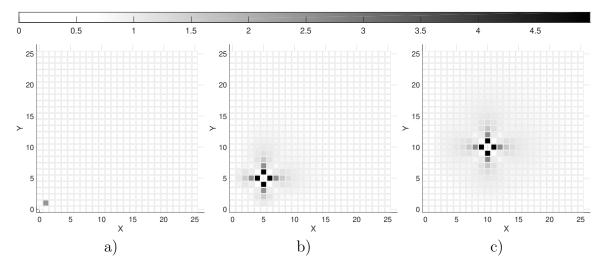

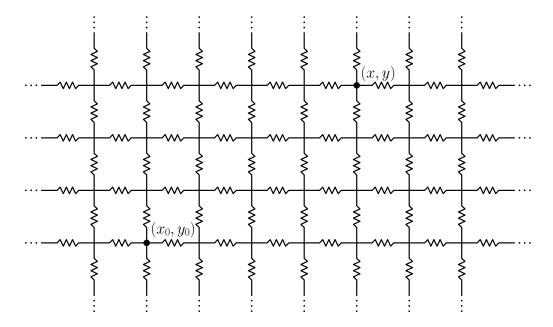

|   |      | 5.3.3 Lattice graph                                 | 288 |

|   | 5.4  | Summary                                             | 295 |

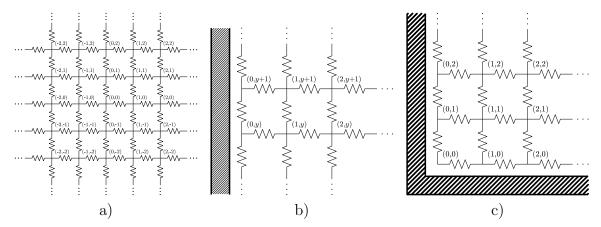

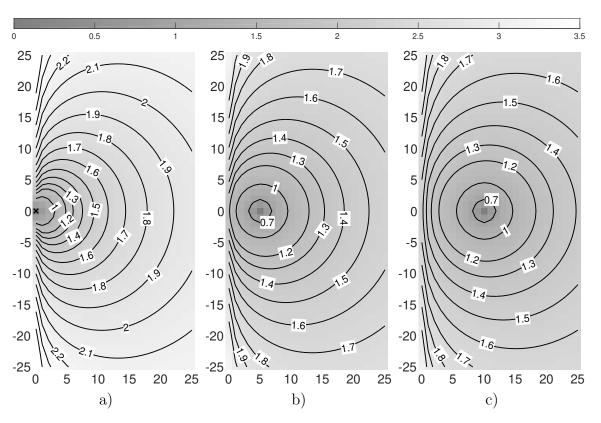

| 6 | Effe | ective resistance of truncated meshes               | 297 |

|   | 6.1  | Historical perspective                              | 300 |

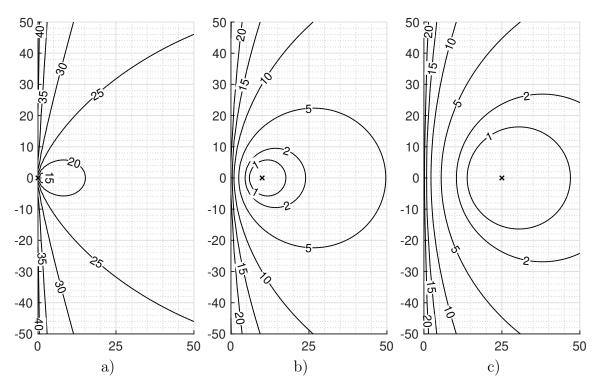

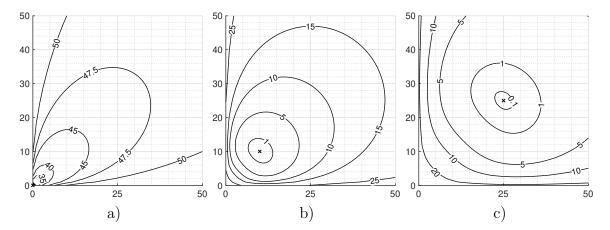

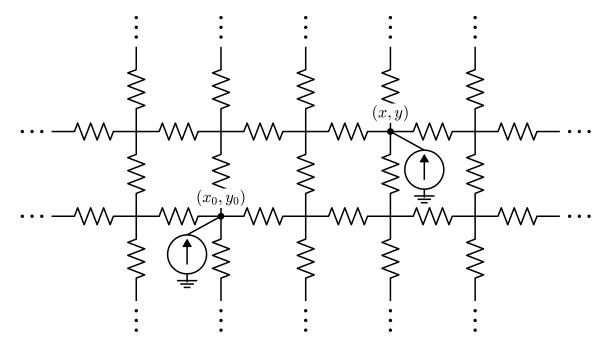

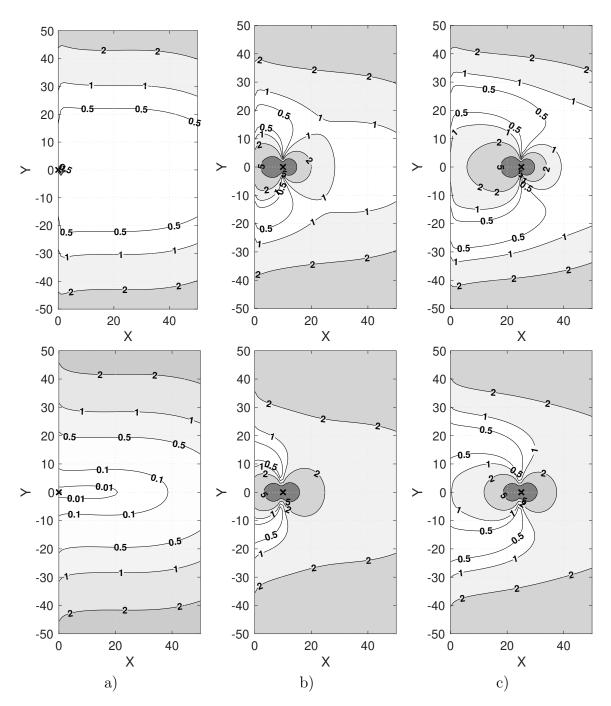

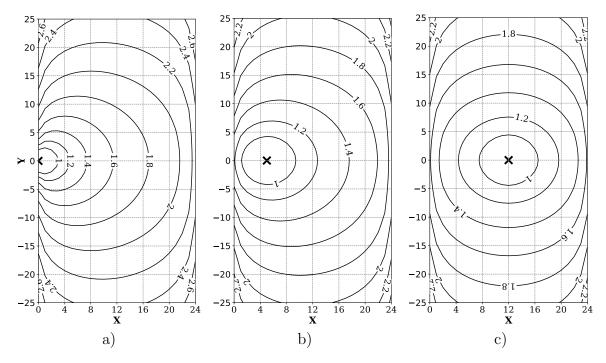

|   | 6.2  | Electric potential in an infinite mesh              | 301 |

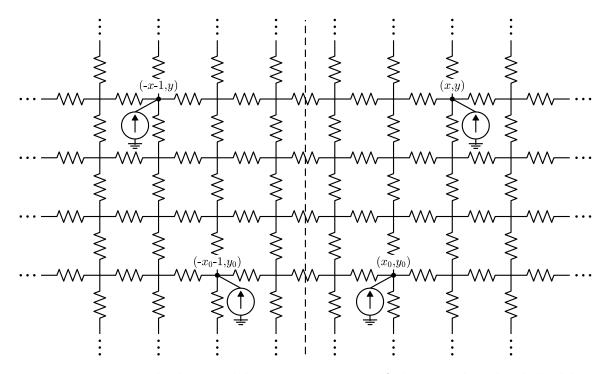

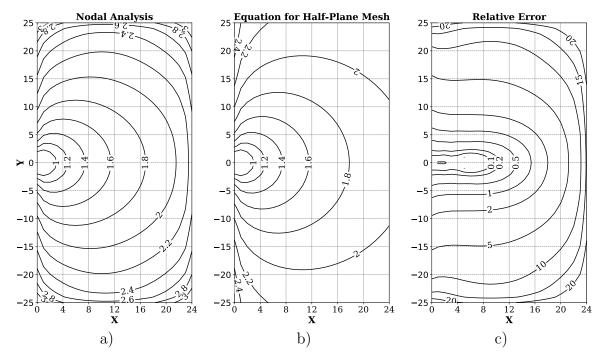

|   | 6.3  | Electric potential within a truncated infinite mesh | 305 |

|   |      | 6.3.1 Modeling truncation with image                | 306 |

|   |      | 6.3.2 Integral expressions for effective resistance | 310 |

|   | 6.4  | Closed-form approximation                           | 315 |

|   | 6.5  | Model evaluation                                    | 319 |

|   |      | 6.5.1 Accuracy evaluation                           | 319 |

|   |      | 6.5.2 Computational speed                           | 320 |

|   | 6.6  | Conclusions                                         | 325 |

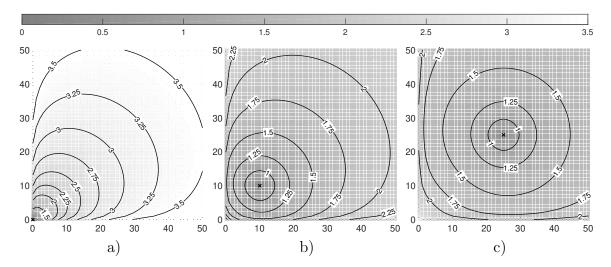

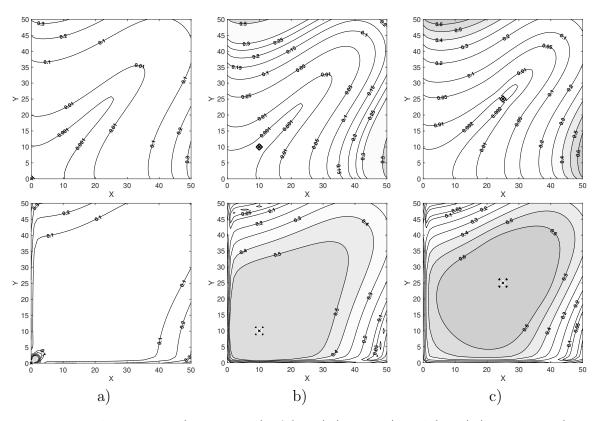

| 7 | Effe | ective resistance of finite grids                   | 326 |

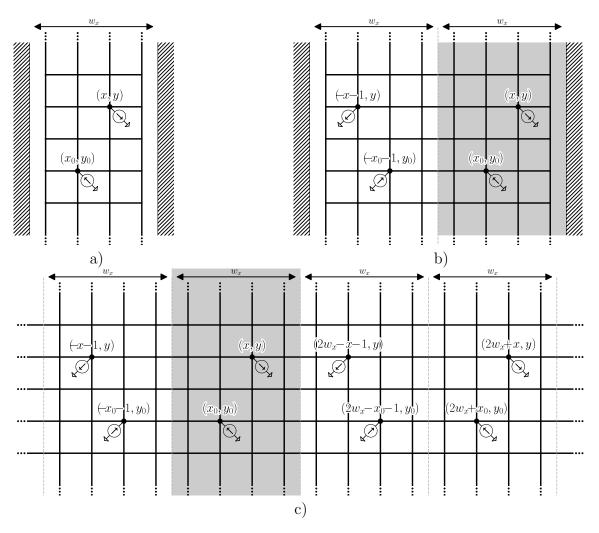

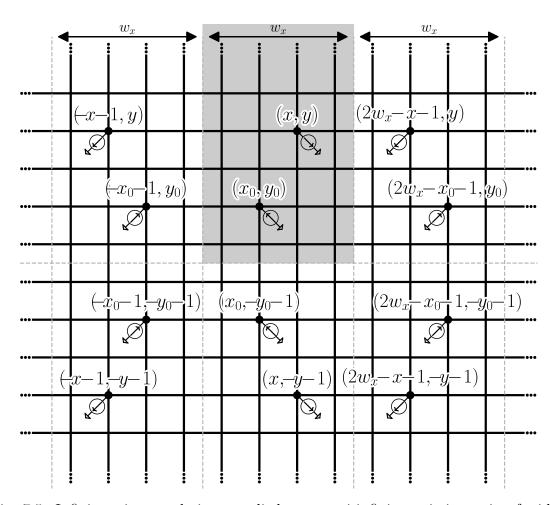

|   | 7.1  | Infinity mirror technique                           | 330 |

|   |      | 7.1.1 Infinite strip                                | 332 |

|   |            | 7.1.2                           | Semi-infinite strip                          | 338                             |

|---|------------|---------------------------------|----------------------------------------------|---------------------------------|

|   |            | 7.1.3                           | Finite mesh                                  | 338                             |

|   |            | 7.1.4                           | Generalization to higher dimensions          | 342                             |

|   | 7.2        | Simpli                          | fication of the resistance expressions       | 345                             |

|   | 7.3        | Case s                          | etudies                                      | 349                             |

|   |            | 7.3.1                           | Mesh reduction based on effective resistance | 349                             |

|   |            | 7.3.2                           | Resistive noise in capacitive touch screen   | 353                             |

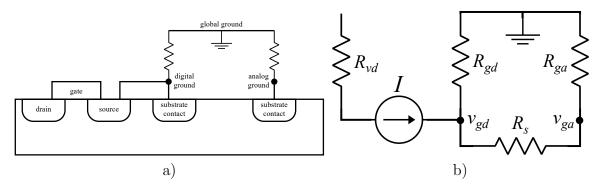

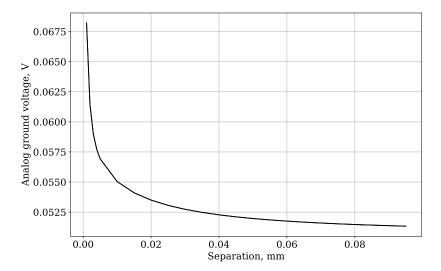

|   |            | 7.3.3                           | Resistive substrate noise                    | 355                             |

|   | 7.4        | Conclu                          | asions                                       | 357                             |

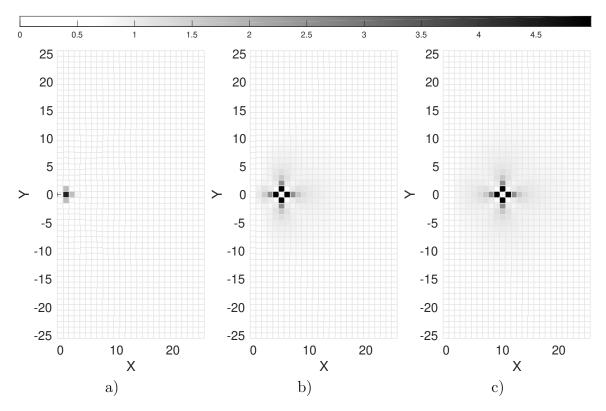

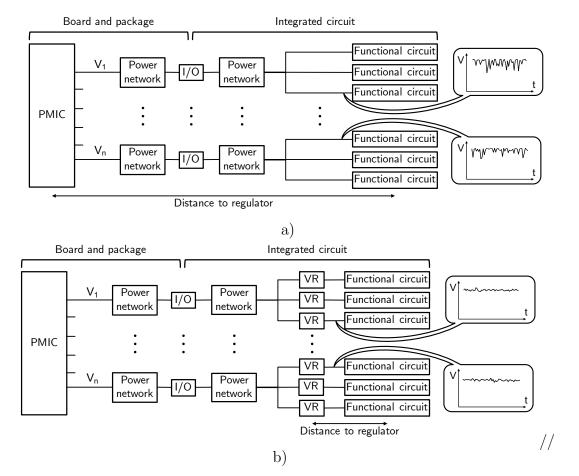

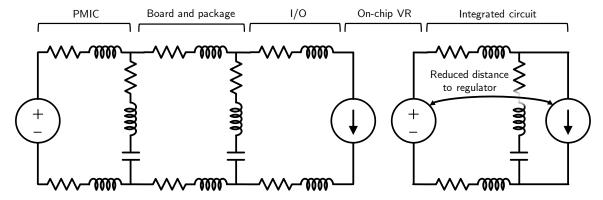

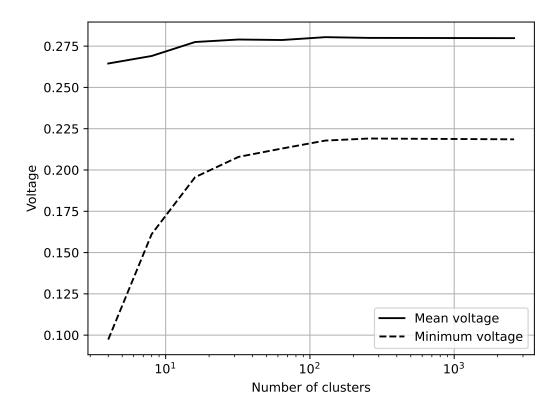

| 8 | Plac       | cement                          | t of On-Chip Distributed Voltage Regulators  | 360                             |

|   | 8.1        | 0 . 1                           | . 1, 1, .                                    |                                 |

|   |            | On-cn                           | ip voltage regulation                        | 364                             |

|   | 8.2        |                                 | of power network                             |                                 |

|   | 8.2        |                                 |                                              | 369                             |

|   | 8.2        | Model                           | of power network                             | 369<br>371                      |

|   | 8.2        | Model<br>8.2.1<br>8.2.2         | of power network                             | 369<br>371<br>377               |

|   |            | Model<br>8.2.1<br>8.2.2<br>Load | of power network                             | 369<br>371<br>377               |

|   | 8.3        | Model 8.2.1 8.2.2 Load of       | of power network                             | 369<br>371<br>377<br>379        |

|   | 8.3<br>8.4 | Model 8.2.1 8.2.2 Load of       | of power network                             | 369<br>371<br>377<br>379<br>383 |

|    |      | 8.5.3   | Restricted current – case three                        | 388 |

|----|------|---------|--------------------------------------------------------|-----|

|    | 8.6  | Conclu  | isions                                                 | 391 |

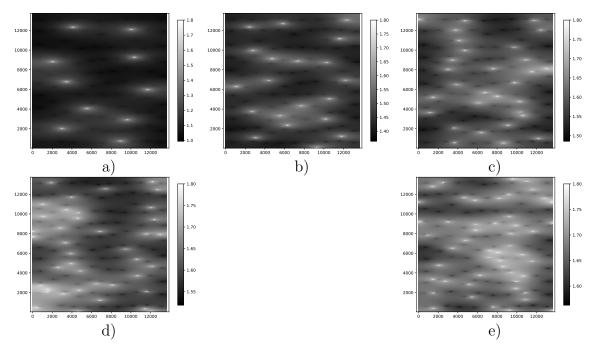

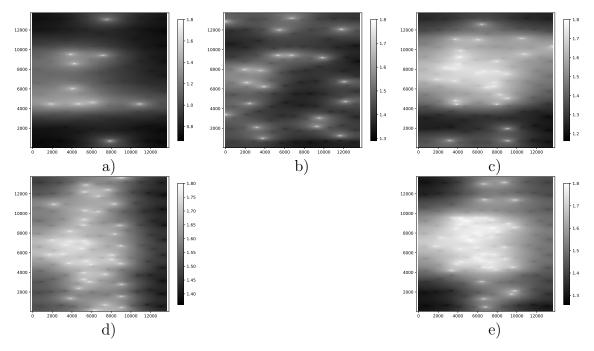

| 9  | Exp  | loratoi | ry methodology for power delivery                      | 393 |

|    | 9.1  | Optim   | ization framework                                      | 396 |

|    |      | 9.1.1   | Specification of the electrical design requirements    | 399 |

|    |      | 9.1.2   | Specification of non-electrical design requirements    | 401 |

|    |      | 9.1.3   | Combination of electrical and nonelectrical metrics    | 402 |

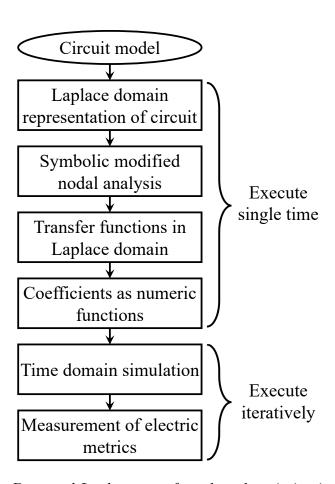

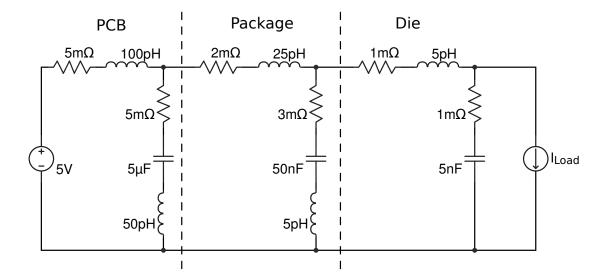

|    |      | 9.1.4   | Circuit simulation procedure                           | 404 |

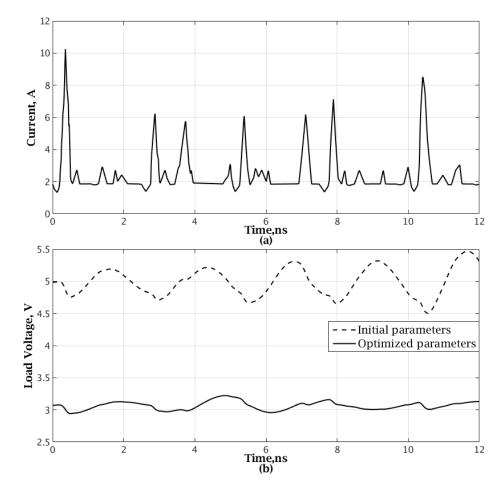

|    | 9.2  | Case s  | tudies                                                 | 410 |

|    |      | 9.2.1   | Single rail system                                     | 410 |

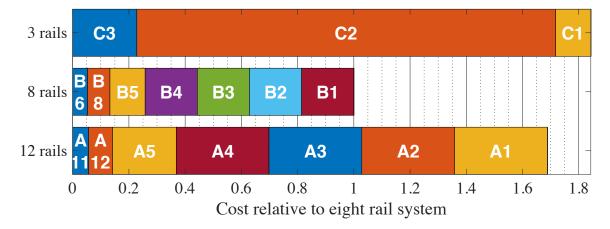

|    |      | 9.2.2   | Multiple rail system                                   | 417 |

|    | 9.3  | Conclu  | asions                                                 | 425 |

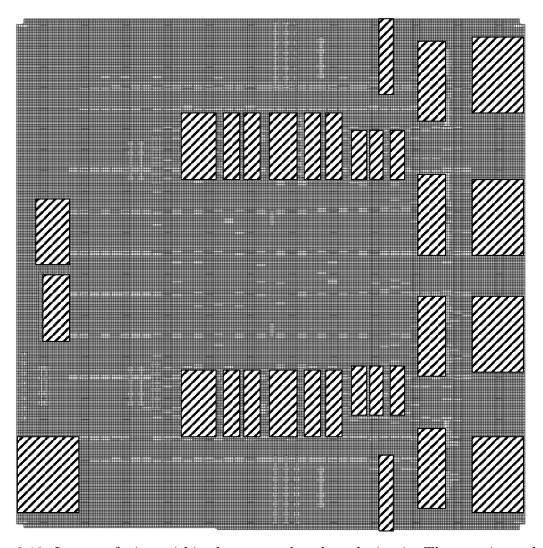

| 10 | SPF  | ROUT    | - Smart Power ROUting Tool for board-level exploration | n   |

|    | and  | protot  | cyping                                                 | 427 |

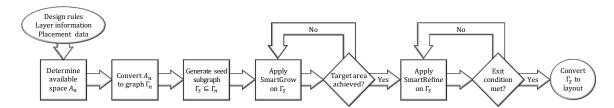

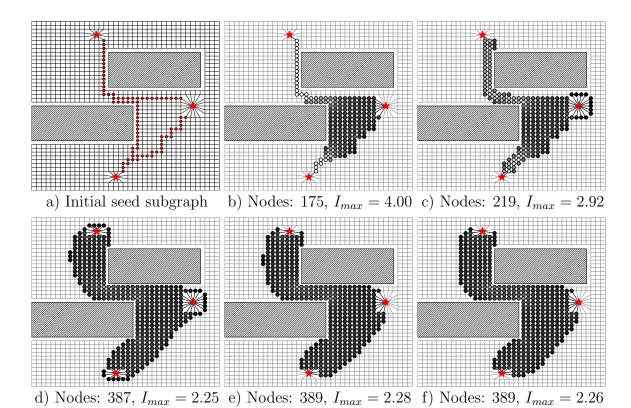

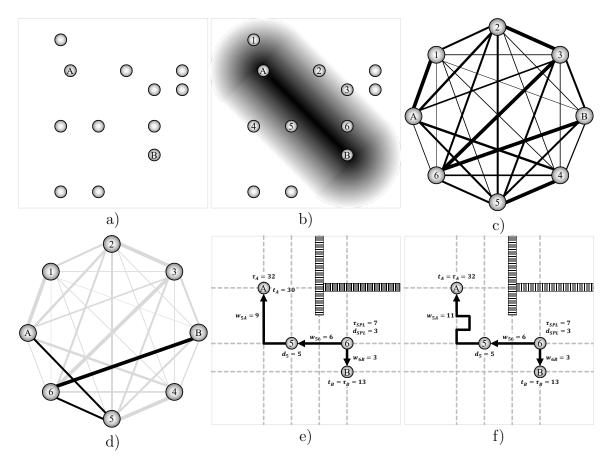

|    | 10.1 | SPRO    | UT algorithm                                           | 432 |

|    |      | 10.1.1  | Available routing space                                | 434 |

|    |      | 10.1.2  | Equivalent graph                                       | 436 |

|    |      | 10.1.3  | Seed subgraph                                          | 437 |

|    |      | 10.1.4  | Growth stage                                           | 441 |

|    |      | 10.1.5                                        | Refinement stage                                                                               | 444                                    |

|----|------|-----------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------|

|    |      | 10.1.6                                        | Subgraph reheating                                                                             | 446                                    |

|    |      | 10.1.7                                        | Back conversion                                                                                | 447                                    |

|    |      | 10.1.8                                        | Algorithm runtime analysis                                                                     | 447                                    |

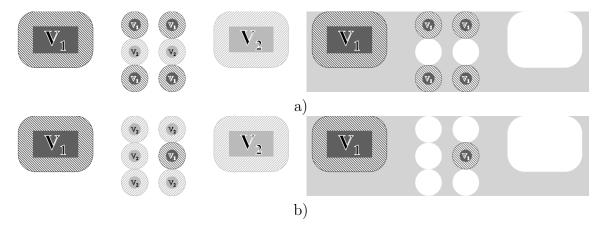

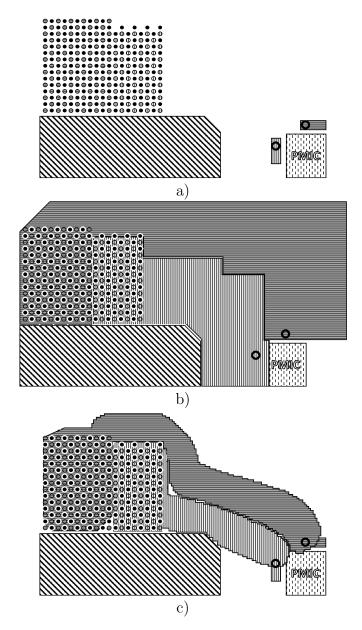

|    | 10.2 | Valida                                        | tion of case study                                                                             | 451                                    |

|    |      | 10.2.1                                        | Two rail system                                                                                | 452                                    |

|    |      | 10.2.2                                        | Six rail system                                                                                | 454                                    |

|    |      | 10.2.3                                        | Area/impedance tradeoff                                                                        | 456                                    |

|    | 10.3 | Conclu                                        | asions                                                                                         | 459                                    |

|    |      |                                               |                                                                                                |                                        |

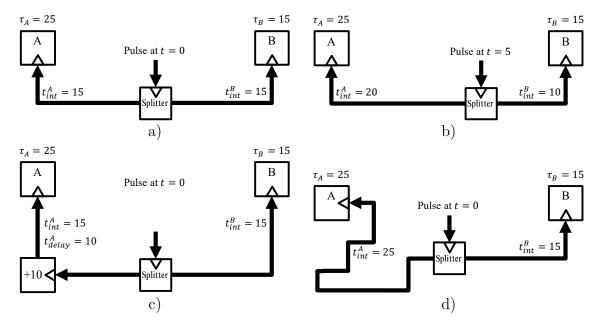

| 11 | QuC  | $\mathbf{CTS} - \mathbf{i}$                   | single flux Quantum Clock Tree Synthesis                                                       | 462                                    |

| 11 |      |                                               | single flux Quantum Clock Tree Synthesis                                                       |                                        |

| 11 |      | Clock                                         |                                                                                                | 466                                    |

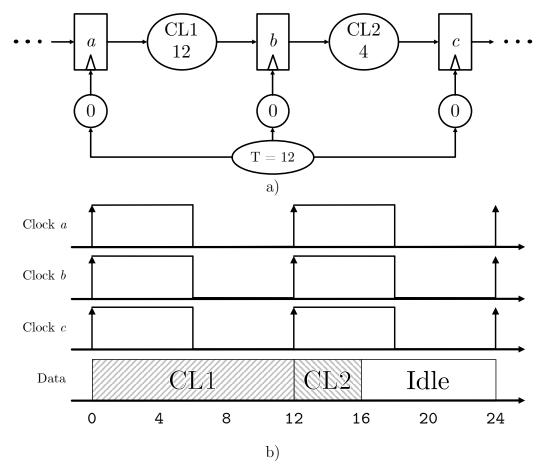

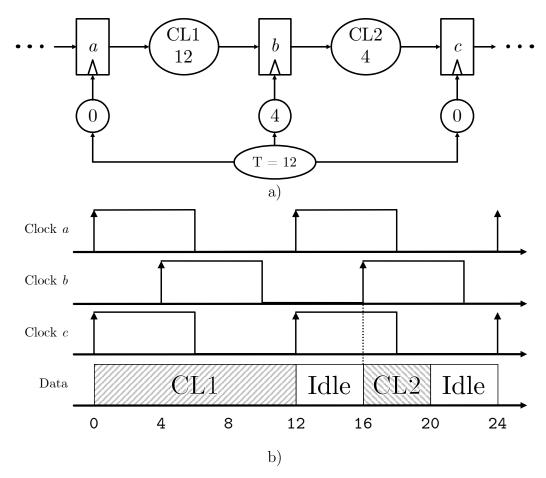

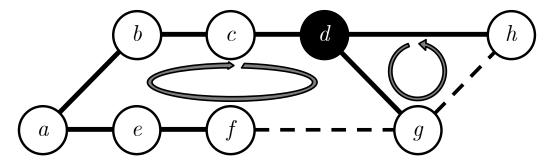

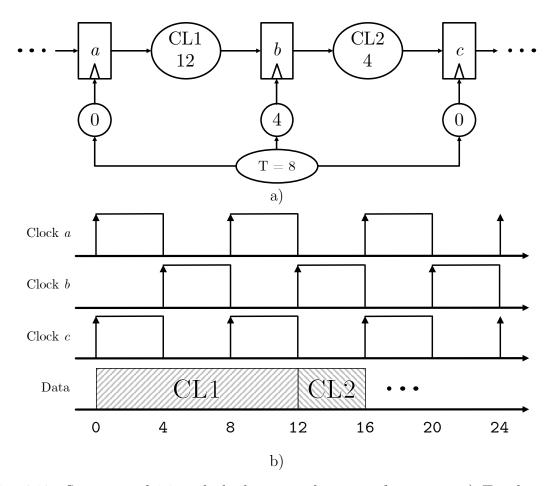

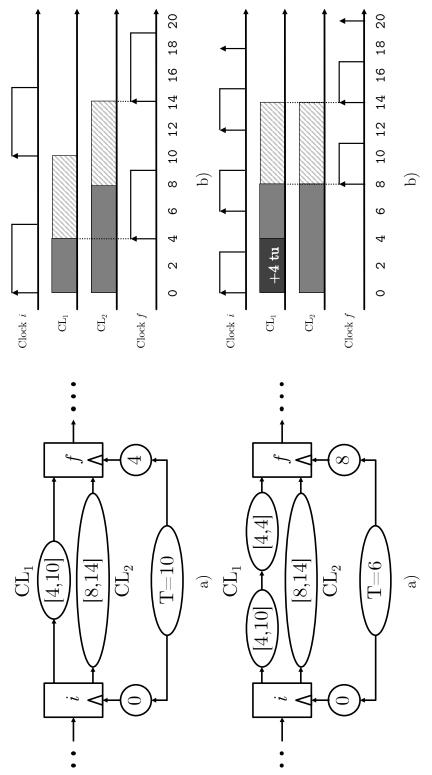

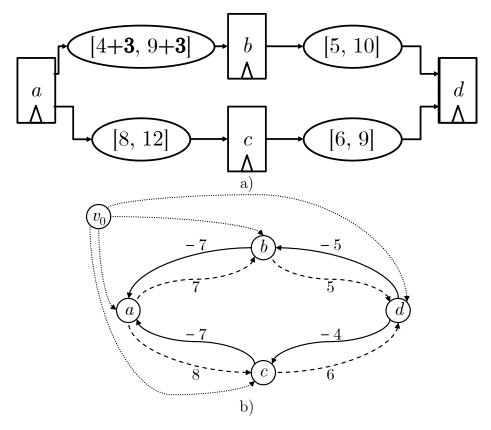

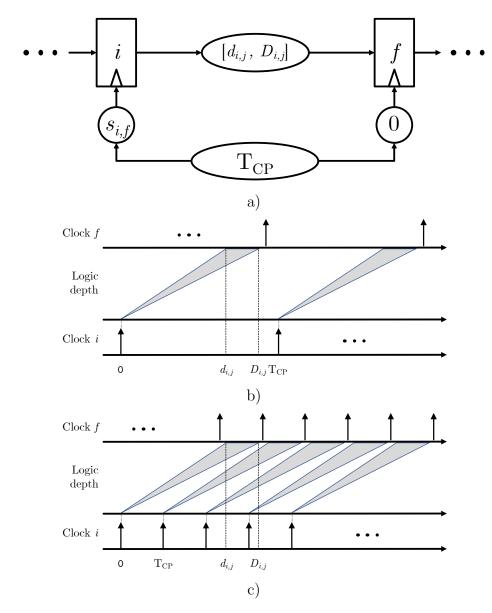

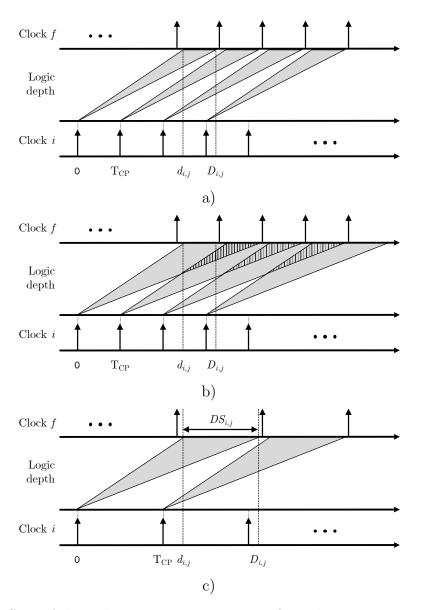

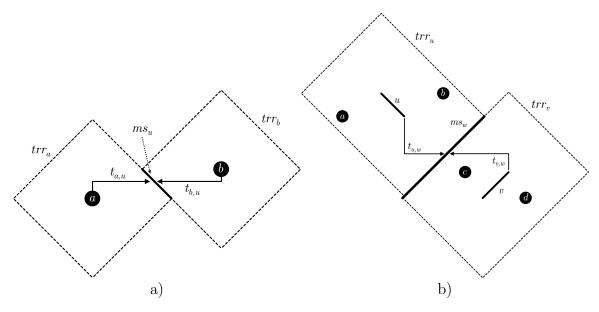

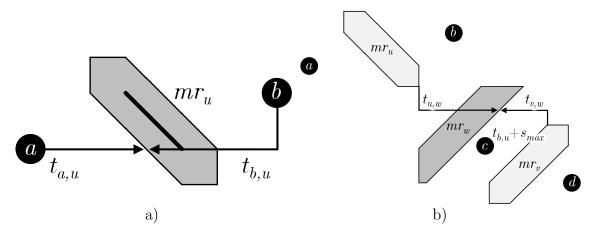

| 11 |      | Clock 11.1.1                                  | skew scheduling                                                                                | 466                                    |

| 11 |      | Clock 11.1.1 11.1.2                           | skew scheduling                                                                                | 466<br>467<br>468                      |

| 11 | 11.1 | Clock 11.1.1 11.1.2 11.1.3                    | Skew scheduling                                                                                | 466<br>467<br>468<br>472               |

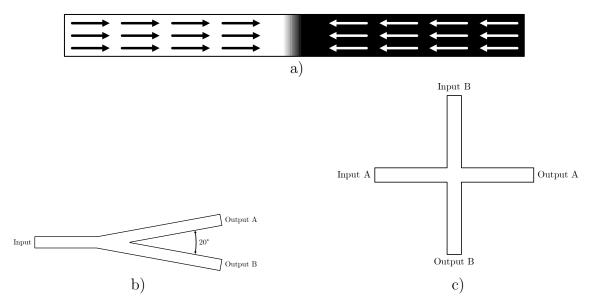

| 11 | 11.1 | Clock 11.1.1 11.1.2 11.1.3 Clock              | Sequential graph                                                                               | 466<br>467<br>468<br>472               |

| 11 | 11.1 | Clock 11.1.1 11.1.2 11.1.3 Clock Delay        | skew scheduling                                                                                | 466<br>467<br>468<br>472<br>475        |

| 11 | 11.1 | Clock 11.1.1 11.1.2 11.1.3 Clock Delay 11.3.1 | Sequential graph  Minimum clock period  Clock skew optimization  tree synthesis  equilibration | 466<br>467<br>468<br>472<br>475<br>479 |

| 11.4 Case study                                    | 493 |

|----------------------------------------------------|-----|

| 11.5 Conclusions                                   | 496 |

| 12 Conclusions                                     | 498 |

| 13 Future work                                     | 506 |

| 13.1 Lattice-based multigrid analysis              | 507 |

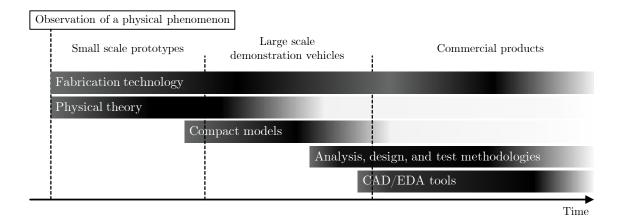

| 13.2 EDA tools for emerging technologies           | 509 |

| Appendix A Green's function for a truncated grid   | 514 |

| Appendix B Uniqueness based on boundary conditions | 517 |

| Appendix C Multilayer routing algorithm            | 520 |

| Bibliography                                       | 523 |

### Biographical Sketch

Rassul Bairamkulov was born in August 1994 in Karaganda, Kazakhstan. He received a Bachelor of Engineering in Electrical and Electronic Engineering degree from Nazarbayev University in Astana, Kazakhstan in 2016, and a Master of Science degree in Electrical Engineering from the University of Rochester in Rochester, NY in 2018. In the summers of 2018 and 2020, he interned

with the Power Design team at Qualcomm Inc. in San Diego, CA. He is currently completing the Ph.D. degree in electrical engineering from the University of Rochester in Rochester, NY under the supervision of Prof. Eby G. Friedman. His current research interests include graph theory, physical design of integrated circuits, and electronic design automation of conventional and emerging VLSI technologies.

The following publications are a result of work conducted during his doctoral study.

#### Authored book

R. Bairamkulov, E. G. Friedman, "Graph Theory in VLSI," Springer, 2022 (in press).

#### Journal articles

- R. Bairamkulov, T. Jabbari, and E. G. Friedman, "QuCTS single flux Quantum Clock Tree Synthesis," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems* (in press).

- 2. R. Bairamkulov, A. Roy, M. Nagarajan, V. Srinivas, and E. G. Friedman, "SPROUT - Smart Power ROUting Tool for Board-Level Exploration and Prototyping," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems* (in press).

- R. Bairamkulov, K. Xu, M. Popovich, J. S. Ochoa, V. Srinivas, and E. G. Friedman, "Power Delivery Exploration Methodology Based on Constrained Optimization," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, Vol. 39, No. 9, pp. 1916 1924, September 2020.

- 4. R. Bairamkulov and E. G. Friedman, "Effective Resistance of Finite Two-Dimensional Grids Based on Infinity Mirror Technique," *IEEE Transactions* on Circuits and Systems I: Regular Papers, Vol. 67, No. 9, pp. 3224 - 3233, September 2020.

R. Bairamkulov and E. G. Friedman, "Effective Resistance of Two-Dimensional Truncated Infinite Mesh Structures," *IEEE Transactions on Circuits and Systems I: Regular Papers*, Vol. 66, No. 11, pp. 4368 - 4376, November 2019.

#### Conference articles

- R. Bairamkulov, A. Roy, M. Nagarajan, V. Srinivas, and E. G. Friedman, "SPROUT - Smart Power ROUting Tool for Board-Level Exploration and Prototyping," Proceedings of the IEEE/ACM Design Automation Conference, December 2021.

- R. Bairamkulov, A. Roy, M. Nagarajan, V. Srinivas, and E. G. Friedman, "Graph-Based Power Network Routing for Board-Level High Performance Systems," Proceedings of the IEEE International Symposium on Circuits and Systems, October 2020.

- 3. R. Bairamkulov, K. Xu, E. G. Friedman, M. Popovich, J. Ochoa, and V. Srinivas, "Versatile Framework for Power Delivery Exploration," *Proceedings of the IEEE International Symposium on Circuits and Systems*, May 2018.

### Acknowledgments

Like a cutting-edge integrated circuit produced by a combined effort of many people, my development into a multigigahertz high-performance integrated scholar would not be possible without those wonderful people who accompanied me during my journey. I am immensely grateful for being advised and mentored by Professor Eby G. Friedman. He recognized the crystalline structure of my abilities, and with the ultraviolet light of support and enthusiasm shed on the substrate of my curiosity, he etched away my inexperience and confusion and implanted the ions of confidence and maturity. In the controlled pressure environment, he deposited layers of professionalism and meticulousness, and coated with the overglass of stoicism that I will carry through my entire life.

I would like to thank Professor Michael Huang and Professor Selçuk Köse of the Electrical and Computer Engineering Department, Professor Sreepathi Pai and Professor Daniel Štefankovič of the Computer Science Department, and Dr. Abinash Roy of Intel Corp. for providing valuable feedback while serving in my proposal and defense committees. I also thank Professor Chen Ding of the Computer Science Department for serving as a committee chair.

I owe special thanks to Professor Alex Ruderman, who, in the Fall of 2014, recognized a seed of a scholar in me and opened a door into the world of research. I also thank Professor Refik C. Kizilirmak, Professor Yakov Familiant, and Professor Alex P. James for their support during my formative undergraduate years.

My internships and industrial projects with Qualcomm greatly influenced my personal and professional growth. I would like to thank Dr. Mikhail Popovich, Dr. Juan S. Ochoa, Dr. Abinash Roy, Mr. Mahalignam Nagarajan, and Dr. Vaishnav Srinivas for sharing their knowledge and experience during our productive collaboration.

I seize the opportunity to thank the current and graduated members of High Performance Integrated Circuit lab Professor Boris Vaisband, Dr. Albert Çiprut, Dr. Kan Xu, Dr. Gleb Krylov, Abd-Elrahman Qoutb, Tahereh Jabbari, Nurzhan Zhuldassov, Ana Mitrovic, and Andrés Ayes. The uphill struggles of research felt much easier when mixed with our academic and casual conversations. Special appreciation goes to RuthAnn Williams for her support with the administrative tasks and her contagious cheerfulness that she always brings to the lab. I am grateful to our Graduate Coordinator, Michele Foster, for guiding me through the mazes of regulations and to Robert Lindholm for his vital sudo support.

Last but foremost, I am forever grateful to my family for providing the meaning and purpose to this lengthy adventure. I thank my daughter Marie for lighting up my days with her pure sincerity, curiosity, and creativity. And I thank my love and soulmate Zhansaya for bringing color into my world, nurturing my brightest qualities, and being wonderful mother amid the bitter sacrifices of this uneasy journey. I will always be indebted to you for I will not be here without your support.

#### Abstract

The exponential growth in the computational capabilities of humankind cannot be sustained without innovative design methodologies to manage the immense complexity of VLSI systems. To facilitate cooperation across diverse disciplines, the IC design process is composed of multiple abstraction layers. Decomposition of the VLSI process into discrete components enables the automation of manually intractable circuit design tasks. Graph theory plays an important role in electronic design automation (EDA) by providing powerful and versatile algorithms to tackle a variety of VLSI system design issues at each layer of abstraction. In this dissertation, a diverse spectrum of applications of graph theory in the design of VLSI circuits is discussed, ranging from coloring-based register allocation at the register transfer layer to tree-based floorplanning at the physical layer.

Graph-based synthesis of VLSI power and clock distribution networks is emphasized in this dissertation. By exploiting the duality between a random walk within a graph and resistive electrical networks, an efficient algorithm for analyzing arbitrarily

large power grids is proposed. Based on this model, a set of voltage regulators are efficiently distributed within a power grid, drastically improving the power integrity of a synthesized integrated system.

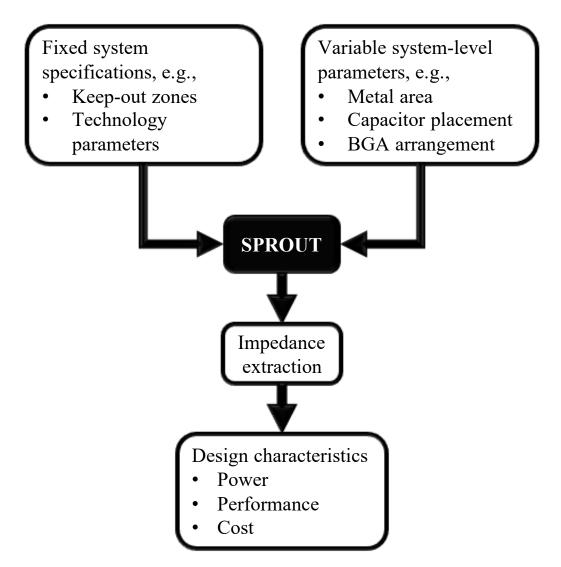

To facilitate the development of power distribution networks at early stages of the system design process, the Smart Power ROUTing (SPROUT) tool for power delivery exploration and prototyping at the board level is proposed. By converting the physical layout of the power network into a graph, prototypical physical layouts of a power network are efficiently created. From an analysis of these prototypes, the power network characteristics can be accurately predicted during early stages of the design process.

Finally, graph theory is applied to synthesize clock distribution network for superconductive single flux quantum (SFQ) integrated circuits. A clock skew scheduling

algorithm, originally developed for CMOS circuits, is adapted to synchronize SFQ

circuits. Based on a schedule of clock arrival times produced for SFQ systems, a

clock tree topology is determined. Using the proposed proxy graph technique, a clock

tree layout based on the clock tree topology is synthesized.

### Contributors and Funding Sources

This work was supervised by a dissertation committee consisting of Professor Eby G. Friedman (advisor), Professor Michael Huang, and Professor Selçuk Köse of the Department of Electrical and Computer Engineering, Professor Sreepathi Pai and Professor Daniel Štefankovič of the Computer Science Department, and Doctor Abinash Roy of Intel Corp. The committee was chaired by Professor Chen Ding of the Computer Science Department. All of the work described in this dissertation was completed by the student.

This research is supported in part by the National Science Foundation under Grant Nos. CCF-1329374, CCF-1526466, CCF-1716091, Intelligence Advanced Research Projects Activity under Grant Nos. W911NF-14-C-0089 and W911NF-17-9-0001, American Institute for Manufacturing Integrated Photonics under Award No. 059447-007, the Intel Collaborative Research Institute for Computational Intelligence, Singapore Ministry of Education Tier 2 under Grant No. MOE2014-T2-2-105, and grants from Cisco Systems, Google, OeC, Qualcomm, and Synopsys.

# List of Tables

| 3.1 | Typical capacity and latency (in 2019) at different levels of the memory      |     |

|-----|-------------------------------------------------------------------------------|-----|

|     | hierarchy [211]                                                               | 108 |

| 6.1 | Exact normalized resistance between $(0, y_0)$ and $(x, y)$ in a half-plane   |     |

|     | resistive grid with $y \in [-3,3], x \in [0,3],$ and $r_h = r_y = r$ . The    |     |

|     | numerical values are within the square brackets                               | 313 |

| 6.2 | Coefficients for the polynomial approximation of $J_3$ (6.32)                 | 317 |

| 6.3 | Computational speedup for determining the effective resistance be-            |     |

|     | tween a pair of nodes in an $M \times N$ grid                                 | 325 |

| 7.1 | Summands of (7.12) for $(x_0, y_0) = (0, 0)$ and $(x, y) = (0, 1)$ in a 2 × 2 |     |

|     | resistive grid                                                                | 343 |

| 7.2 | Coefficients for the polynomial approximation of $J_3$ (7.19) [462]           | 347 |

| 7.3 | Parameters for substrate noise evaluation                                     | 355 |

| 8.1 | Comparison of major types of on-chip converters                               | 366 |

| 8.2  | Parameters of the equivalent grids used to model the ibmpg bench-      |     |

|------|------------------------------------------------------------------------|-----|

|      | marks [505]                                                            | 372 |

| 8.3  | Summary of the voltage regulator distribution within the ibmpg bench-  |     |

|      | marks. The results of case two greatly depend on the particular geom-  |     |

|      | etry of restricted placement and are therefore omitted from this table |     |

|      |                                                                        | 387 |

| 9.1  | Parameters of decoupling capacitor cost                                | 413 |

| 9.2  | Optimization constraints, with initial and optimal parameters          | 417 |

| 9.3  | Voltage domain specifications of power delivery network adapted from   |     |

|      | [545]                                                                  | 419 |

| 10.1 | Comparison of normalized impedance between SPROUT and manual           |     |

|      | routing for the two rail system shown in Fig. 10.9                     | 454 |

| 10.2 | Comparison of normalized impedance between SPROUT and manual           |     |

|      | routing for the six rail system shown in Fig. 10.10                    | 456 |

| 10.3 | Target area of the test layouts for exploring area impedance tradeoffs | 458 |

| 11.1 | Performance of QuCTS applied to AMD2901, ITC99, and ISCAS89            |     |

|      | benchmark circuits with high gate count                                | 496 |

# List of Figures

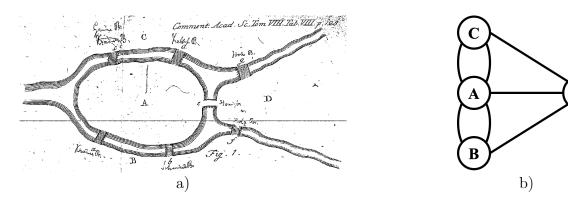

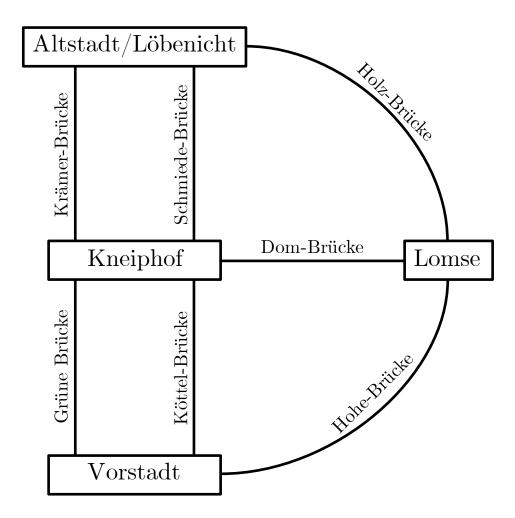

| 1.1 | Seven Bridges of Königsberg problem. a) Simplified map of Königsberg          |   |

|-----|-------------------------------------------------------------------------------|---|

|     | bridges as drawn by Euler in [4], and b) equivalent multigraph repre-         |   |

|     | sentation.                                                                    | 2 |

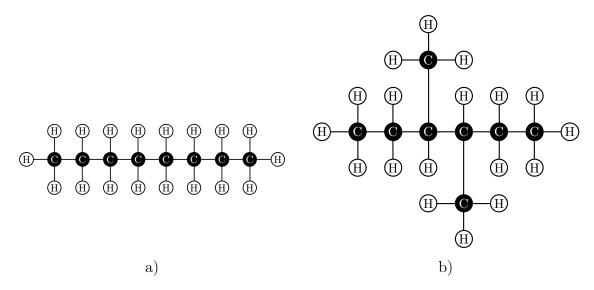

| 1.2 | Earliest application of graphs is in chemical notation. The figures           |   |

|     | illustrate the difference between $C_8H_{18}$ isotopes [7], a) octane, and b) |   |

|     | 3 4-dimethylhexane                                                            | 4 |

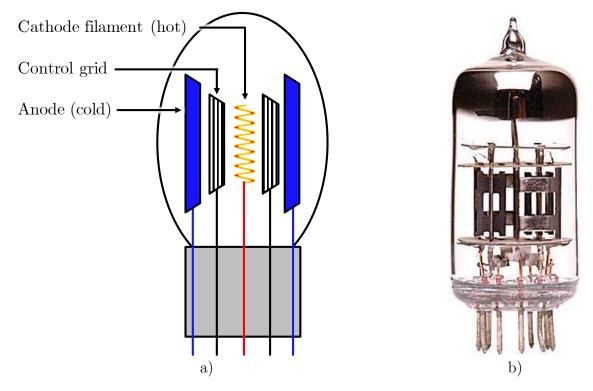

- 1.4 Vacuum tube. a) Internal structure of a vacuum tube. The cathode filament is heated inducing thermionic emission [14]. The electrons emitted from the cathode are captured by the cold anode. The grid is placed between the anode and cathode to control the output current. Without the grid, the vacuum tube behaves as a diode. b) Solen Électronique SI-12AX7B vacuum tube [16]. The thick vertical wire at the center of the tube is a filament cathode. The filament is surrounded by several anode plates capturing electrons emitted by the filament.

7

6

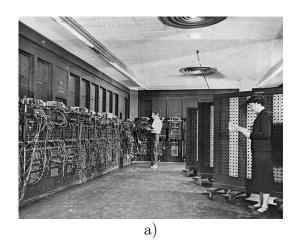

| 1.5 | Electronic Numerical Integrator and Computer (ENIAC) built in 1945       |    |

|-----|--------------------------------------------------------------------------|----|

|     | using 18,000 vacuum tubes. The operating frequency of the ENIAC was      |    |

|     | 100 kilohertz, producing 5,000 operations per second. a) The ENIAC       |    |

|     | occupied more than 167 square meters and consumed more than 150          |    |

|     | kilowatts [19]. b) The reliability of the ENIAC was poor due to the      |    |

|     | large number of vacuum tubes that occasionally burnt out. Locating       |    |

|     | and replacing the broken tubes required significant time and effort      | 8  |

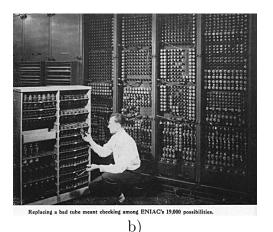

| 1.6 | Manual layout of an integrated system during the pre-CAD/EDA era.        |    |

|     | a) An interconnect pattern of a logic circuit scaled by a factor of 250, |    |

|     | manually drawn with pencil on a routing grid [42]. b) Visual inspection  |    |

|     | of the resulting layout [42]                                             | 12 |

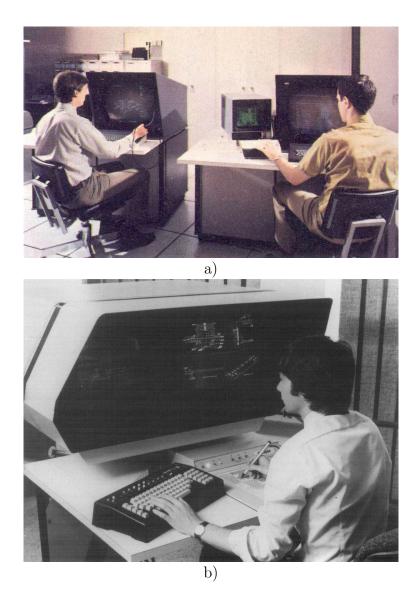

| 1.7 | Workstations used during the development of integrated systems dur-      |    |

|     | ing the early years of CAD/EDA. a) Two workstations used in Texas        |    |

|     | Instruments circa 1970 [43]. The left workstation, used for schematic    |    |

|     | design, is equipped with a large interactive screen and stylus. The      |    |

|     | right workstation is used for layout drawing and is equipped with a      |    |

|     | large interactive screen and a small additional display. b) IC design    |    |

|     | workstation during the mid-1980's used to generated the layout of an     |    |

|     | IC [44]                                                                  | 13 |

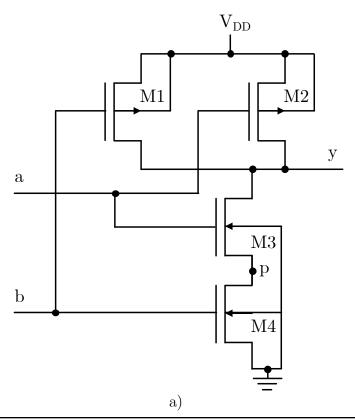

| 1.8 | Example of a two input NAND gate in SPICE using four transistors.            |    |

|-----|------------------------------------------------------------------------------|----|

|     | a) Initial schematic representation. b) Circuit in SPICE format. Each        |    |

|     | line encodes the type and name of the component (e.g., M1 describes          |    |

|     | a transistor with name '1'), connection to other nodes (e.g., M1 is          |    |

|     | connected to nodes $y$ , $a$ , and $vdd$ ), and model parameters such as the |    |

|     | channel dimensions (length and width)                                        | 15 |

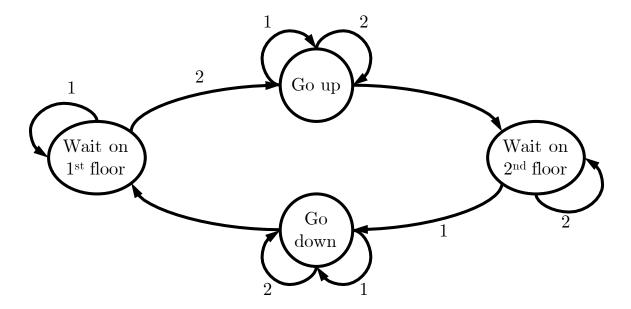

| 1.9 | An example of a finite state machine [62], [63] representing a two floor     |    |

|     | elevator. The nodes represent the four states of the system, $i.e.$ , wait   |    |

|     | on the first or second floor, go up, or go down. The edges represent         |    |

|     | the transition between the states. The edge labels 1 and 2 denote the        |    |

|     | events of pressing button 1 and 2 in an elevator. These events trigger       |    |

|     | the transition of an elevator to the next state. The loops (edges starting   |    |

|     | and ending at the same node) indicate events that do not change the          |    |

|     | state of the system.                                                         | 17 |

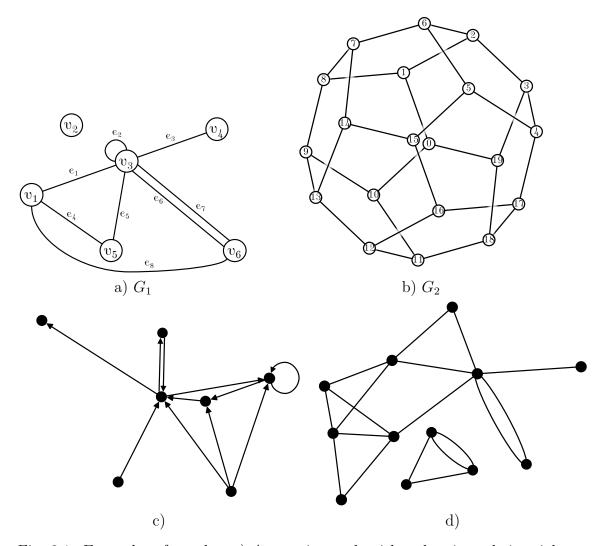

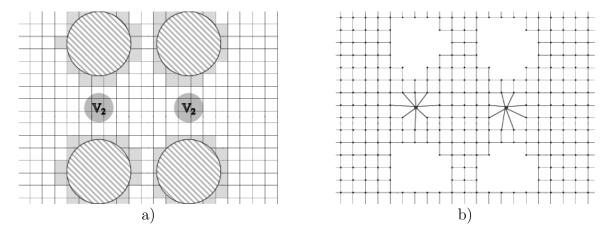

| 2.1 | Examples of graphs. a) A generic graph with order six and size eight.                   |    |

|-----|-----------------------------------------------------------------------------------------|----|

|     | $v_2$ is an isolated node with degree zero. Edge $e_1$ is the link connecting           |    |

|     | two distinct nodes. Edge $e_2$ is the loop connecting node $v_3$ with itself.           |    |

|     | $e_6$ and $e_7$ are parallel edges connecting the same pair of nodes, $v_3$ and $v_6$ . |    |

|     | b) Dodecahedral graph. The nodes and edges represent, respectively,                     |    |

|     | the vertices and edges of a regular dodecahedron (platonic solid). c)                   |    |

|     | Directed graph with self-loops, and d) undirected multigraph                            | 26 |

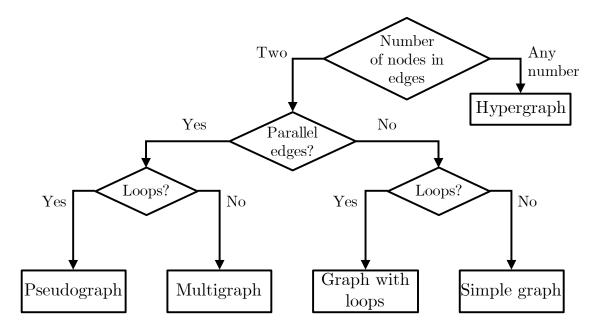

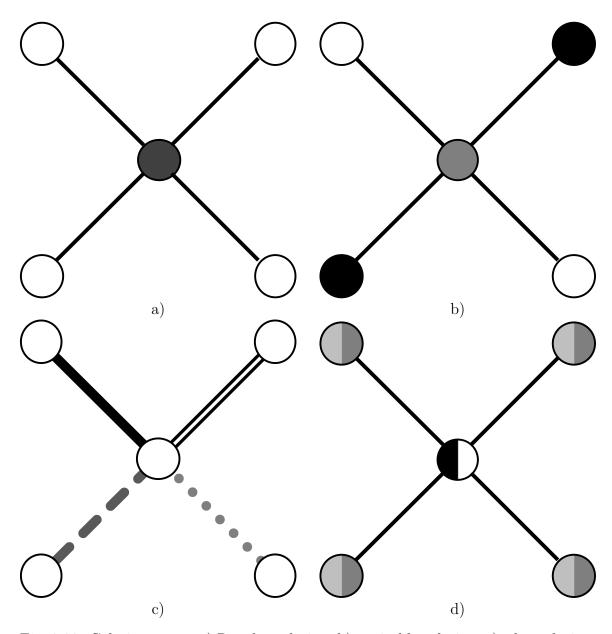

| 2.2 | Topological classification of a graph. A hypergraph is a superclass of                  |    |

|     | graphs where the edges can connect an arbitrary number of nodes.                        |    |

|     | Only two nodes (not necessarily distinct) can be connected with an                      |    |

|     | edge in a graph. Depending on whether parallel edges and loops exist,                   |    |

|     | a graph can be classified as a pseudograph, multigraph, graph with                      |    |

|     | loops, or simple graph.                                                                 | 27 |

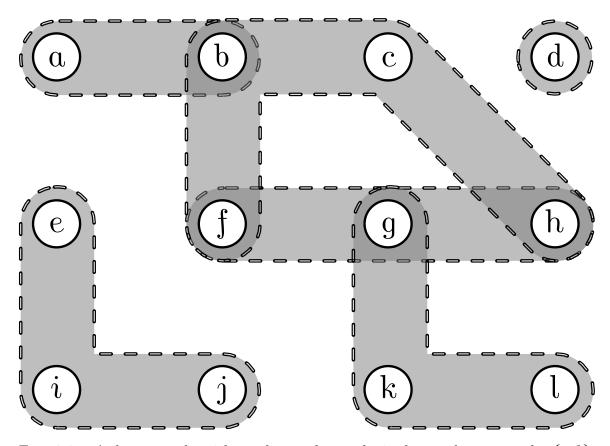

| 2.3 | A hypergraph with twelve nodes and six hyperedges, namely $\{a,b\}$ ,                   |    |

|     | $\{b, c, f, h\}, \{d\}, \{e, i, j\}, \{f, g, h\}, \text{ and } \{j, k, l\}.$            | 29 |

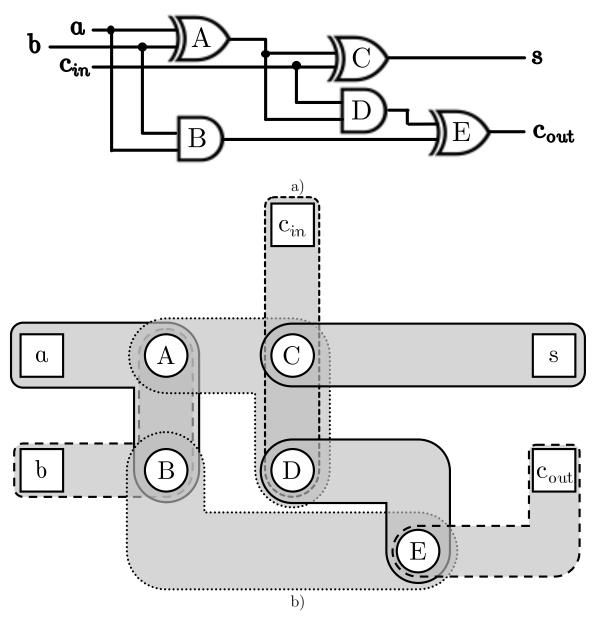

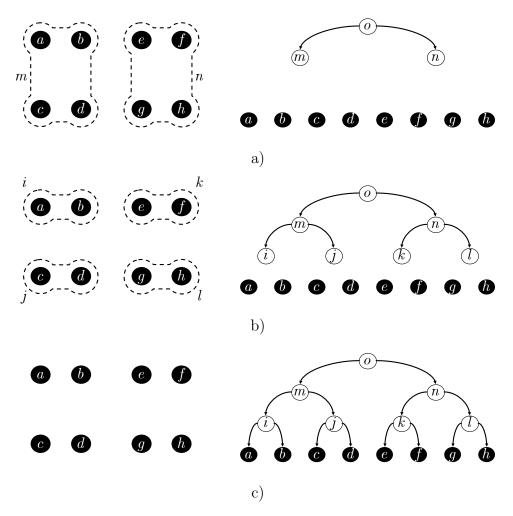

| 2.4 | A logic circuit converted into a hypergraph. a) The initial circuit.                    |    |

|     | Observe the wires connecting more than two gates. b) Equivalent hy-                     |    |

|     | pergraph. The nodes represent the gates and terminals. Nine hyper-                      |    |

|     | edges exist within the hypergraph, representing the wires connecting                    |    |

|     | the gates.                                                                              | 30 |

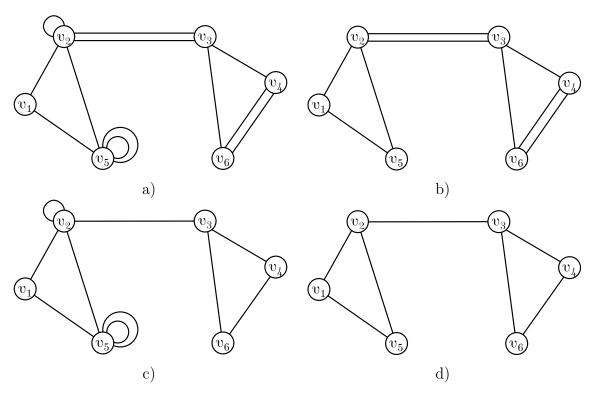

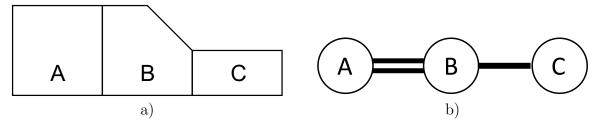

| 2.5 | Topological classes of a graph. a) A pseudograph with two pairs of           |    |

|-----|------------------------------------------------------------------------------|----|

|     | parallel links, and three loops, two loops of which are parallel loops.      |    |

|     | b) a multigraph with two pairs of parallel links, c) a graph with three      |    |

|     | loops and no parallel edges, and d) a simple graph with no parallel          |    |

|     | edges and no loops                                                           | 32 |

| 2.6 | A multigraph representing the seven bridges of Königsberg [4]. Four          |    |

|     | landmasses, represented by rectangles, are connected by seven bridges,       |    |

|     | represented by edges. Two pairs of parallel edges are formed by bridges,     |    |

|     | Krämer and Schmiede, and Grüne and Kötten                                    | 33 |

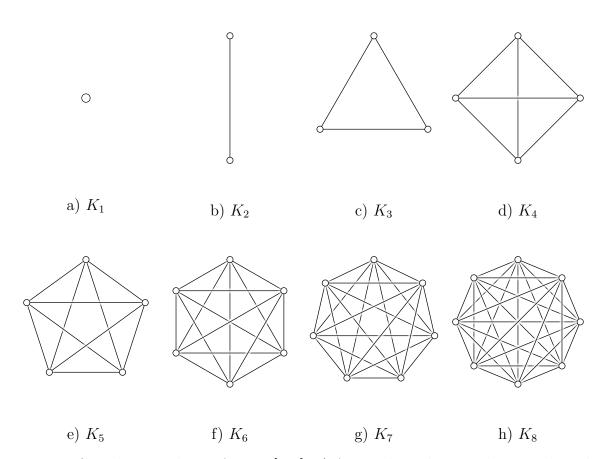

| 2.7 | Complete graphs $K_n$ for $n \in [1, 8]$ . a) A trivial graph $K_1$ with one |    |

|     | node and no edges, b) a line graph $K_2$ with two nodes and one edge,        |    |

|     | c) a smallest cycle graph $K_3$ with three nodes and three edges, d)         |    |

|     | tetrahedral graph $K_4$ with four nodes and six edges, e) $K_5$ with five    |    |

|     | nodes and ten edges, f) $K_6$ with six nodes and 15 edges, g) $K_7$ with     |    |

|     | seven nodes and 21 edges, and h) $K_8$ with seven nodes and 28 edges.        | 35 |

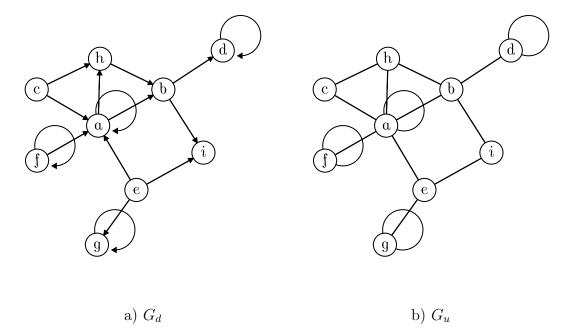

| 2.8 | An example of a graph orientation and the underlying graph. a) Di-           |    |

|     | rected graph $G_d$ , and b) underlying graph $G_u$                           | 38 |

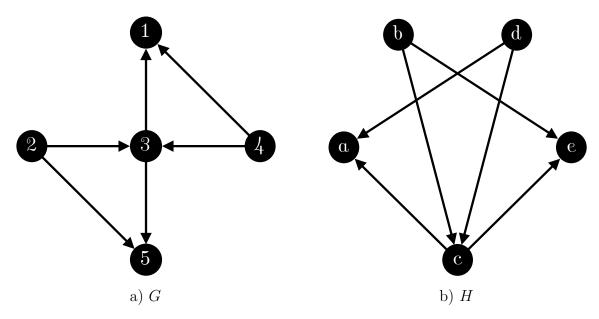

| 2.9  | Isomorphic graphs; a) $G$ and b) $H$ . Map $f: [1 \to a,, 5 \to e]$ is          |      |

|------|---------------------------------------------------------------------------------|------|

|      | the isomorphism of graphs $G$ and $H$ , since for any edge $(u, v) \in E_G$ , a |      |

|      | unique edge $(f(u), f(v)) \in E_H$ exists. For example, edge $(4, 1) \in E_G$   |      |

|      | is mapped to edge $(d, a) \in E_H$                                              | 40   |

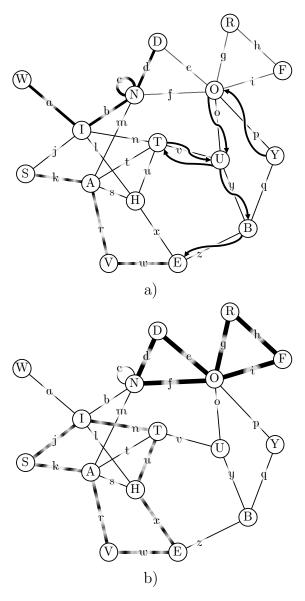

| 2.10 | Examples of walks within a graph. a) The generic walk $W_1 = YpOoUvTvU$         | yBzE |

|      | is shown with wavy arrows. Nodes $Y$ and $E$ are, respectively, the origin      |      |

|      | and terminus of $W_1$ . Node $U$ and edge $v$ are repeated twice during the     |      |

|      | walk. Walk $W_2 = WaIbNcNdD$ is the trail (solid thick lines), since            |      |

|      | none of the edges is repeated. Walk $W_3 = SkArVwE$ is a path, since            |      |

|      | none of the nodes is repeated. Observe that path $W_3$ is also a trail. b)      |      |

|      | Walk $W_4 = OeDdNfOgRhFiO$ is a circuit since the origin and termi-             |      |

|      | nus of $W_4$ is the same node (O). Walk $W_5 = SjInTuHxEwVrAkS$ is              |      |

|      | a cycle since $W_5$ is a circuit with no repeated nodes                         | 42   |

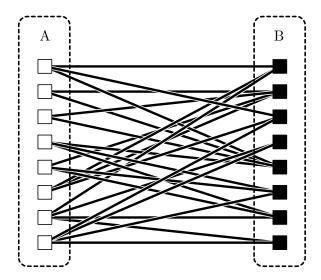

| 2.11 | A bipartite graph consisting of sets $A$ and $B$ . All edges include one        |      |

|      | endpoint in $A$ and another endpoint in $B$ . None of the edges connects        |      |

|      | the nodes within the same partition                                             | 43   |

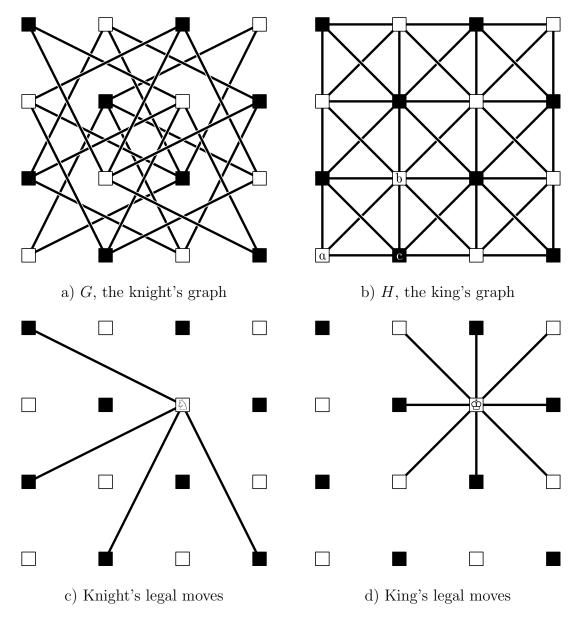

| 2.12 | Examples of bipartite and non-bipartite graphs. a) Knight's graph.          |    |

|------|-----------------------------------------------------------------------------|----|

|      | The nodes and edges represent, respectively, the chessboard squares         |    |

|      | and valid knight's moves. b) King's graph. The edges represent valid        |    |

|      | king's moves within the chessboard. c) Valid moves of a knight, and         |    |

|      | d) valid moves of a king.                                                   | 45 |

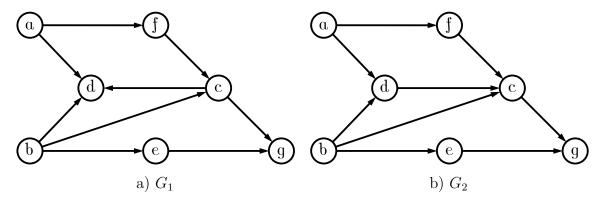

| 2.13 | Directed graphs with and without directed cycles. a) Directed graph         |    |

|      | $G_1$ with cycles $[a,b,d,c]$ and $[e,c,d]$ , and b) directed acyclic graph |    |

|      | (DAG) $G_2$                                                                 | 46 |

| 2.14 | Topological orderings of DAG $G_2$ (see Fig. 2.13b). In topological         |    |

|      | ordering, any ancestor of node $u$ in a DAG appears before $u$ , while the  |    |

|      | descendants of $u$ appear after $u$                                         | 47 |

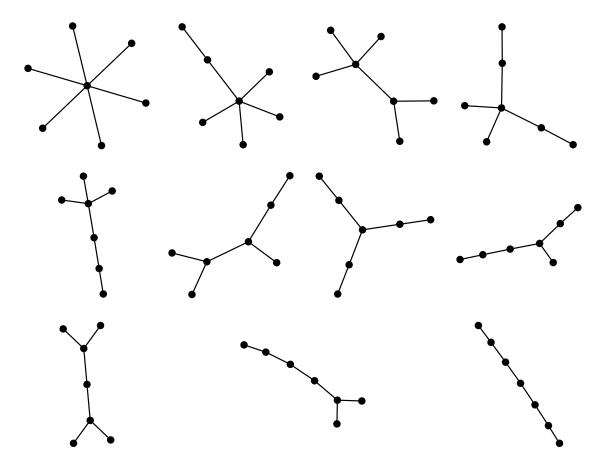

| 2.15 | Eleven possible non-isomorphic trees with seven nodes                       | 47 |

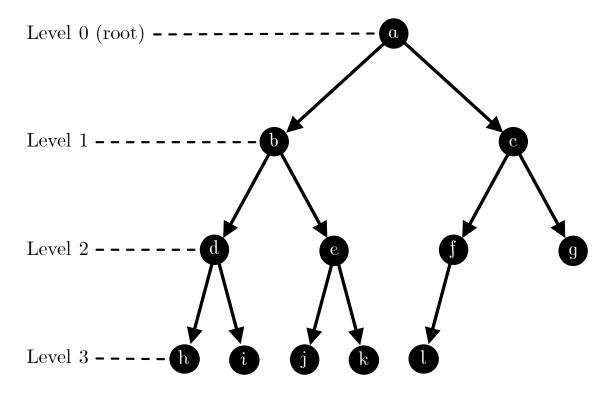

| 2.16 | An example of a complete balanced rooted tree with height $h=3.a$           |    |

|      | is the root node. All edges are oriented away from the root                 | 48 |

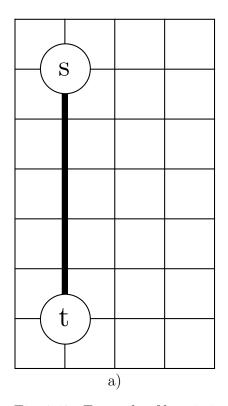

| 2.17 | Example of heuristics in graph pathfinding. a) Path finding in a grid       |    |

|      | graph. To determine the shortest path, the Euclidean distance from          |    |

|      | the target node is used as a heuristic. The shortest path between nodes     |    |

|      | s and $t$ is efficiently determined by traversing only five edges. b) With  |    |

|      | the same heuristic, a suboptimal path is found due to the presence of       |    |

|      | an obstacle                                                                 | 51 |

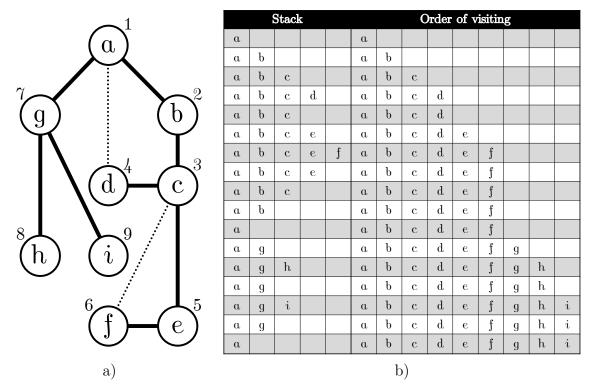

| 2.18 | An example of Depth-First Search (DFS). a) The traversed graph.              |    |

|------|------------------------------------------------------------------------------|----|

|      | The numbers indicate the order of traversal. The thick solid and thin        |    |

|      | dashed lines denote the traversed and non-traversed edges. b) DFS            |    |

|      | using a stack data structure. Unvisited neighbors of the top (rightmost)     |    |

|      | node in the stack are traversed. The new nodes are placed at the top         |    |

|      | of the stack (right), i.e., the neighborhood of the nodes added last are     |    |

|      | traversed first. Once all of the neighbors of a node are visited, the node   |    |

|      | is removed from the stack. The algorithm is terminated after the last        |    |

|      | entry is removed                                                             | 54 |

| 2.19 | Basic stack operations. An element is placed on top of the stack by          |    |

|      | using a push operation. The top element is removed from the stack by         |    |

|      | using a pop operation. This data structure is commonly called Last-In,       |    |

|      | First-Out (LIFO), where the last added element is removed first              | 55 |

| 2.20 | Basic queue operations. An element is placed at the end of the queue         |    |

|      | with the enqueue operation, denoted here as E. The first (top) element       |    |

|      | is removed from the stack with the <b>dequeue</b> operation, denoted here as |    |

|      | D. This data structure is commonly called First-In, First-Out (FIFO),        |    |

|      | where the last added element is removed last                                 | 57 |

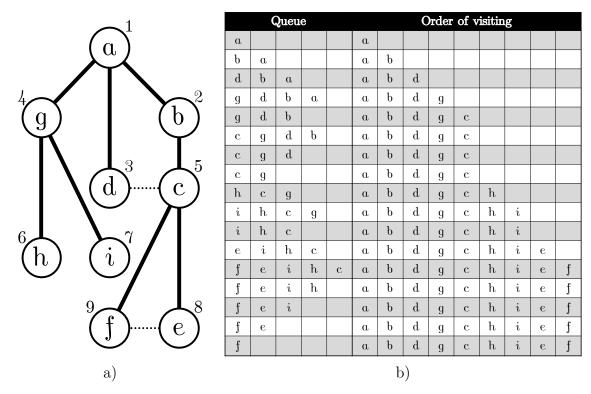

| 2.21 | An example of Breadth-First Search (BFS). a) The traversed graph.         |    |

|------|---------------------------------------------------------------------------|----|

|      | The numbers indicate the order of traversal. The thick solid and thin     |    |

|      | dashed lines denote the traversed and non-traversed edges. b) BFS         |    |

|      | using a queue data structure (First-In, First-Out, FIFO). Unvisited       |    |

|      | neighbors of the rightmost node in the queue are traversed. New nodes     |    |

|      | are placed at the (left) end of the queue. Once all of the neighbors of a |    |

|      | node are visited, the node is removed from the queue. The algorithm       |    |

|      | is terminated after the last entry is removed                             | 58 |

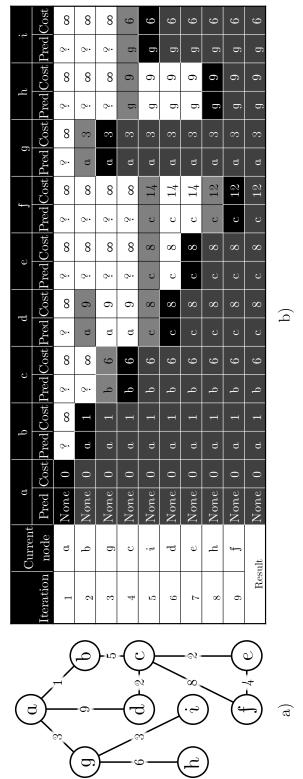

| 2.22 | An example of the Dijkstra's algorithm. a) The traversed graph. The       |    |

|      | numbers indicate the edge weights. b) Order of traversal. During each     |    |

|      | iteration, the neighborhood of a current node is explored. If a shorter   |    |

|      | path is determined, the cost and predecessor of a node are updated,       |    |

|      | as shown in light gray in the table. The node with the smallest cost is   |    |

|      | selected as the current node, and the cost of this node is not changed    |    |

|      | in subsequent iterations                                                  | 59 |

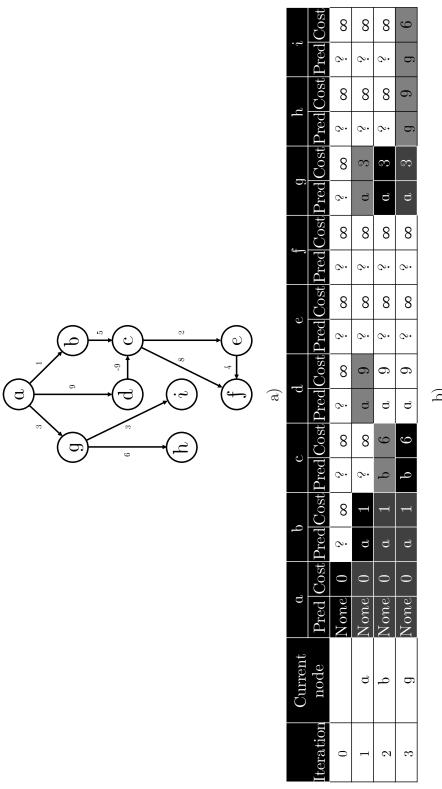

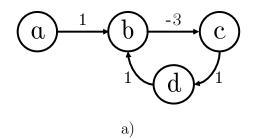

| 2.23 | An example of an incorrect result by the Dijkstra's algorithm in a graph  |    |

|------|---------------------------------------------------------------------------|----|

|      | with negative edges. a) The traversed graph. The numbers indicate         |    |

|      | the edge weight. b) Order of traversal. The first three iterations of the |    |

|      | algorithm. In the third iteration, the Dijkstra's algorithm determines    |    |

|      | an incorrect shortest path to node $c$ via node $b$ with cost 6. The node |    |

|      | c can however be reached with cost 0 by traveling via node $d$            | 62 |

| 2.24 | An example of the Bellman-Ford algorithm applied to the graph de-         |    |

|      | picted in Fig. 2.23. During each iteration, each edge is evaluated to     |    |

|      | update the predecessor and cost of reaching the head of the edge. If      |    |

|      | no cost is updated during an iteration, the algorithm is terminated       | 64 |

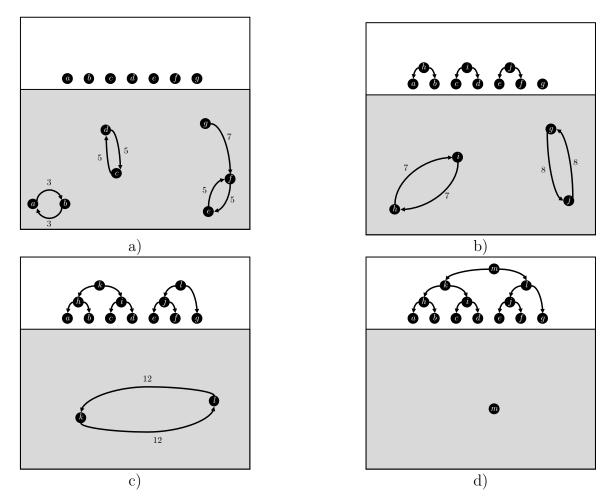

| 2.25 | The Bellman-Ford algorithm applied to a graph with a negative cycle.      |    |

|      | a) A graph with a negative cycle. The sum of weights along the path       |    |

|      | [b,c,d] is $-1$ . b) The BF algorithm. The maximum expected number        |    |

|      | of iterations is $ V  - 1 = 3$ . An update of the cost during the fourth  |    |

|      | iteration indicates the presence of a negative cycle which triggers the   |    |

|      | termination of an algorithm.                                              | 65 |

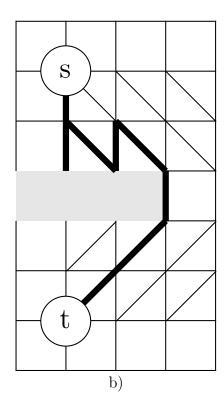

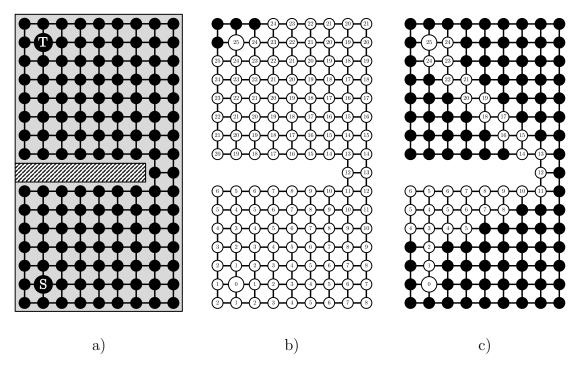

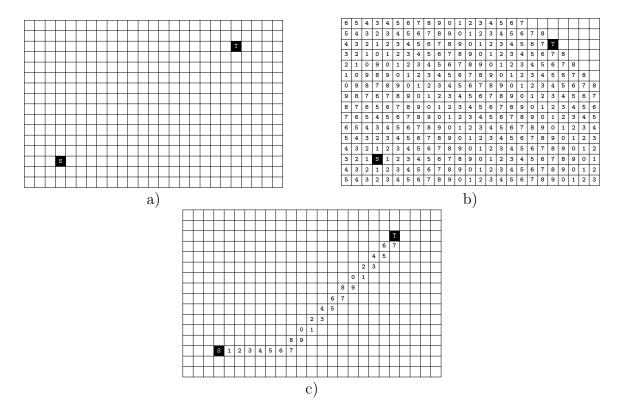

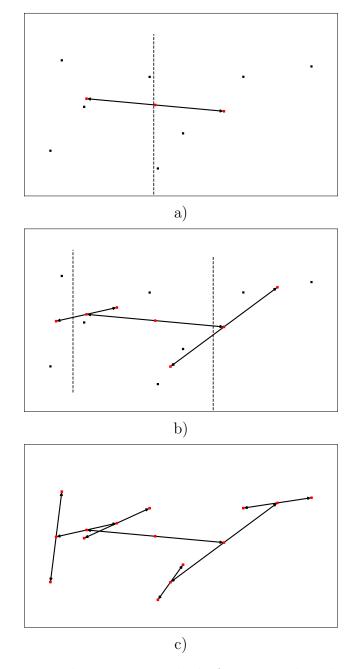

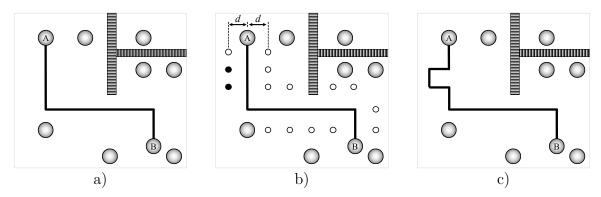

| 2.26 | Finding a path within a two-dimensional layout. a) Initial layout mod-               |    |

|------|--------------------------------------------------------------------------------------|----|

|      | eled as a grid graph. b) Path finding using the Dijkstra's algorithm.                |    |

|      | The hollow nodes denote traversed nodes. The numbers indicate the                    |    |

|      | distance from the source. c) Path finding using the A* algorithm. The                |    |

|      | Euclidean distance from the target is used to determine the direction                |    |

|      | for traversal. Significantly fewer nodes are therefore traversed using               |    |

|      | the A* algorithm.                                                                    | 67 |

| 2.27 | All 16 possible spanning trees for a complete graph $K_4$                            | 69 |

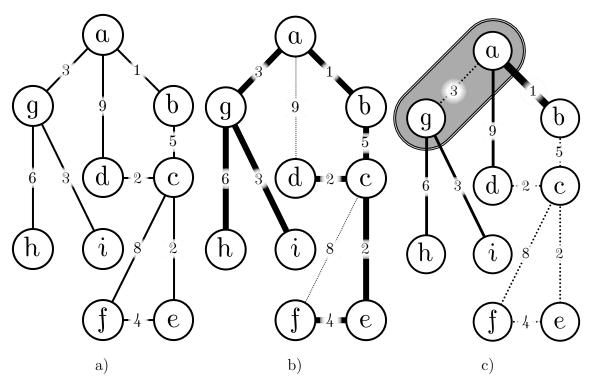

| 2.28 | Minimum spanning tree (MST) of a weighted graph. a) Original graph.                  |    |

|      | The numbers indicate the edge weights. b) Corresponding MST. The                     |    |

|      | bold lines denote the edges included within a MST. c) A set of external              |    |

|      | edges $E_s^{ext}$ (solid edges) for terminals $S=\{a,g\}$ . The edges in $E_s^{ext}$ |    |

|      | connect a and g with other nodes. The edge $e_{min}(G, S) = \{a, b\}$ is the         |    |

|      | minimum-weight external edge with weight 1                                           | 70 |

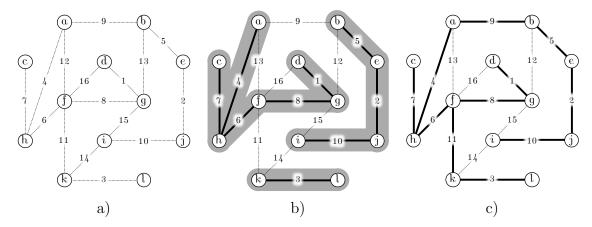

| 2.29 | The Borůvka's algorithm for finding a MST. a) Initial graph. Each                    |    |

|      | node is considered a component. b) Graph components after the first                  |    |

|      | iteration. Three components are determined. c) Final MST                             | 72 |

| 2.30 | Progress of the Prim's algorithm applied to the graph shown in Fig.                       |    |

|------|-------------------------------------------------------------------------------------------|----|

|      | 2.29a. Node $a$ is used as the initial component. The minimum-weight                      |    |

|      | external edge is used to determine which node is added to the compo-                      |    |

|      | nent                                                                                      | 74 |

| 2.31 | Progress of the Kruskal's algorithm applied to the graph shown in                         |    |

|      | Fig. 2.29a. The MST is constructed by iteratively adding edges with                       |    |

|      | minimum weight while avoiding cycles. The column $\mathit{Min}$ $\mathit{edge}$ lists the |    |

|      | edges with minimum weight added to the MST. The edges that could                          |    |

|      | not be added to the MST so as not to create cycles are listed in column                   |    |

|      | Skipped                                                                                   | 76 |

| 2.32 | Example of contractible subgraph. a) Initial graph. Edges belonging            |    |

|------|--------------------------------------------------------------------------------|----|

|      | to MST are depicted with solid lines, and the remaining edges are              |    |

|      | depicted with dotted lines. Two subgraphs, $G_1$ and $G_2$ , are considered    |    |

|      | in this example with node sets, respectively, $V_1 = f, h, k, l$ and $V_2 =$   |    |

|      | $b, e, g$ . b) Contraction of subgraph $G_1$ . Those edges whose endpoints     |    |

|      | are both in $V_1$ are discarded. The nodes in $V_1$ are combined into a single |    |

|      | node. Edges incident to nodes in $V_1$ are incident to the combined node       |    |

|      | fhkl after contraction. The tree structure is retained after contraction.      |    |

|      | Subgraph $G_1$ is therefore contractible. c) Contraction of subgraph           |    |

|      | $G_2$ . Cycles within a MST are produced during the contraction (e.g.,         |    |

|      | $(beg, i, j)$ ). Subgraph $G_2$ is therefore not contractible                  | 78 |

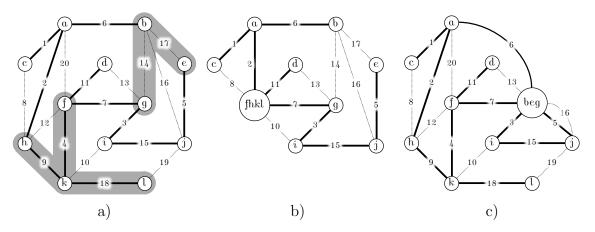

| 2.33 | Example of a Steiner minimum tree (SMT). a) Initial graph. All edges           |    |

|      | have equal weight. The solid circles denote the terminal nodes. b)             |    |

|      | The SMT utilizes two Steiner nodes. The bold lines denote the edges            |    |

|      | belonging to a SMT                                                             | 79 |

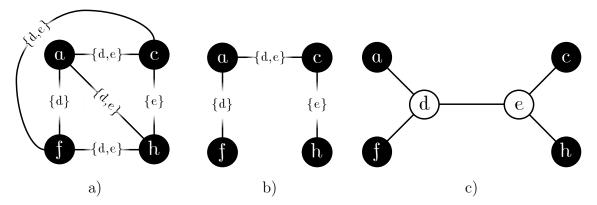

| 2.34 | Construction of a Steiner Minimum tree (SMT) by metric closure of            |    |

|------|------------------------------------------------------------------------------|----|

|      | the graph. a) Subgraph of the metric closure of the graph shown in Fig.      |    |

|      | 2.33a induced by the set of terminals $S = \{a, c, f, h\}$ . The nodes along |    |

|      | a shortest path are shown in curly brackets. b) The MST of the metric        |    |

|      | closure. c) SMT constructed from the MST. Note that the algorithm            |    |

|      | is an approximation of the SMT and does not guarantee optimality.            | 80 |

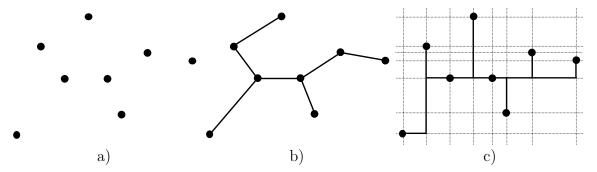

| 2.35 | Construction of a SMT within a planar space. a) Initial arrangement          |    |

|      | of points. b) Euclidean SMT. c) Manhattan SMT constructed using a            |    |

|      | Hanan grid                                                                   | 82 |

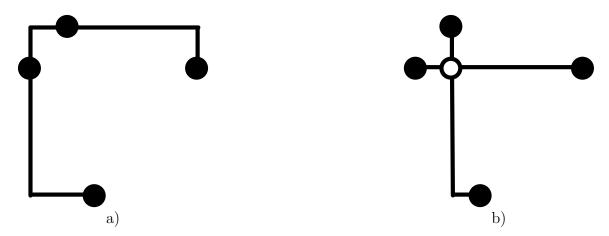

| 2.36 | Insertion of a 1-Steiner point. a) Minimum spanning tree. Solid circles      |    |

|      | denote terminals. b) Steiner tree after addition of a 1-Steiner point        |    |

|      | (hollow circle). The total length of a tree is reduced by 17.3%. $$          | 83 |

| 2.37 | Length-Restricted Steiner Minimum Tree (LRSMT) construction. a)              |    |

|      | Minimum length tree. The distance from the main terminal node (hol-          |    |

|      | low circle) to other terminals is unbalanced. b) LRSMT. The difference       |    |

|      | in distance from the main terminal node is reduced                           | 84 |

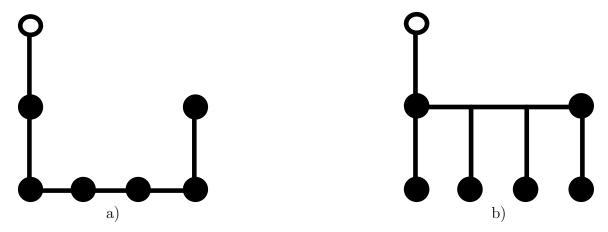

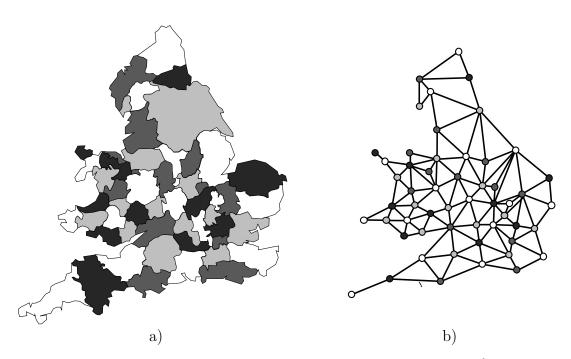

| 2.38 | Four color theorem originated in the middle of the 19 <sup>th</sup> century when |    |

|------|----------------------------------------------------------------------------------|----|

|      | Francis Guthrie noted that only four colors are sufficient when coloring         |    |

|      | the map of England. a) Map of contiguous English counties colored                |    |

|      | using four colors, and b) an equivalent graph. The nodes represent the           |    |

|      | counties, and the edges connect adjacent regions                                 | 85 |

| 2.39 | Coloring types. a) Regular coloring, b) equitable coloring, c) edge              |    |

|      | coloring, and d) fractional coloring.                                            | 88 |

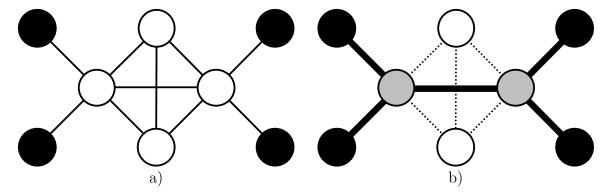

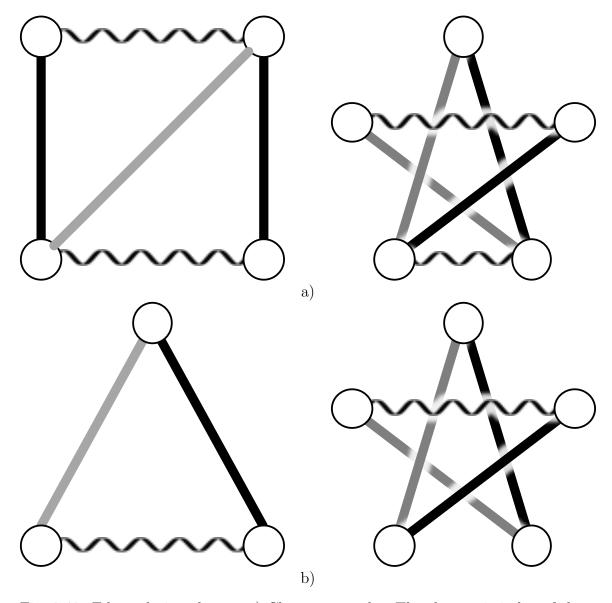

| 2.40 | Edge coloring classes. a) Class one graphs. The chromatic index of               |    |

|      | these graphs is equal to $\Delta$ , the maximum degree of any node within a      |    |

|      | graph. b) Class two graphs. The chromatic index of these graphs is               |    |

|      | $\Delta + 1$                                                                     | 89 |

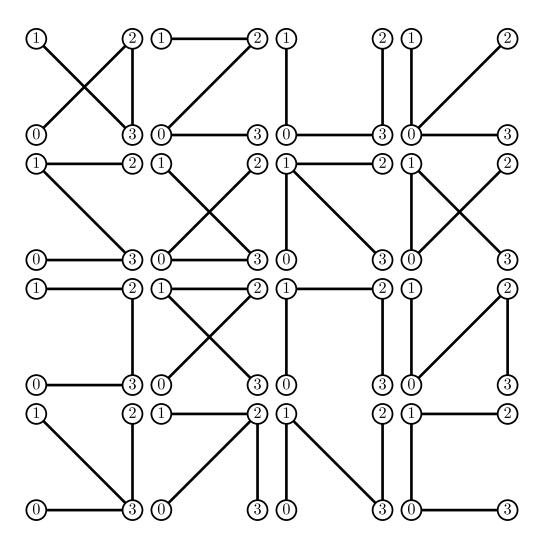

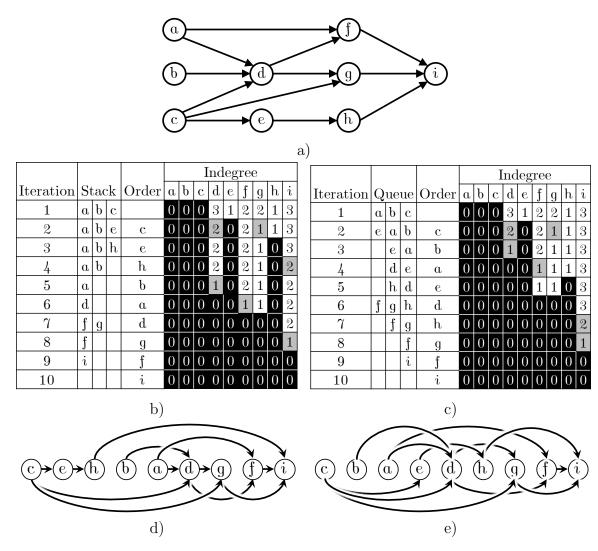

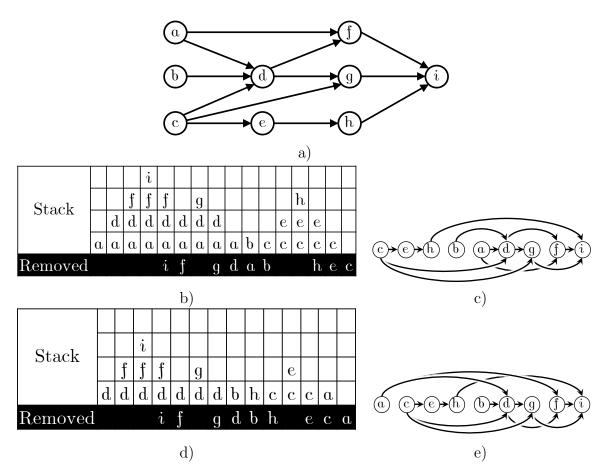

| 2.41 | Topological ordering using the Kahn's algorithm. a) An example DAG.              |    |

|      | b) Stack-based Kahn's algorithm. During each iteration, nodes with               |    |

|      | zero indegree are placed into the stack. The top node $u$ is removed             |    |

|      | from the stack, and the indegree of the successors is decremented. The           |    |

|      | process repeats until the stack is empty. c) Queue-based Kahn's algo-            |    |

|      | rithm. The process is identical to the stack-based Kahn's algorithm              |    |

|      | except the order of processing the zero-degree nodes. d) Result of the           |    |

|      | stack-based Kahn's algorithm, and e) result of the queue-based Kahn's            |    |

|      | algorithm                                                                        | 91 |

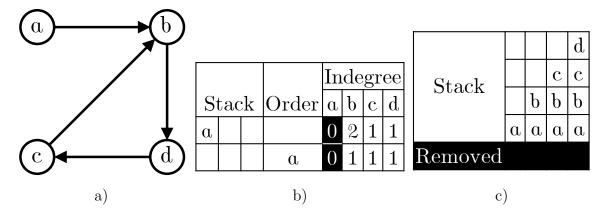

| 2.42 | Topological sorting applied to a connected graph with a directed cycle.         |    |

|------|---------------------------------------------------------------------------------|----|

|      | a) Connected graph with cycle $[b,c,d,b]$ . b) The stack-based Kahn's           |    |

|      | algorithm. After removing node $a$ from the stack, none of the indegrees        |    |

|      | is decremented to zero. The algorithm terminates before processing all          |    |

|      | of the nodes, indicating the presence of a cycle. An identical result           |    |

|      | is achieved with the queue-based Kahn's algorithm. c) DFS based                 |    |

|      | sorting. No inherent cycle detection exists in DFS. The nodes within            |    |

|      | the stack $(i.e., added but not yet removed)$ are marked. If a marked           |    |

|      | node is encountered during DFS, the cycle exists within the graph. In           |    |

|      | this example, upon reaching node $d$ , node $b$ is detected. Since node         |    |

|      | b is marked (i.e., within the stack), a cycle containing $b$ and $d$ exists     |    |

|      | within the graph.                                                               | 92 |

| 2.43 | Topological ordering using DFS. a) An example DAG. b) DFS starting              |    |

|      | from nodes $a$ , $b$ , and $c$ , and $c$ ) the resulting ordering. The ordering |    |

|      | is obtained by reversing the order of removal from the stack. This              |    |

|      | ordering is coincidentally identical to the ordering obtained using the         |    |

|      | queue-based Kahn's algorithm. d) DFS starting from nodes $d,\ b,\ h,$           |    |

|      | c, and $a$ , and $e$ ) the resulting ordering. Note that a valid ordering is    |    |

|      | obtained despite starting from nodes with nonzero indegree                      | 94 |

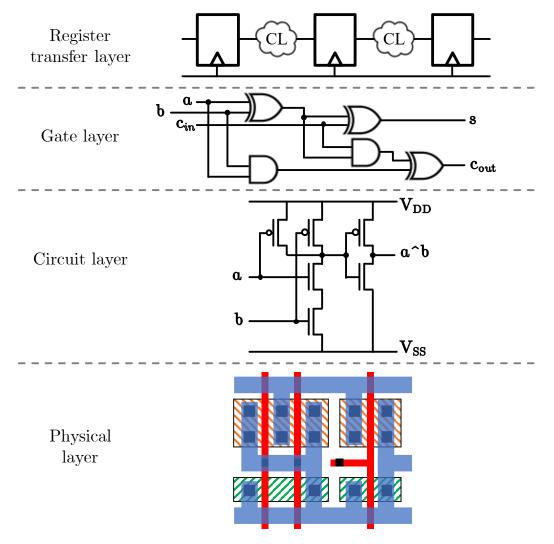

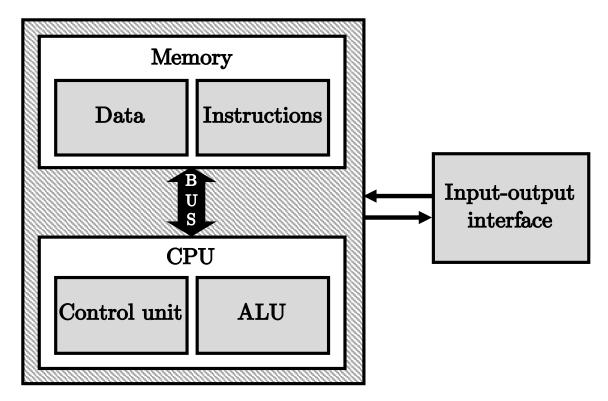

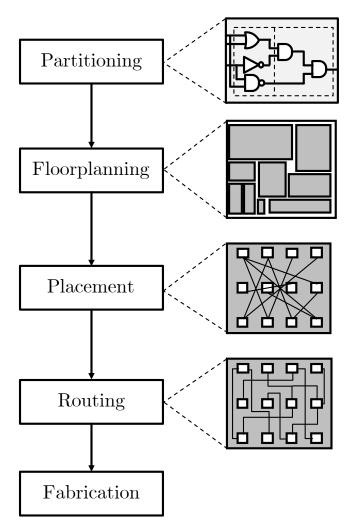

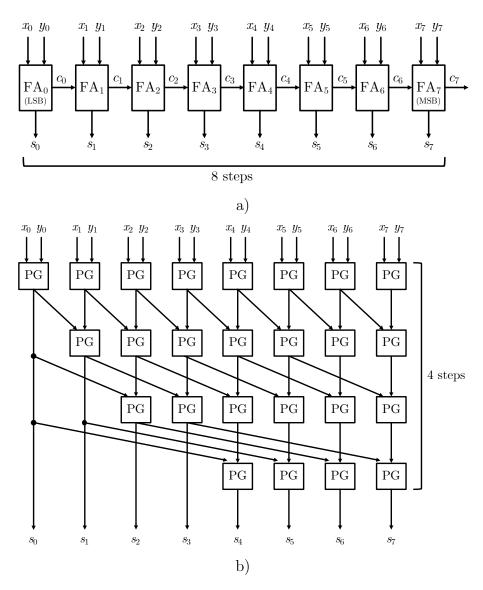

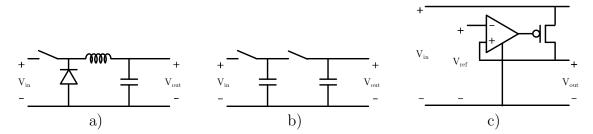

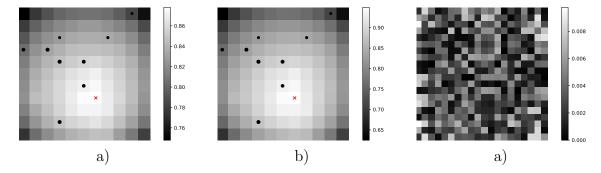

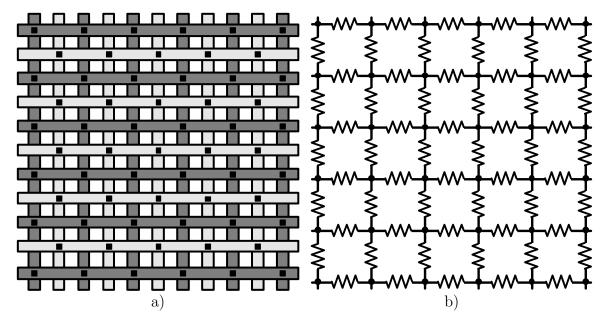

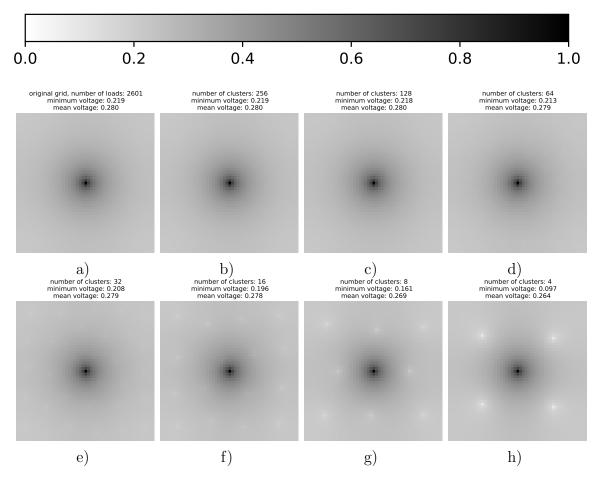

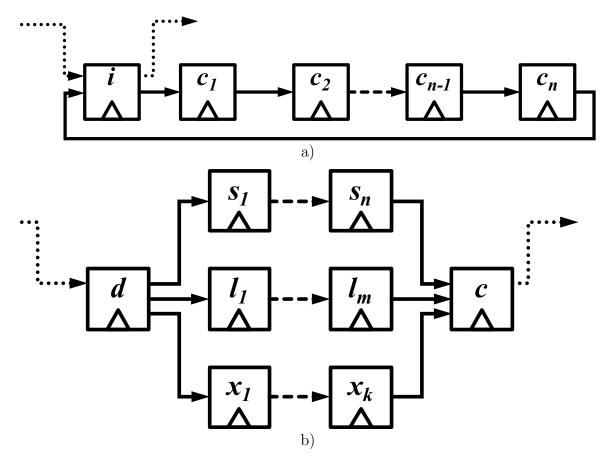

|     | Design hierarchy in VLSI. At the register transfer layer, these mac-       | 3.1 |

|-----|----------------------------------------------------------------------------|-----|

|     | roblocks are transformed into a network of memory blocks connected         |     |

|     | by wires and combinatorial logic. At the logic layer, a gate-level rep-    |     |

|     | resentation of the system is the primary focus. The transistors within     |     |

|     | the logic gates are the focus of the circuit layer. At the physical layer, |     |

| 99  | the circuits are transformed into a physical layout                        |     |

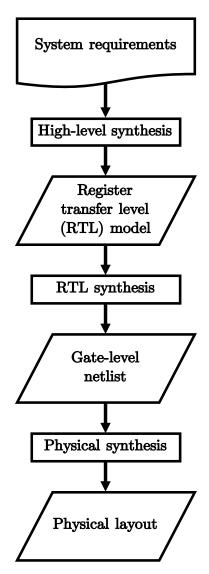

|     | General design flow for a digital VLSI system [180]. A high-level de-      | 3.2 |

|     | scription of a VLSI system is gradually converted into more detailed       |     |

|     | formats. A register transfer level model is initially created. The RTL     |     |

|     | models are converted into a logic gate-level netlist. The layout is gen-   |     |

| 101 | erated during the physical synthesis and layout processes                  |     |

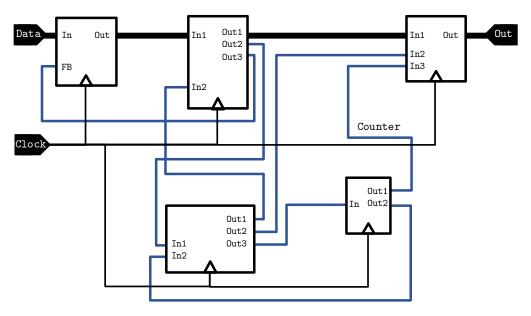

|     | Example of a VLSI system from an RTL perspective. The system               | 3.3 |

|     | consists of multiple interconnected functional blocks. The data flow       |     |

| 105 | within the system is synchronized by a common clock signal                 |     |

|     | The Von Neumann architecture is a reprogrammable architecture ini-         | 3.4 |

|     | tially developed for early programmable computers. The architecture        |     |

|     | consists of a CPU, memory, and input-output interface. The mem-            |     |

|     | ory stores data and instructions. The shared data and instruction bus      |     |

| 107 | provides communication between the CPU and memory                          |     |

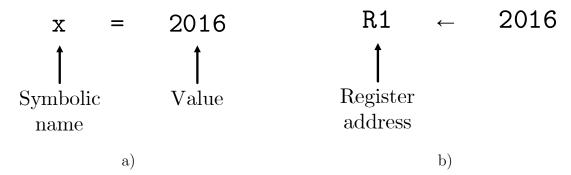

| 3.5 | Variables in computer engineering. a) Variable definition. The value                               |     |

|-----|----------------------------------------------------------------------------------------------------|-----|

|     | $2016$ is linked to the symbolic name $x.\ \ \mathrm{b})$ The value $2016$ is stored               |     |

|     | in register $\tt R1$ after register allocation. Operations involving variable $\tt x$              |     |

|     | will access R1.                                                                                    | 109 |

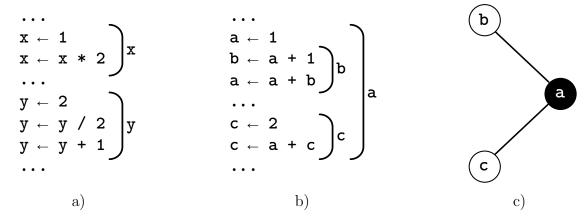

| 3.6 | Live ranges used for register allocation within a computer program.                                |     |

|     | a) Non-overlapping live ranges. Variables $\boldsymbol{x}$ and $\boldsymbol{y}$ can share the same |     |

|     | register. b) Overlapping live ranges. Variable <b>c</b> can be assigned to the                     |     |

|     | register of variable b, but not a, since the live ranges of a and c overlap.                       |     |

|     | c) Coloring of the interference graph for case (b). Register allocation                            |     |

|     | can be viewed as a graph coloring problem [213], [214], where the live                             |     |

|     | ranges are represented by nodes and the interference is represented by                             |     |

|     | edges                                                                                              | 110 |

| 3.7 | Greedy coloring of a bipartite graph. a) Optimal coloring order re-                                |     |

|     | quiring only two colors. b) Suboptimal coloring requiring three colors                             |     |

|     |                                                                                                    | 112 |

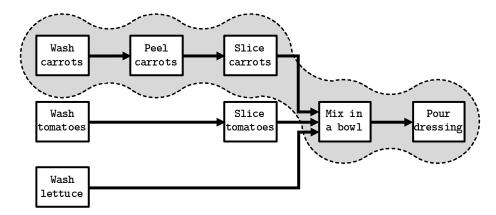

| 3.8 | Task graph for salad preparation. Directed edges establish a task prece-                           |     |

|     | dence. The shaded region represents a critical path, the longest chain                             |     |

|     | of dependent tasks.                                                                                | 114 |

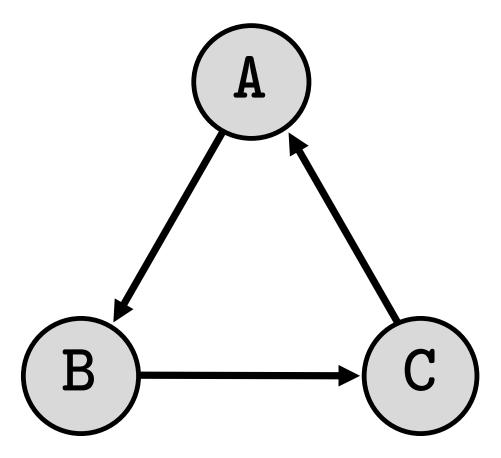

| 3.9  | Example of a circular task dependence. Task B awaits completion                |     |

|------|--------------------------------------------------------------------------------|-----|

|      | of task A, Task C awaits completion of task B, and task A awaits               |     |

|      | completion of task C. None of the tasks can therefore start, producing         |     |

|      | a deadlock                                                                     | 115 |

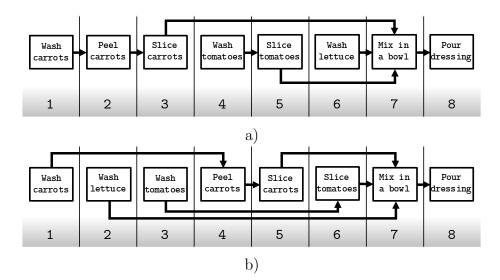

| 3.10 | Topological sort of the task graph shown in Fig. 3.9. Both of the              |     |

|      | schedules in (a) and (b) are valid, since the sequence number of each          |     |

|      | task is greater than the sequence number of the preceding tasks. $$ . $$       | 116 |

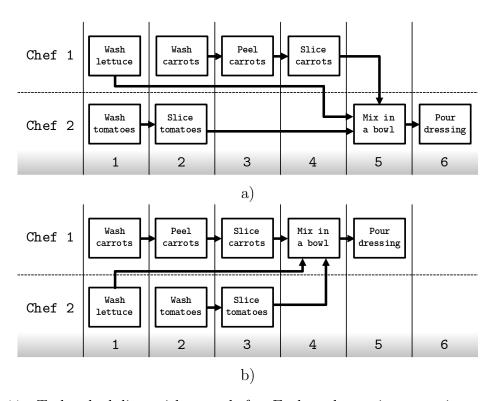

| 3.11 | Task scheduling with two chefs. Each task requires one time unit. a)           |     |

|      | Suboptimal task scheduling. Chef 2 is idle for two time units. b)              |     |

|      | Optimal task scheduling, requiring one fewer time unit. The execution          |     |

|      | time cannot be further optimized, since the execution time is equal to         |     |

|      | the length of the critical path                                                | 118 |

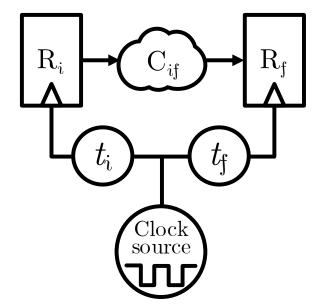

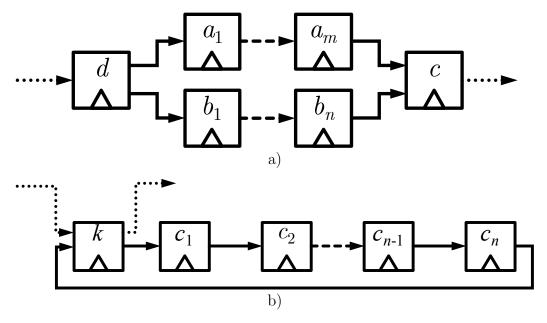

| 3.12 | A sequential system exhibiting clock skew. The clock signal is gen-            |     |

|      | erated at the clock source and travels through the clock tree toward           |     |

|      | registers $R_i$ and $R_f$ . The delay from the clock source to registers $R_i$ |     |

|      | and $R_f$ are, respectively, $t_i$ and $t_f$                                   | 121 |

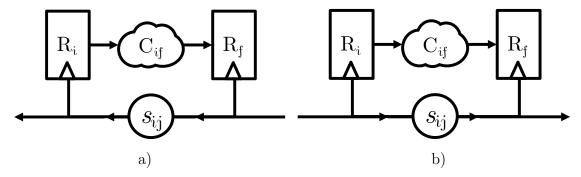

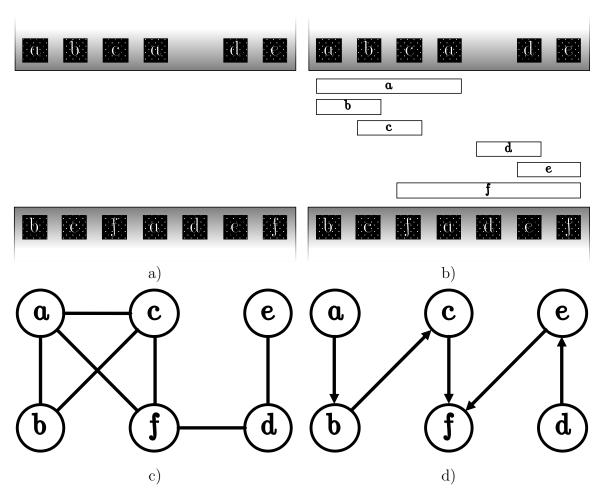

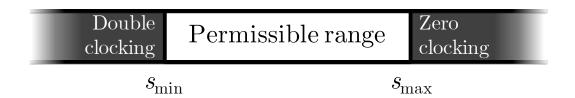

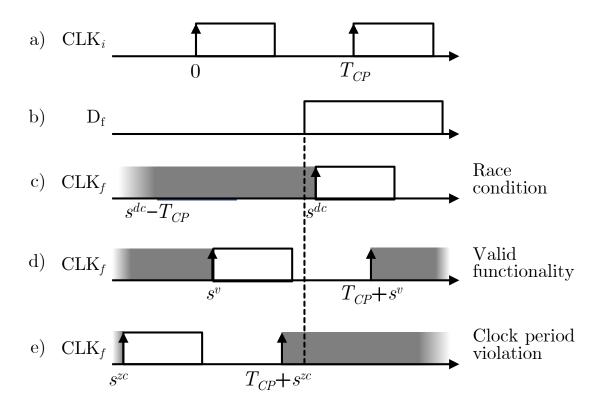

| 3.13 | Data and clock flow for positive and negative skew. a) Positive clock         |     |

|------|-------------------------------------------------------------------------------|-----|

|      | skew. The clock signal travels in the direction opposite to the flow          |     |

|      | of data. The effective clock period is reduced. This configuration is         |     |

|      | immune to race conditions. b) Negative clock skew. The clock signal           |     |

|      | travels in the same direction as the datum. The effective clock period        |     |

|      | is increased. Race conditions may occur if the data signal arrives at         |     |

|      | $R_f$ before arrival of the clock signal within the same clock period         | 122 |

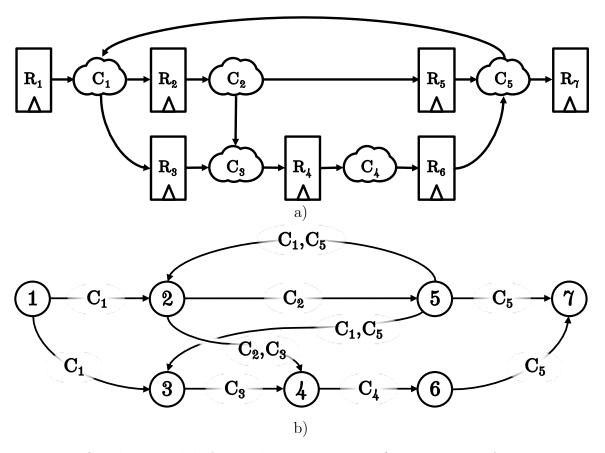

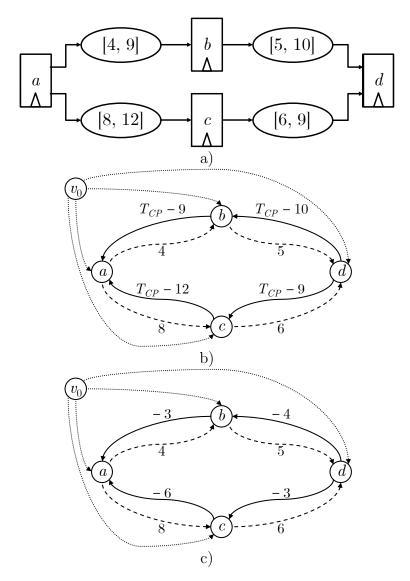

| 3.14 | Graphical model of a synchronous system. a) Register transfer level           |     |

|      | representation of a synchronous system. b) Timing graph. The nodes            |     |

|      | represent sequential logic elements, and the edges represent combina-         |     |

|      | torial logic.                                                                 | 123 |

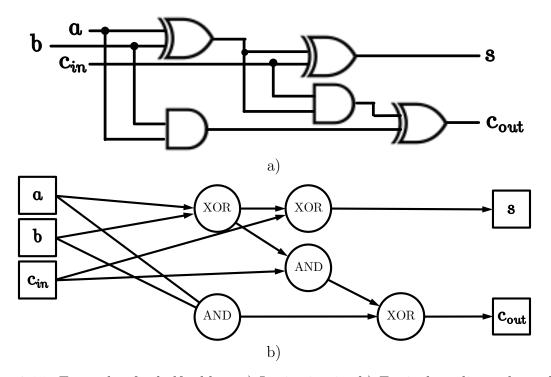

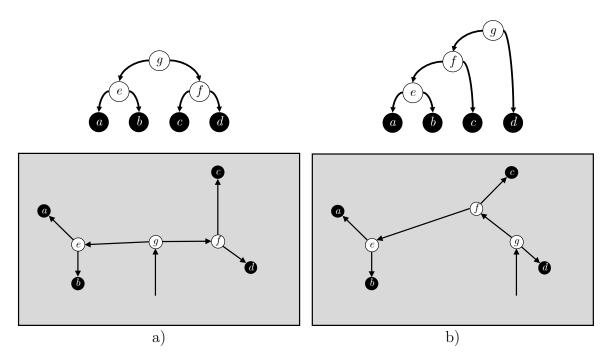

| 3.15 | Example of a half adder. a) Logic circuit. b) Equivalent directed graph.      |     |

|      | The nodes denote the gates, and the edges denote the connection be-           |     |

|      | tween the gates. Observe that the fan-in and fan-out of the gates are         |     |

|      | equal to, respectively, the indegree and outdegree of the corresponding       |     |

|      | node in a directed graph                                                      | 125 |

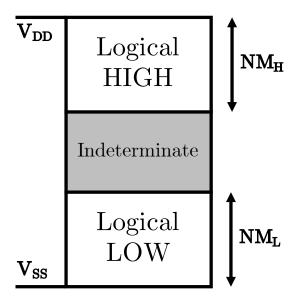

| 3.16 | Noise margins in digital circuits. The voltage in a digital circuit ranges    |     |

|      | from $V_{SS}$ to $V_{DD}$ . The signals in digital circuits are often treated |     |

|      | as binary numbers. Any voltage within $NM_L$ or $NM_H$ is treated,            |     |

|      | respectively, as logical 0 or logical 1                                       | 127 |

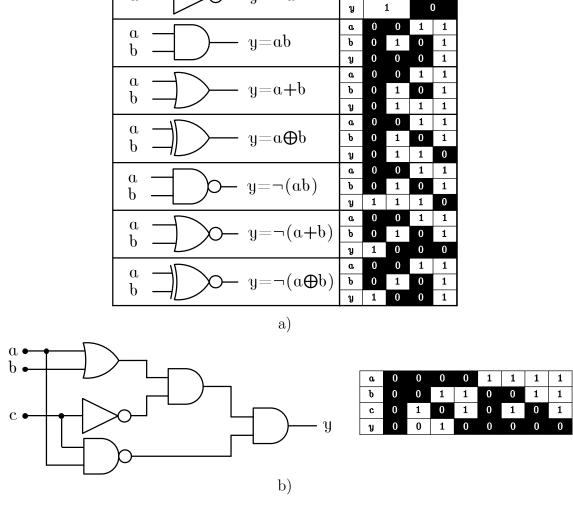

| 3.17 | Examples of logic gates. a) A list of primitive one and two input logic    |     |

|------|----------------------------------------------------------------------------|-----|

|      | gates and truth tables. b) An example of a logic circuit composed of       |     |

|      | multiple logic gates and the associated truth table                        | 128 |

| 3.18 | Truth table for function $f = a(b+c)$                                      | 129 |

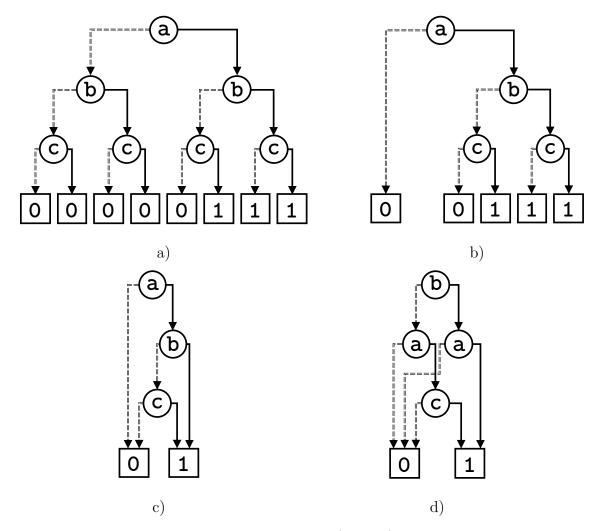

| 3.19 | Ordered Binary Decision Diagrams (OBDD) for a Boolean function             |     |

|      | f = a(b+c) and variable order $(a,b,c)$ . a) Original OBDD. The solid      |     |

|      | and dashed edges leaving edge $x$ represent, respectively, paths $high(x)$ |     |

|      | and $low(x)$ . b) OBDD after eliminating nodes $b$ and $c$ for the case    |     |

|      | a=0. c) Reduced OBDD (ROBDD). d) Inefficient ROBDD due to                  |     |

|      | suboptimal variable order $(b, a, c)$                                      | 132 |

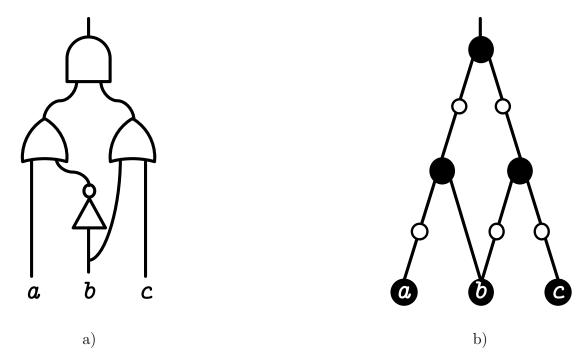

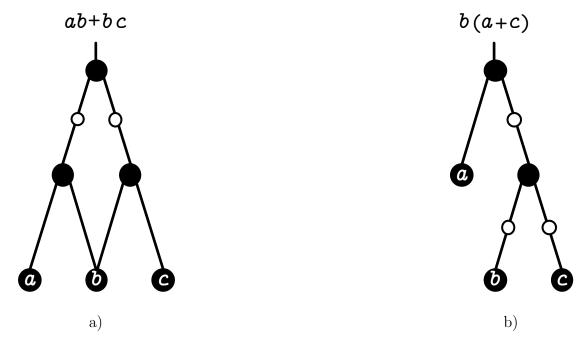

| 3.20 | Conversion of a Boolean circuit into an And-Inverter graph (AIG). a)       |     |

|      | Original circuit. b) Equivalent AIG                                        | 134 |

| 3.21 | Identical Boolean functions can be represented differently using an        |     |

|      | AIG. a) $ab + bc$ , and b) $b(a + c)$ . Both (a) and (b) describe the same |     |

|      | function                                                                   | 135 |

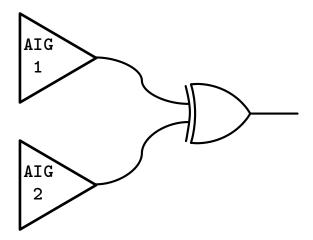

| 3.22 | Miter technique for checking the equivalence of two AIGs. The AIGs         |     |

|      | are connected to a XOR gate. The SAT problem is solved for this            |     |

|      | structure. If any input configuration produces output 1, the AIGs are      |     |

|      | not equivalent.                                                            | 136 |

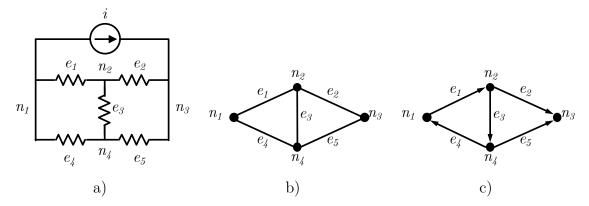

| 3.23 | Graph model of an electrical circuit. a) A resistive circuit with four |     |

|------|------------------------------------------------------------------------|-----|

|      | nodes, five resistors, and a current source, b) equivalent undirected  |     |

|      | graph model, and c) equivalent directed graph model, where the direc-  |     |

|      | tion of the edges indicates the assumed direction of current. $\dots$  | 138 |

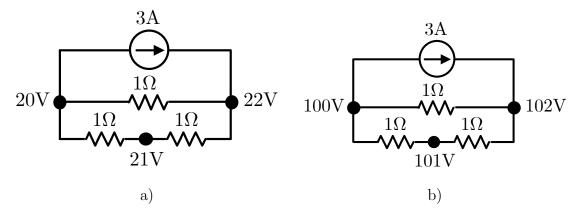

| 3.24 | Valid solutions for (3.21). In both (a) and (b), the potential at the  |     |

|      | nodes of the circuit satisfies (3.21)                                  | 144 |

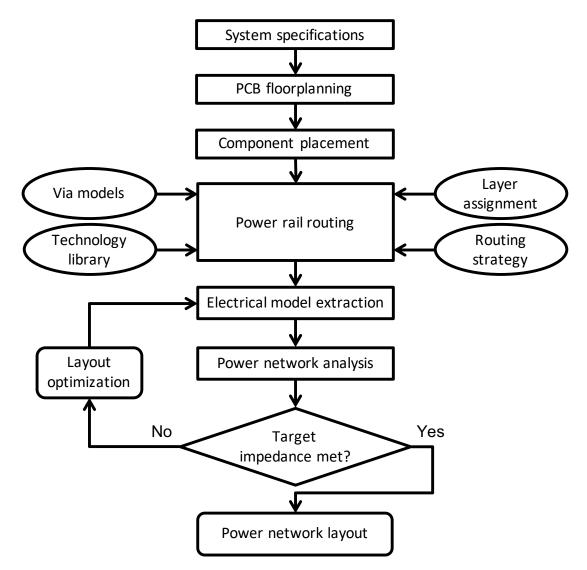

| 3.25 | Simplified flow diagram of physical design of a VLSI system. A cir-    |     |

|      | cuit is initially partitioned into multiple blocks. The constraints on |     |

|      | the location of the functional blocks is determined during the floor-  |     |

|      | planning stage. During the placement stage, the exact location of each |     |

|      | block is determined. The layout of the wires connecting the blocks is  |     |

|      | synthesized during the routing stage                                   | 148 |

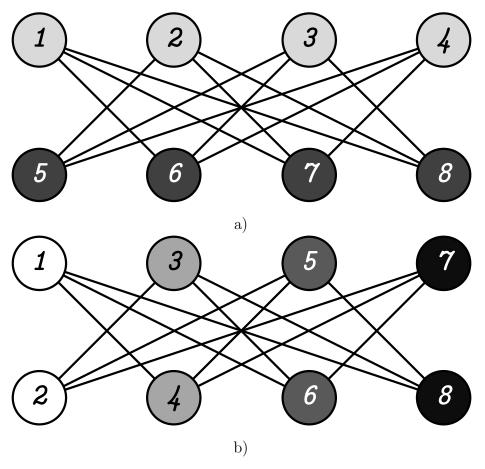

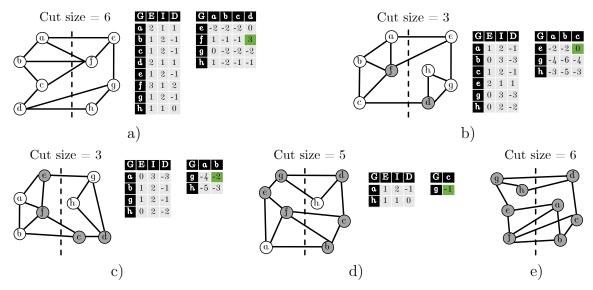

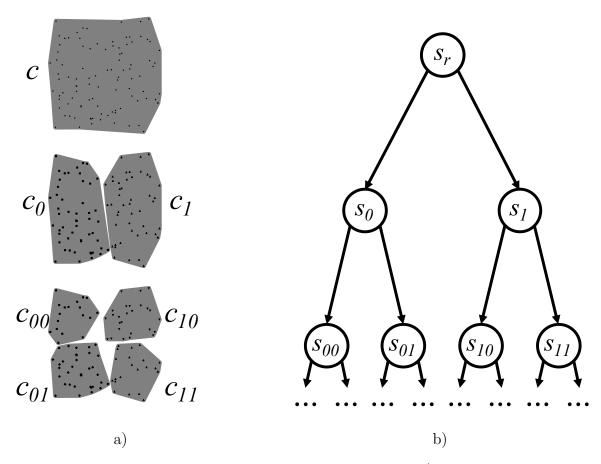

| 3.26 | Kernighan-Lin algorithm to partition a graph with eight nodes. a)           |     |

|------|-----------------------------------------------------------------------------|-----|

|      | Initial partition. The size of the partitions is equal, as required by      |     |

|      | the algorithm. In the left table, the number of external connections,       |     |

|      | number of internal connections, and the difference is calculated based      |     |

|      | on (3.27) and shown in, respectively, columns $E,\ I,$ and $D.$ In the      |     |

|      | right table, (3.28) is used to calculate the swapping gain for each pair    |     |

|      | of nodes. b) The partition after the first swap. The cut size is reduced    |     |

|      | to 3. Note that the swapped nodes are locked (shaded) and cannot be         |     |

|      | transferred to another partition. c) Partition after the second swap.       |     |

|      | The cut size is unchanged due to zero swapping gain during the swap.        |     |

|      | d) Partition after the third swap. The cut size is increased to five since  |     |

|      | the gain of swapping $b$ and $g$ is negative. Only two nodes are left,      |     |

|      | hence calculating the swapping gain is unnecessary but shown here for       |     |

|      | demonstrational purposes. e) Final partition                                | 153 |

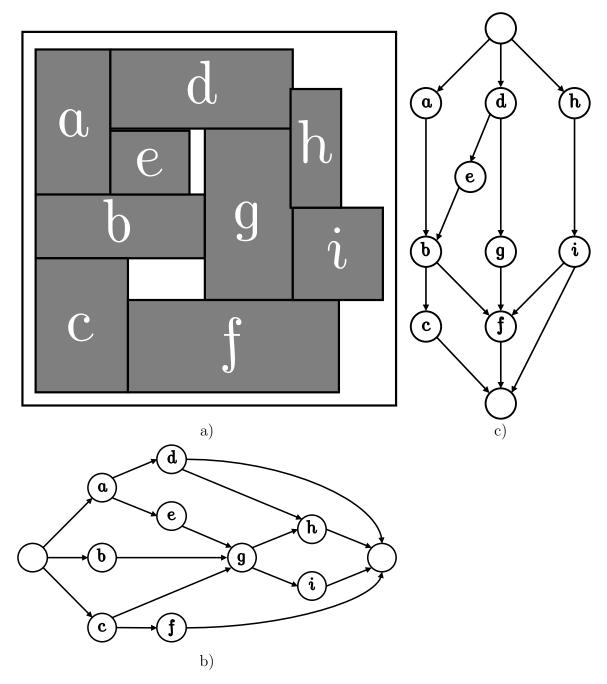

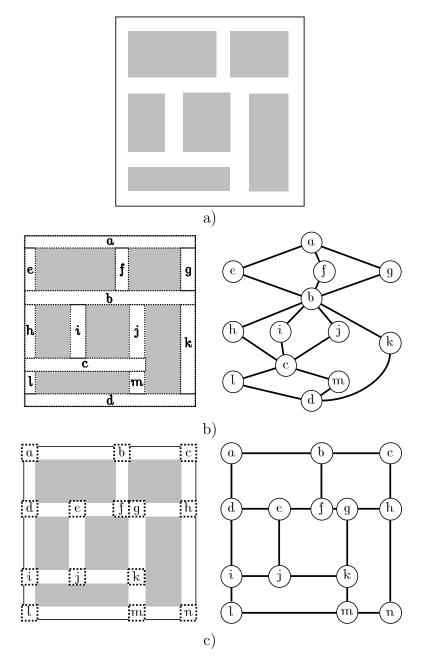

| 3.27 | Horizontal and vertical constraint graphs. a) Floorplan of an integrated    |     |

|      | system partitioned into nine modules. b) Horizontal constraint graph        |     |

|      | (HCG). An edge $(i,j)$ in the HCG indicates that block $i$ is located to    |     |

|      | the left of block $j$ . b) Vertical constraint graph (VCG). An edge $(i,j)$ |     |

|      | in the VCG indicates that block $i$ is located above block $j$              | 157 |

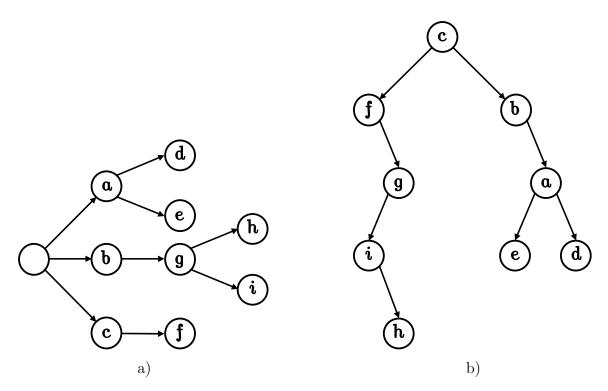

| 3.28 | Tree-based representation of the floorplan shown in Fig. 3.27a. a) An       |     |

|------|-----------------------------------------------------------------------------|-----|

|      | O-tree constructed by performing a depth-first search traversal of a        |     |

|      | vertical constraint graph. b) $B^*$ -tree – a binary tree representation of |     |

|      | a floorplan. The root node corresponds to the node at the left-bottom       |     |

|      | corner of the floorplan. The left successor of a node in the $B^*$ -tree    |     |

|      | corresponds to a block on the right side, while the right successor         |     |

|      | corresponds to a block on the top side                                      | 159 |

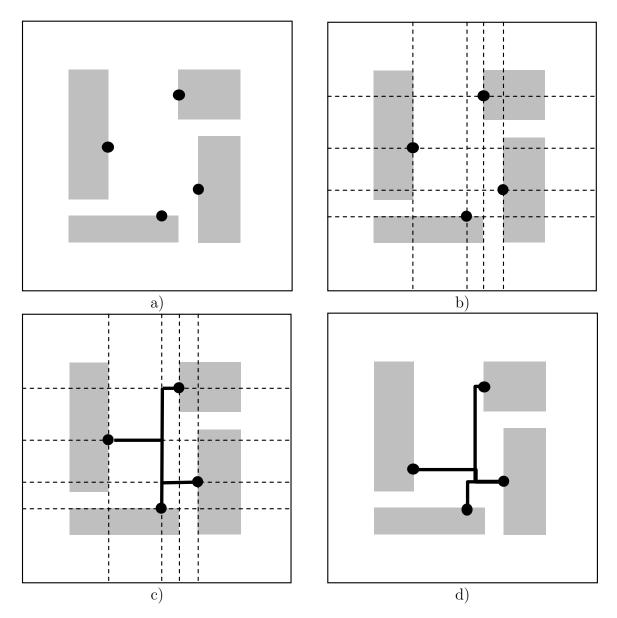

| 3.29 | Approximation of a minimum rectilinear Steiner tree based on a Hanan-       |     |

|      | grid. a) Initial block placement. The dots indicate the routing termi-      |     |

|      | nals. b) The Hanan grid is constructed by drawing lines through the         |     |

|      | terminal points. c) Based on a Hanan grid, a rectilinear minimum            |     |

|      | Steiner tree is approximated [276]. d) Final layout                         | 162 |

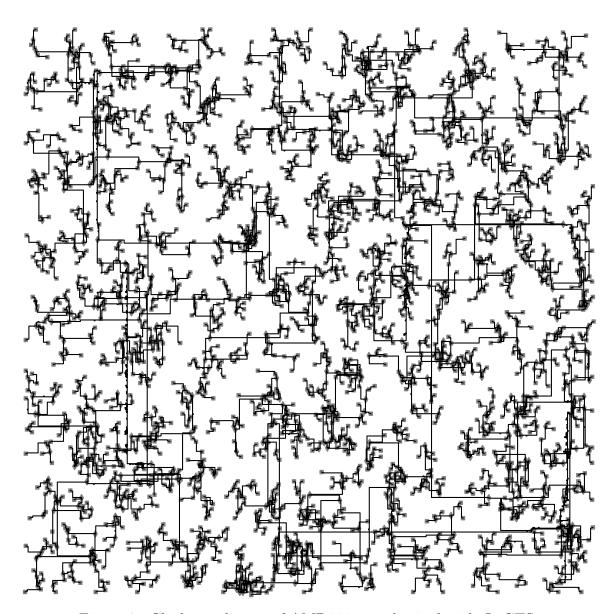

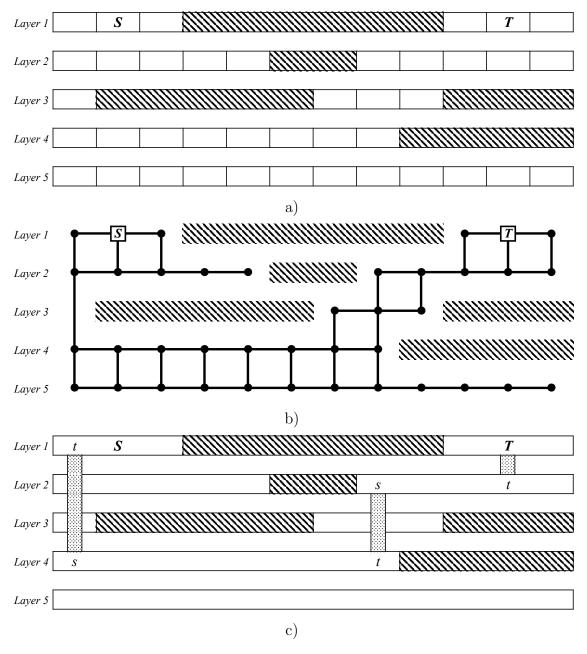

| 3.30 | Comparison of planar routing algorithms. a) Initial position of source      |     |

|      | (S) and target(T). b) Traversal during the Lee's maze routing algo-         |     |