# Sensitivity of Interconnect Delay to On-Chip Inductance

Yehea I. Ismail and Eby G. Friedman Department of Electrical and Computer Engineering University of Rochester Rochester, New York 14627

Abstract – Inductance extraction has become an important issue in the design of high speed CMOS circuits. Two characteristics of on-chip inductance are discussed in this paper that can significantly simplify the extraction of on-chip inductance. The first characteristic is that the sensitivity of a signal waveform to errors in the inductance values is low, particularly the propagation delay and the rise time. It is quantitatively shown in this paper that the error in the propagation delay and rise time is below 9.4% and 5.9%, respectively, assuming a 30% relative error in the extracted inductance. If an RC model is used for the same example, the corresponding errors are 51% and 71%, respectively. The second characteristic is that the magnitude of the on-chip inductance is a slowly varying function of the width of a wire and the geometry of the surrounding wires. These two characteristics can be exploited by using simplified techniques that permit approximate and sufficiently accurate values of the on-chip inductance to be determined with high computational efficiency.

## I. Introduction

The importance of on-chip inductance is increasing with faster on-chip rise times and longer wire lengths [1]-[15]. Wide wires are frequently encountered in clock distribution networks, data busses, and upper metal layers. These wires are low resistance lines that can exhibit significant inductive effects. Furthermore, performance requirements are pushing the introduction of new materials for low resistance interconnect [16]-[18] and new dielectrics to reduce the interconnect capacitance. These technological advances increase the importance of inductance, as has been described in [6]-[8], [13].

The efficient and accurate extraction of inductance is one of the primary bottlenecks that hinder incorporating on-chip inductance within IC CAD tools. To extract on-chip inductance, the return paths of the current flowing in an interconnect line must be determined. Initial work has assumed the return paths of the current are within the substrate [1]-[5]. However, further investigation has provided evidence that the return paths of the current are primarily within the power distribution network and other interconnect lines [6]-[12]. This characteristic of the return paths severely complicates the process of accurately extracting the on-chip inductance since the value of the inductance of a wire not only depends on the wire characteristics but also on the characteristics of other wires surrounding the line. This problem is further aggravated by the fact that the current return paths can be distributed among many power and signal wires, some of which may be hundreds of micrometers away from the wire for which the inductance is being extracted [1], [6]-[12]. Some research on on-chip inductance extraction has been described which places an emphasis on accuracy and the use of computationally expensive 3-D numerical algorithms [1]-[9]. Fortunately, as is shown in this paper, on-chip inductance has two useful characteristics which enable simple methods to be used to extract the on-chip inductance. These two characteristics are described and analyzed in section II. A summary is provided in section III.

## **II.** Characteristics of On-Chip Inductance which Simplify the Extraction Process

Two characteristics of on-chip inductance can be exploited to simplify the extraction process of on-chip inductance. These two characteristics are discussed in this section.

**First characteristic:** The sensitivity of a signal waveform to errors in the inductance values is low, particularly the propagation delay and rise time.

Inductance appears under a square root function in a waveform or timing expression characterizing a signal. The cause of this square root dependence is physically based since any LC constant has the dimensions of time squared, where L and C are any inductance and capacitance values in the circuit, respectively. The square root dependence can be compared to the linear dependence of the delay expressions on the resistance since any RC constant has the dimensions of time, where R is any resistance of the circuit. For example, according to the equivalent Elmore delay for RLC trees introduced in [19], the 50% delay of the signal at node i of an RLC tree is

$$t_{pdi} = 1.047 \cdot \sqrt{\sum_{k} C_{k} L_{ik}} \cdot e^{-\frac{\zeta_{i}}{0.85}} + 0.695 \cdot \sum_{k} C_{k} R_{ik} , \qquad (1)$$

where  $\zeta_i$  is the damping factor at node *i* and is

$$\zeta_{i} = \frac{1}{2} \frac{\sum_{k} C_{k} R_{ik}}{\sqrt{\sum_{k} C_{k} L_{ik}}}$$

(2)

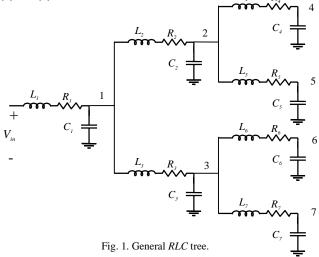

The summation variable *k* operates over all of the capacitors in the circuit.  $R_{ik}$  ( $L_{ik}$ ) is the common resistance (inductance) from the input to nodes *i* and *k*. For example, as shown in Fig. 1,  $R_{77} = R_1 + R_3 + R_7$ ,  $R_{67} = R_1 + R_3$ , and  $R_{27} = R_1$ . The square root dependence of the propagation delay on the inductance values in an *RLC* tree is evident in (1) and (2).  $L_4 = R_7$ .

This research was supported in part by the National Science Foundation under Grant No. MIP-9610108, the Semiconductor Research Corporation under contract No. 99-TJ-687, a grant from the New York State Science and Technology Foundation to the Center for Advanced Technology - Electronic Imaging Systems, and by grants from the Xerox Corporation, IBM Corporation, and Intel Corporation, Lucent Technologies Corporation, and Eastman Kodak Company.

<sup>0-7803-5482-6/99/\$10.00 ©2000</sup> IEEE

To quantify the error in the propagation delay due to errors in the extracted inductance, consider an extraction tool that generates a value of the extracted inductance with a maximum error E relative to the actual inductance value. Alternatively, the extracted inductance based on this extraction tool is in the range between L (1-E) and L(1+E) where L is the actual inductance value. The worst case error in the propagation delay occurs when all of the inductance values are overestimated by a maximum factor of (1+E) [or underestimated by a minimum factor of (1-E)]. In that case, the propagation delay in (1) becomes

$$t_{pdi_{-}E} = 1.047 \cdot \sqrt{1+E} \cdot \sqrt{\sum_{k} C_{k} L_{ik}} \cdot e^{-\frac{\zeta_{i}}{0.85 \cdot \sqrt{1+E}}} + 0.695 \cdot \sum_{k} C_{k} R_{ik} , \qquad (3)$$

where  $L_{ik}$  represent the actual inductance values and (1) represents the actual propagation delay. Errors in the extracted inductance result in a worst case relative error of the propagation delay as given by

$$Et_{pdi_{E}E} = \left| \frac{t_{pdi} - t_{pdi_{E}}}{t_{pdi}} \right| = \left| \frac{1.047 \cdot \left[ e^{-\frac{\zeta_{i}}{0.85}} - \sqrt{1 + E} \cdot e^{-\frac{\zeta_{i}}{0.85 \cdot \sqrt{1 + E}}} \right]}{1.047 \cdot e^{-\frac{\zeta_{i}}{0.85}} + 1.39 \cdot \zeta_{i}} \right|.$$

(4)

The worst case error in the propagation delay only depends upon the damping factor and the worst case error in the extracted inductance. Another interesting metric is the error in the propagation delay due to neglecting inductance altogether and using an *RC* interconnect model. The propagation delay in this case can be calculated by letting  $L_{\mu} \rightarrow 0$  in (1) and is

$$t_{pdi_{RC}} = 0.695 \cdot \sum_{k} C_{k} R_{ik} , \qquad (5)$$

which is simply the Elmore (Wyatt) approximation of the propagation delay [20], [21]. Thus, the relative error in the propagation delay when inductance is not extracted and an *RC* model is used is

$$Et_{pdi_{-}RC} = \left| \frac{t_{pdi_{-}RC}}{t_{pdi}} \right| = \left| \frac{1.047 \cdot e^{-\frac{\zeta_{i}}{0.85}}}{1.047 \cdot e^{-\frac{\zeta_{i}}{0.85}} + 1.39 \cdot \zeta_{i}} \right|.$$

(6)

The relative error in the propagation delay due to using an *RC* model is only a function of the damping factor.

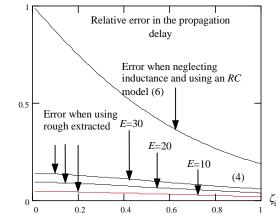

The worst case error in the propagation delay due to errors in the extracted inductance as given by (4) versus  $\zeta_i$  is plotted in Fig. 2 for several values of E. Equation (6) is also plotted in Fig. 2. Note in Fig. 2 that including the extracted inductance in evaluating the propagation delay significantly improves the accuracy as compared to an RC model even with a 30% error in the extracted inductance. The error in the propagation delay decreases with increasing  $\zeta_i$  since a higher damping factor means the inductance has less effect and most of the delay is due to the RC time constants in the circuit, thereby diminishing the relevance of the error caused by inexact inductance values. Note also that the improvement in accuracy by extracting approximate values of inductance as compared to using an RC model increases as the importance of the inductance increases (for small  $\zeta_{i}$ ), which is the range of primary interest. Numerical values of the error in the propagation delay are listed in Table 1 with different accuracy levels of extracted inductance values and with no inductance. At  $\zeta_{i}$  = 0.4 and with a relative error in the inductance values of 30%, the relative error in the propagation delay improves by a factor of five as compared to using an RC model.

Table 1. Relative error of the propagation delay when inductance is extracted and when an RC model is used. The relative errors for the extracted inductance values are 10%, 20%, and 30%.

| $\zeta_i$ | Relative error of the propagation delay |            |            |                 |  |  |  |

|-----------|-----------------------------------------|------------|------------|-----------------|--|--|--|

|           | Extraction                              | Extraction | Extraction | RC model        |  |  |  |

|           | error                                   | error      | error      | (no inductance) |  |  |  |

|           | E=10%                                   | E=20%      | E=30%      |                 |  |  |  |

| 0.0       | 4.9%                                    | 9.5%       | 14%        | 100%            |  |  |  |

| 0.2       | 4.5%                                    | 8.8%       | 13%        | 75%             |  |  |  |

| 0.4       | 3.9%                                    | 7.6%       | 11%        | 54%             |  |  |  |

| 0.6       | 3.2%                                    | 6.3%       | 9.3%       | 39%             |  |  |  |

| 0.8       | 2.6%                                    | 5.1%       | 7.5%       | 27%             |  |  |  |

| 1.0       | 2%                                      | 4%         | 6%         | 19%             |  |  |  |

Fig. 2. The relative error in (4) and (6) is plotted versus  $\zeta_i$ . Several values of *E* in (4) are used as labeled in the figure.

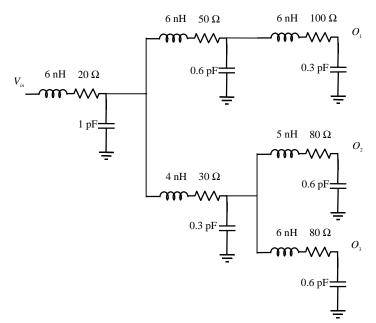

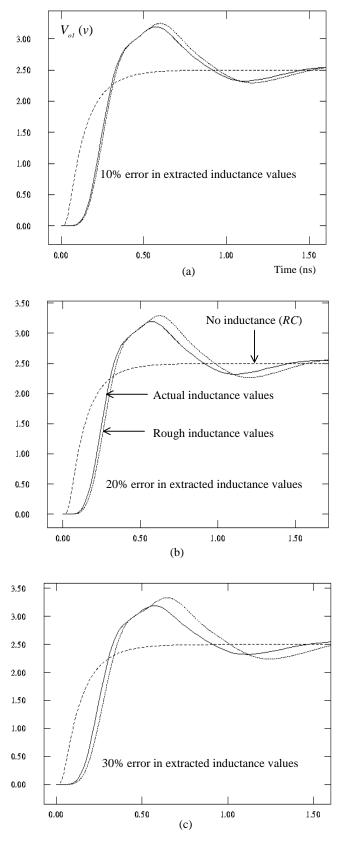

As an example, consider the RLC tree shown in Fig. 3. AS/X [22] simulations are performed with the inductance values shown in Fig. 3, with no inductance (an RC model), and with all of the inductance values increased by 10%, 20%, and 30%. These simulations are depicted in Fig. 4. Note in the simulations that using an approximate inductance estimation greatly improves the accuracy of the waveform as compared to using an RC model. The 50% delay and the 10%-to-90% rise time are depicted in Table 2 for the circuit simulations shown in Fig. 4. With a 30% error in the inductance values, the propagation delay differs by 9.4% from the actual value as compared to 51% if an RC model is used. The improvement in the rise time is even greater. The rise time differs from the actual value by 5.9% with a 30% error in the inductance values as compared to a 71% error when an RC model is used. Note that these errors are worst case errors since the circuits are simulated after overestimating all of the inductance values in the circuit by 30%. Practically, some of the inductance values are overestimated while others are underestimated. The error in the different directions partially cancel, thereby reducing the error in the total delay. The maximum error in the waveform shape occurs around the overshoots (see Fig. 4). However, estimating the overshoot requires less accuracy since the overshoot value is usually evaluated to decide if the overshoot is within an acceptable limit. This high tolerance of the delay expressions to errors in the extracted inductance encourages the use of simplified techniques with higher computational efficiency to extract the on-chip inductance.

**Second characteristic:** The value of the on-chip inductance is a slow varying function of the width of the wire and the geometry of the surrounding wires.

Most of the analytic formulae approximating the on-chip inductance has a logarithmic dependence on the width of the interconnect [4]-[5], [11], which is a slowly varying function. Also, numerical three-dimensional extraction methods based on solving Maxwell's differential equations and experimental measurements have illustrated this slow varying behavior of on-chip inductance with wire width and the surrounding wires geometies [6]-[9]. On-chip inductance values for a high performance integrated circuit are typically between 4 nH/cm and 6 nH/cm for the range of wire widths used in [6]-[9].

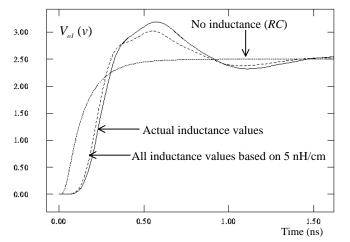

This characteristic together with the low sensitivity of the delay expressions to errors in the extracted inductance permit extraction techniques as simple as using a constant inductance value per unit length of interconnect of 5 nH/cm. Using a constant average value results in a maximum overestimation of 25% and a maximum underestimation of 16.6% of the inductance values. According to this sensitivity analysis, these errors in the inductance values result in errors of less than 9% in the propagation delay and below 5% in the rise time for typical damping factors commonly seen in high speed integrated circuits ( $\zeta_i > 0.4$ ) [6]-[9]. As an example, all of the inductance values in the tree shown in Fig. 3 are recalculated assuming a value of 5 nH/cm. AS/X [22] simulations are performed for the resulting tree and for the tree with actual inductance values. These simulations are shown in Fig. 5. The actual values of the propagation delay and rise time are 233 ps and 152 ps, respectively. The estimated propagation delay improves from 116 ps when using an RC model to 215 ps when using a constant inductance value of 5 nH/cm, which is equivalent to an improvement in the relative error from 51% to 7.7%. The estimated rise time improves from 260 ps to 146 ps, which is equivalent to an improvement in the relative error from 71% to 3.9%. There is an insignificant overhead to include inductance using this method. However, a significant amount of information characterizing the signal waveform shape which is lost when using an RC model can be retrieved by using this simple technique. If a more accurate inductance estimation is required, other methods can be used such as simple curve fitting or look-up table methods to quickly estimate the inductance based on the wire width and certain characteristics of the power distribution network such as the metal pitch. Other techniques can be considered which utilize simple analytic formulae to provide an approximate estimate of the inductance based on the wire width and certain characteristics of the power distribution network [11].

Fig. 3. An example of an *RLC* tree

Fig. 4. AS/X [22] simulations of the *RLC* tree shown in Fig. 3 at output node  $O_1$  with the actual inductance values, with no inductance (an *RC* model), and with all of the inductance values increased by a) 10%, b) 20%, and c) 30%.

Table 2. The 50% delay and the 10%-to-90% rise time from AS/X [22] simulations for the *RLC* tree shown in Fig. 3 with the actual inductance values, with all of the inductance values increased by 10%, 20%, and 30%, and with no inductance (an *RC* model).

| Relative<br>error in<br>inductance<br>values |               | <i>RC</i> (no inductance) | Relative<br>error | Actual<br>inductanc<br>e values | Relative<br>error | Rough<br>inductance<br>values |

|----------------------------------------------|---------------|---------------------------|-------------------|---------------------------------|-------------------|-------------------------------|

|                                              | $t_{pd}$ (ps) | 116                       | 51%               | 233                             | 3.4%              | 241                           |

| 10%                                          | $t_r$ (ps)    | 260                       | 71%               | 152                             | 2.0%              | 155                           |

|                                              | $t_{pd}$ (ps) | 116                       | 51%               | 233                             | 6.9%              | 249                           |

| 20%                                          | $t_r$ (ps)    | 260                       | 71%               | 152                             | 3.9%              | 158                           |

|                                              | $t_{pd}$ (ps) | 116                       | 51%               | 233                             | 9.4%              | 255                           |

| 30%                                          | $t_r$ (ps)    | 260                       | 71%               | 152                             | 5.9%              | 161                           |

Fig. 5. AS/X [22] simulations of the *RLC* tree shown in Fig. 3 at output node  $O_1$  with the actual inductance values, with no inductance (an *RC* model), and with all of the inductance values recalculated based on a value of 5 nH/cm inductance per unit length.

### III. Summary

Two characteristics have been discussed in this paper that can be exploited to significantly simplify the extraction of on-chip inductance. The first characteristic is that the sensitivity of a signal waveform to errors in the inductance values is low, particularly the propagation delay and the rise time. It is quantitatively shown in this paper that the error in the propagation delay and rise time is below 9.4% and 5.9%, respectively, assuming a 30% relative error in the extracted inductance. If an RC model is used for the same example, the corresponding errors are 51% and 71%, respectively. The second characteristic is that the value of the on-chip inductance is a slow varying function of the width of the wire and the geometry of the surrounding wires. These two characteristics can be exploited by using simplified techniques to generate approximate inductance values with high computational efficiency. A trivial method such as using a constant value of average inductance per unit length has also been shown to significantly improve the accuracy of the propagation delay and the rise time as compared to using an RC model. Thus, one solution when extracting on-chip inductance is to tradeoff accuracy for computational efficiency and use simple estimates of the on-chip inductance.

#### References

- D. A. Priore, "Inductance on Silicon for Sub-Micron CMOS VLSI," *Proceedings of the IEEE Symposium on VLSI Circuits*, pp. 17-18, May 1993.

- [2] D. B. Jarvis, "The Effects of Interconnections on High-Speed Logic Circuits," *IEEE Transactions on Electronic Computers*, Vol. EC-10, No. 4, pp. 476 - 487, October 1963.

- [3] M. P. May, A. Taflove, and J. Baron, "FD-TD Modeling of Digital Signal Propagation in 3-D Circuits with Passive and Active Loads," *IEEE Transactions on Microwave Theory and Techniques*, Vol. MTT-42, No. 8, pp. 1514 - 1523, August 1994.

- [4] Y. Eo and W. R. Eisenstadt, "High-Speed VLSI Interconnect Modeling Based on S-Parameter Measurement," *IEEE Transactions* on Components, Hybrids, and Manufacturing Technology, Vol. CHMT-16, No. 5, pp. 555 - 562, August 1993.

- [5] M. Shoji, *High-Speed Digital Circuits*, Addison Wesley, Massachusetts, 1996.

- [6] A. Deutsch, et al., "High-Speed Signal Propagation on lossy transmission lines," *IBM Journal of Research and Development*, Vol. 34, No. 4, pp. 601 - 615, July 1990.

- [7] A. Deutsch, et al., "Modeling and Characterization of Long Interconnections for High-Performance Microprocessors," *IBM Journal of Research and Development*, Vol. 39, No. 5, pp. 547 - 667, September 1995.

- [8] A. Deutsch, et al., "When are Transmission-Line Effects Important for On-Chip Interconnections?," *IEEE Transactions on Microwave Theory and Techniques*, Vol. 45, No. 10, pp. 1836 - 1846, October 1997.

- [9] A. Duetsch, A. Kopcsay, and G. V. Surovic, "Challenges Raised by Long On-Chip Wiring for CMOS Microprocessors," *Proceedings of* the IEEE Topical Meeting on Electrical Performance of Electronic Packaging, pp. 21 – 23, October 1995.

- [10] Y. Massoud, S. Majors, T. Bustami, and J. White, "Layout Techniques for Minimizing On-Chip Interconnect Self Inductance," *Proceedings of the ACM/IEEE Design Automation Conference*, pp. 566 – 571, June 1998.

- [11] B. Krauter and S. Mehrotra, "Layout Based Frequency Dependent Inductance and Resistance Extraction for On-Chip Interconnect Timing Analysis," *Proceedings of the ACM/IEEE Design Automation Conference*, pp. 303 – 308, June 1998.

- [12] A. Duetsch, et al., "Design Guidelines for Short, Medium, and Long On-Chip Interconnect," Proceedings of the IEEE Topical Meeting on Electrical Performance of Electronic Packaging, pp. 30 – 32, October 1996.

- [13] Y. I. Ismail, E. G. Friedman, and J. L. Neves, "Figures of Merit to Characterize the Importance of On-Chip Inductance," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, Vol. 7, No. 4, pp. 442 – 449, December 1999.

- [14] Y. I. Ismail and E. G. Friedman, "Effects of Inductance on the Propagation Delay and Repeater Insertion in VLSI Circuits," *Proceedings of the ACM/IEEE Design Automation Conference*, pp. 721-724, June 1999.

- [15] L. T. Pillage, "Coping with RC(L) Interconnect Design Headaches," Proceedings of the IEEE/ACM International Conference on Computer-Aided Design, pp. 246 – 253, September 1995.

- [16] J. Torres, "Advanced Copper Interconnections for Silicon CMOS Technologies," *Applied Surface Science*, Vol. 91, No. 1, pp. 112 -123, October 1995.

- [17] P. J. Restle and A. Duetsch, "Designing the Best Clock Distribution Network," *Proceedings of the IEEE VLSI Circuit Symposium*, pp. 2 – 5, June 1998.

- [18] K. K. Likharev and V. K. Semenov, "RSFQ Logic/Memory Family: A New Josephson-Junction Technology for Sub-Terahertz-Clock Frequency Digital System," *IEEE Transactions on Applied Superconductivity*, Vol. AS-1, No. 1, pp. 3 - 28, March 1991.

- [19] Y. I. Ismail, E. G. Friedman, and Jose L. Neves, "Equivalent Elmore Delay for *RLC* Trees," *Proceedings of the ACM/IEEE Design Automation Conference*, pp. 715-720, June 1999.

- [20] W. C. Elmore, "The Transient Response of Damped Linear Networks," *Journal of Applied Physics*, Vol. 19, pp. 55 - 63, January 1948.

- [21] J. L. Wyatt, Circuit Analysis, Simulation and Design, Elsevier Science Publishers, North-Holland, 1987.

- [22] AS/X User's Guide, IBM Corporation, New York, 1996.