# Effective Capacitance of *RLC* Loads for Estimating Short-Circuit Power

Guoqing Chen and Eby G. Friedman Department of Electrical and Computer Engineering University of Rochester, Rochester, NY 14627 Email: guchen,friedman@ece.rochester.edu

Abstract—An effective capacitance of a distributed RLC load for estimating short-circuit power is presented in this paper. Both resistive and inductive shielding effects of interconnects are considered and no iterations are required to determine the effective capacitance. The proposed method has been verified with Cadence Spectre. For a single switching input, the average error of the short-circuit power obtained with the effective capacitance is less than 2% for the example circuits as compared with an  $RLC \ \pi$  model. The proposed method can be used in look-up table or k-factor based models to estimate short-circuit power dissipation in CMOS gates with complex interconnects.

#### I. INTRODUCTION

With CMOS technology scaling, power has become an important design criterion in integrated circuits due to the increasing number of portable applications. Furthermore, high power dissipation can generate significant heat which limits performance and increases cooling costs. A capability of accurately and efficiently estimating power is therefore needed in the circuit design process.

As compared with dynamic power which is well characterized, short-circuit power is more difficult to model due to the complicated transient behavior of the short-circuit current. In [1], Veendrick developed a closed form expression for shortcircuit power dissipation in an unloaded CMOS inverter. More accurate analyses have recently been presented by including both short-channel effects and output overshoot effects [2], [3]. In these analyses, a lumped capacitor is assumed as the load. In [4], an  $RC \pi$  model is adopted as the load to characterize the shielding effect of the interconnect resistance. An effective capacitance of the  $RC \pi$  structure for short-circuit power estimation is described in [5] to maintain compatibility with popular look-up table or k-factor based power models. With increasing on-chip frequencies and longer interconnects, the interconnect inductance also needs to be considered. As described in [6], the interconnect inductance also exhibits a shielding effect on the load capacitance, increasing the shortcircuit power dissipated by the driver.

In this paper, an effective capacitance of an RLC load is developed to accurately estimate short-circuit power. Both resistive and inductive shielding effects are considered. The paper is organized as follows. In section II, a distributed RLC network is reduced into a  $\pi$  model. From this  $\pi$  model, the effective capacitance is determined. In section III, the proposed effective capacitance model is verified by Cadence Spectre simulations. Finally, some conclusions are offered in section IV.

# II. EFFECTIVE CAPACITANCE OF AN RLC LOAD

As technology progresses, interconnect networks have become increasingly complicated. One efficient method for analyzing interconnect is the model order reduction technique. This technique has demonstrated significant efficiency in the timing and power analysis process. In section II-A, a  $\pi$  model is generated from a distributed *RLC* tree, which is further reduced into an effective capacitance in section II-B.

### A. Model order reduction

By matching the first three moments  $(y_1, y_2, \text{ and } y_3)$  of the admittance at the driving point, an RC network can be reduced into an  $RC \pi$  model [7]. In the same way, an RLC network can be reduced into an  $RLC \pi$  model by matching the first four moments. This reduction, however, can be unrealizable (the value of the circuit element is not positive real). In order to obtain a realizable  $RLC \pi$  model, a new coefficient  $y_3^*$  is introduced in [8], which is the third order admittance moment (without considering inductance). By matching  $y_1, y_2, y_3$ , and  $y_3^*$ , the  $\pi$  model parameters can be obtained as [8]

$$C_f = y_2^2 / y_3^*, \tag{1}$$

$$C_n = y_1 - C_f,\tag{2}$$

$$R_{\pi} = -y_2/C_f^2, \tag{3}$$

$$L_{\pi} = (y_3^* - y_3) / C_f^2, \tag{4}$$

where  $C_n$  and  $C_f$  denote the near end and far end capacitance, respectively.

The input admittance of a distributed RLC interconnect with a load admittance  $Y_l$  is [9]

$$Y(s) = \frac{Z_c Y_l + \tanh \theta}{Z_c (1 + Z_c Y_l \tanh \theta)},$$

(5)

where  $\theta = \sqrt{(R+sL)sC}$  and  $Z_c = \frac{\theta}{Cs}$ . R, C, and L are the total resistance, capacitance, and inductance of the

This research is supported in part by the Semiconductor Research Corporation under Contract No. 2003-TJ-1068 and 2004-TJ-1207, the National Science Foundation under Contract No. CCR-0304574, the Fulbright Program under Grant No. 87481764, a grant from the New York State Office of Science, Technology & Academic Research to the Center for Advanced Technology in Electronic Imaging Systems, and by grants from Xerox Corporation, IBM Corporation, Intel Corporation, Lucent Technologies Corporation, Eastman Kodak Company, and Manhattan Routing, Inc.

interconnect, respectively. By expanding Y(s) into a Taylor series of s around zero, the moments at the input of the *RLC* interconnect can be obtained as

$$y_1 = y_{l,1} + C,$$

(6)

$$y_2 = y_{l,2} - R(y_{l,1}^2 + y_{l,1}C + \frac{1}{3}C^2),$$

(7)

$$y_{3} = y_{l,3} - R(2y_{l,1}y_{l,2} + y_{l,2}C) + R^{2}(y_{l,1}^{3} + \frac{4}{3}y_{l,1}^{2}C + \frac{2}{3}y_{l,1}C^{2} + \frac{2}{15}C^{3}) - L(y_{l,1}^{2} + y_{l,1}C + \frac{1}{3}C^{2}),$$

(8)

$$y_{3}^{*} = y_{l,3}^{*} - R(2y_{l,1}y_{l,2} + y_{l,2}C) + R^{2}(y_{l,1}^{3} + \frac{4}{3}y_{l,1}^{2}C + \frac{2}{3}y_{l,1}C^{2} + \frac{2}{15}C^{3}).$$

(9)

The input admittance moments of a distributed *RLC* tree can be determined by recursively applying (6)-(9). From these moments and (1)-(4), the corresponding  $\pi$  structure can be obtained.

# B. Effective capacitance for short-circuit power

Although a  $\pi$  model is highly accurate, four coefficients are required in this model, making it incompatible with k-factor expressions or look-up table based power models. An effective capacitance greatly simplifies the model with little penalty in accuracy.

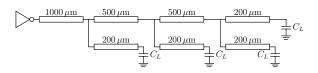

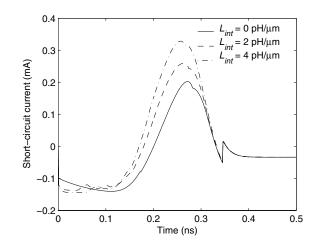

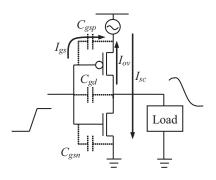

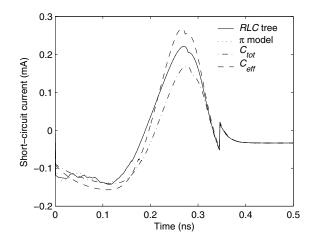

The shielding effect of the interconnect resistance is well known and the effective capacitance of RC interconnects has been developed for estimating delay and short-circuit power in [5], [10]. The interconnect inductance however also has a shielding effect [6]. This inductive shielding effect is illustrated with an example (shown in Fig. 1). In Fig. 1, a distributed *RLC* tree is driven by a 0.18  $\mu$ m CMOS inverter. The size of the transistors in the inverter is  $W_n = 10 \,\mu$  m and  $W_p = 25 \,\mu$  m. The impedance parameters of the interconnect are  $R_{int} = 12.23 \,\mathrm{m}\Omega/\mu\mathrm{m}$  and  $C_{int} = 0.245 \,\mathrm{fF}/\mu\mathrm{m}$ . The load capacitance is  $C_L = 100 \, \text{fF}$ . The short-circuit current of the inverter is illustrated in Fig. 2 for different values of interconnect inductance. When the interconnect inductance becomes larger, greater far end capacitance is shielded. Less effective capacitance is therefore seen at the inverter output, permitting the output voltage to change faster at the beginning of the signal transition, thereby producing a larger shortcircuit current. The currents are measured at the source of the PMOS transistor with a rising input as shown in Fig. 3. The discontinuity of the waveform is due to the discontinuity of the transistor capacitance model used in the simulation. Strictly speaking, the currents illustrated in Fig. 2 include two non-short-circuit current components. The first component is the current flowing through the capacitance  $C_{qs}$ , as shown in Fig. 3. This component can be determined as  $I_{gs} = C_{gs}V_{dd}/t_r$ and is independent of the load. The second component is the current  $I_{ov}$  flowing from the output to  $V_{dd}$  due to the overshoot at the output in the beginning of the signal transition.  $I_{ov}$ returns a small amount of charge stored in the output node back to  $V_{dd}$ , slightly reducing the dynamic power.

Fig. 1. A distributed RLC tree.

Fig. 2. Effect of inductance on the short-circuit current.  $t_r = 0.5$  ns.

In [10], the output waveform of a CMOS gate is approximated by a quadratic function followed by a linear function. In this paper, the output waveform of a gate is modeled as a quadratic function during the input transition time. Assuming the output waveform is  $v(t) = at^2$  for a rising edge, the current drawn from the gate by an *RLC*  $\pi$  structure is

$$I_{\pi}(s) = \frac{2a}{s^3} \left( \frac{C_f s}{1 + R_{\pi} C_f s + L_{\pi} C_f s^2} + C_n s \right).$$

(10)

Applying an inverse Laplace transformation to (10), the current in the time domain is

$$i_{\pi} = 2aC_f(-R_{\pi}C_f + t + k_1e^{s_1t} + k_2e^{s_2t}) + 2aC_nt, \quad (11)$$

where

$$s_{1,2} = \frac{-R_{\pi} \pm \sqrt{R_{\pi}^2 - 4L_{\pi}/C_f}}{2L_{\pi}},$$

(12)

$$k_1 = \frac{1}{s_1^2(s_1 - s_2)L_\pi C_f},\tag{13}$$

$$k_2 = \frac{1}{s_2^2(s_2 - s_1)L_{\pi}C_f}.$$

(14)

The current drawn from the gate by an effective capacitance is  $i_{ceff} = 2aC_{eff}t$ . Equating the average of  $i_{\pi}$  and  $i_{ceff}$ during a period from 0 to an evaluation time  $t_{ev}$ ,  $C_{eff}$  can be obtained as

$$C_{eff} = C_n + C_f \left[ 1 - \frac{2R_{\pi}C_f}{t_{ev}} + \frac{2k_1}{t_{ev}^2 s_1} (e^{s_1 t_{ev}} - 1) + \frac{2k_2}{t_{ev}^2 s_2} (e^{s_2 t_{ev}} - 1) \right].$$

(15)

The effective capacitance  $C_{eff-RC}$  for an  $RC \pi$  structure can be similarly determined. As expected,  $C_{eff}$  is between  $C_n$

Fig. 3. Current components in a CMOS inverter.

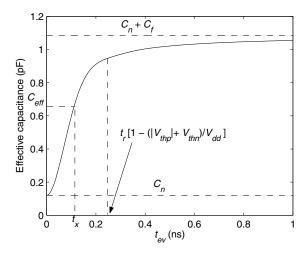

and  $C_n + C_f$ . From (15),  $C_{eff}$  is a function of  $t_{ev}$  as shown in Fig. 4. The  $\pi$  model parameters are obtained from the tree structure as shown in Fig. 1 with  $L_{int} = 0.74 \,\text{nH}/\mu\text{m}$ . With increasing  $t_{ev}$ ,  $C_{eff}$  increases from  $C_n$  and approaches  $C_n + C_f$ . In [10],  $t_{ev}$  is the time when the driver output achieves 50% of  $V_{dd}$ , which is the objective and is not known a priori. Several iterations are therefore required to determine  $C_{eff}$ . In [5],  $t_{ev}$  is determined as the end point of the shortcircuit period. Since the short-circuit current exists when the input is between  $V_{thn}$  and  $V_{dd} + V_{thp}$ , the evaluation time  $t_x$  is in the range from 0 to  $t_r(1 - \frac{|V_{thp}|}{V_{dd}} - \frac{V_{thn}}{V_{dd}})$ . Note that t = 0 corresponds to the time when the input reaches  $V_{thn}$  for a rising edge ( $V_{dd} + V_{thp}$  for a falling edge). As shown in Fig. 4, for the time period  $0 < t < t_x$ , the effective capacitance is overestimated and the short-circuit current is underestimated. For the period  $t_x < t < t_r (1 - \frac{|V_{thp}|}{V_{dd}} - \frac{V_{thn}}{V_{dd}})$ , the effective capacitance is underestimated and the shortcircuit current is overestimated. By properly adjusting  $t_x$ , the estimation error of the short-circuit current in different time regions can be canceled. By comparing Spectre simulations, a fitting parameter is adopted to determine  $t_x$ ,

$$t_x = 0.46t_r \left(1 - \frac{|V_{thp}|}{V_{dd}} - \frac{V_{thn}}{V_{dd}}\right).$$

(16)

The short-circuit current waveforms for an inverter with different load models are compared in Fig. 5. For this inverter,  $V_{thn} = 0.5$  volts and  $V_{thp} = -0.5$  volts. As shown in Fig. 5, the  $\pi$  model can accurately characterize a tree structure. The waveform obtained with a  $\pi$  model is indistinguishable from the waveform with the original *RLC* tree (shown in Fig. 1). Note that unlike  $C_{eff}$  for estimating the delay [10],  $C_{eff}$  for short-circuit power estimation is independent of the transistor size.

## **III. MODEL VERIFICATION**

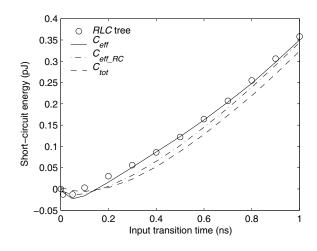

For the example shown in Fig. 1, the short-circuit energy dissipated over a full signal transition for different loads is compared in Fig. 6. As shown in Fig. 6, the total capacitance always underestimates the short-circuit energy as compared with a distributed RLC tree. For example, the error for  $t_r = 0.5$  ns is 28.1%. More accurate estimations can be obtained with  $C_{eff,RC}$  (only considering the resistive shielding effect) and  $C_{eff}$  (considering both resistive and inductive shielding

Fig. 4. Effective capacitance as a function of  $t_{ev}$ .  $C_n = 120.1$  fF,  $C_f = 965.9$  fF,  $R_p = 15.9 \Omega$ , and  $L_p = 0.96$  nH.

Fig. 5. Short-circuit current with different output loads.

effects). The inductive shielding effect is most important for this example in the range from  $t_r = 0.2 \,\mathrm{ns}$  to  $t_r =$  $0.8 \,\mathrm{ns.}$  When  $t_r$  is sufficiently large, the driver output has sufficient time to converge to the RC response [11], making the shielding effect of the inductance negligible. If  $t_r$  is too small, although the effect of the inductance on the output voltage waveform is large, the duration of the short-circuit current period is small, making the total short-circuit power insignificant. Since dynamic power is usually determined as  $\alpha f V_{dd}^2 C_{load}$  (where  $\alpha$  is the switching factor), the reduction  $P_{red}$  in dynamic power due to  $I_{ov}$  is considered part of the short-circuit power such that the summation of the two power components (dynamic and short-circuit) can represent the total transient power. With fast inputs,  $P_{red}$  can dominate the shortcircuit power, producing a negative short-circuit power, as shown in Fig. 6. Since  $P_{red}$  can not be characterized by  $C_{eff}$ , the error of the power estimation is greater for fast inputs.

The effective capacitance concept can also be applied to other logic gates, such as NAND and NOR gates. The shortcircuit energy consumed by an inverter and a two input NAND

| $T_r$           | $R_{\pi}/L_{\pi}/C_n/C_f$ | $C_{eff}$ | Inverter |           |           | NAND (upper) |           |           | NAND (lower) |           |           | NAND (both) |           |           |

|-----------------|---------------------------|-----------|----------|-----------|-----------|--------------|-----------|-----------|--------------|-----------|-----------|-------------|-----------|-----------|

| (ns)            | $(\Omega/nH/fF/fF)$       | (fF)      | $\pi$    | $C_{eff}$ | $C_{tot}$ | $\pi$        | $C_{eff}$ | $C_{tot}$ | $\pi$        | $C_{eff}$ | $C_{tot}$ | $\pi$       | $C_{eff}$ | $C_{tot}$ |

| 0.5             | 100/2/200/600             | 369.4     | 0.16     | 0.16      | 0.11      | 0.12         | 0.12      | 0.08      | 0.11         | 0.10      | 0.07      | 0.06        | 0.05      | 0.02      |

| 1               | 100/2/200/600             | 517.3     | 0.45     | 0.44      | 0.38      | 0.35         | 0.35      | 0.30      | 0.36         | 0.35      | 0.29      | 0.30        | 0.29      | 0.24      |

| 2               | 100/2/200/600             | 641.3     | 1.13     | 1.13      | 1.06      | 0.93         | 0.93      | 0.87      | 0.98         | 0.97      | 0.91      | 0.88        | 0.86      | 0.81      |

| 0.5             | 200/3/100/800             | 205.2     | 0.20     | 0.20      | 0.10      | 0.15         | 0.15      | 0.08      | 0.14         | 0.13      | 0.06      | 0.09        | 0.07      | 0.02      |

| 1               | 200/3/100/800             | 322.6     | 0.51     | 0.51      | 0.36      | 0.41         | 0.41      | 0.28      | 0.41         | 0.41      | 0.28      | 0.35        | 0.34      | 0.23      |

| 2               | 200/3/100/800             | 483.3     | 1.21     | 1.20      | 1.01      | 0.99         | 1.00      | 0.83      | 1.05         | 1.05      | 0.87      | 0.94        | 0.93      | 0.78      |

| 0.5             | 300/4/100/300             | 167.9     | 0.21     | 0.21      | 0.15      | 0.16         | 0.16      | 0.12      | 0.15         | 0.14      | 0.10      | 0.09        | 0.08      | 0.05      |

| 1               | 300/4/100/300             | 228.8     | 0.56     | 0.56      | 0.48      | 0.45         | 0.45      | 0.38      | 0.45         | 0.45      | 0.38      | 0.38        | 0.37      | 0.32      |

| 2               | 300/4/100/300             | 292.7     | 1.34     | 1.33      | 1.25      | 1.11         | 1.11      | 1.04      | 1.16         | 1.16      | 1.09      | 1.03        | 1.02      | 0.96      |

| Average % Error |                           |           |          | 0.9       | 22.1      | _            | 1.2       | 22.2      | _            | 1.6       | 24.4      |             | 7.2       | 33.5      |

TABLE I SHORT-CIRCUIT ENERGY DISSIPATION (pJ) DURING A FULL SIGNAL SWITCH.

Fig. 6. Short-circuit energy with different loads.  $L = 0.74 \text{ pH}/\mu\text{m}$ .

gate during a full signal transition is listed in Table I for different inputs and loads. The two inputs of the NAND gate are denoted as the upper input and lower input according to the relative location of the input terminal. Three switching patterns are considered: only the upper input is switched (the lower input is tied to  $V_{dd}$ ), only the lower input is switched, and both of the two inputs are connected and simultaneously switched. The size of the transistors in the NAND gate is  $W_n = 10 \,\mu\text{m}$  and  $W_p = 25 \,\mu\text{m}$ . For a single switching input, the average error of the short-circuit power is less than 2% as compared with the  $\pi$  model. The average error with the total capacitance, however, is more than 20% for these examples. As compared to the single switching input, the error with  $C_{eff}$ for the connected inputs is greater, exhibiting an average error of 7.2%. For multiple switching inputs with offsets in delay (non-simultaneous input signals), an equivalent input signal has been developed in [12] for estimating short-circuit power. From this equivalent input signal, an effective capacitance can be obtained from (15) and (16).

#### **IV. CONCLUSIONS**

Interconnect is highly significant in deep submicrometer integrated circuits. The interconnects not only dominate the overall circuit delay, but also greatly affect power dissipation. In this paper, the effective capacitance of a distributed RLC load is determined in order to accurately estimate shortcircuit power by considering the shielding effects of both the interconnect resistance and inductance. This effective capacitance can be used in look-up tables or in empirical kfactor expressions to estimate short-circuit power as well as in analytic approaches to simplify interconnect load models.

#### REFERENCES

- H. J. M. Veendrick, "Short-Circuit Dissipation of Static CMOS Circuitry and Its Impact on the Design of Buffer Circuits," *IEEE Journal of Solid-State Circuits*, Vol. SC-19, No. 4, pp. 468-473, August 1984.

- [2] K. Nose and T. Sakurai, "Analysis and Future Trend of Short-Circuit Power," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, Vol. 19, No. 9, pp. 1023-1030, September 2000.

- [3] J. L. Rosselló and J. Segura, "Charge-Based Analytical Model for the Evaluation of Power Consumption in Submicron CMOS Buffers," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, Vol. 21, No. 4, pp. 433-448, April 2002.

- [4] A. Chatzigeorgiou, S. Nikolaidis, and I. Tsoukalas, "Modeling CMOS Gates Driving RC Interconnect Loads," *IEEE Transactions on Circuits* and System II: Analog and Digital Signal Processing, Vol. 48, No. 4, pp. 413-418, April 2001.

- [5] F. Dartu, N. Menezes, and L. T. Pileggi, "Performance Computation for Precharacterized CMOS Gates with *RC* Loads," *IEEE Transactions* on Computer-Aided Design of Integrated Circuits and Systems, Vol. 15, No. 5, pp. 544-553, May 1996.

- [6] M. A. El-Moursy and E. G. Friedman, "Shielding Effect of On-Chip Interconnect Inductance," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, Vol. 13, No. 3, pp. 396-400, March 2005.

- [7] P. R. OBrien and T. L. Savarino, "Modeling the Driving-Point Characteristic of Resistive Interconnect for Accurate Delay Estimation," *Proceedings of the IEEE/ACM International Conference on Computer Aided Design*, pp. 512-515, April 1989.

- [8] X. Yang et al., "Hurwitz Stable Reduced Order Modeling for RLC Interconnect Trees," Proceedings of the IEEE/ACM International Conference on Computer Aided Design, pp. 222-228, November 2000.

- [9] G. Chen and E. G. Friedman, "An *RLC* Interconnect Model Based on Fourier Analysis," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, Vol. 24, No. 2, pp. 170-183, February 2005.

- [10] J. Qian, S. Pullela, and L. Pillage, "Modeling the Effective Capacitance for the *RC* Interconnect of CMOS Gates," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, Vol. 13, No. 12, pp. 1526-1535, December 1994.

- [11] Y. I. Ismail, E. G. Friedman, and J. L. Neves, "Figures of Merit to Characterize the Importance of On-Chip Inductance," *IEEE Transactions* on Very Large Scale Integration (VLSI) Systems, Vol. 7, No. 4, pp. 442-449, December 1999.

- [12] Q. Wang and S. B. K. Vrudhula, "A New Short Circuit Power Model for Complex CMOS Gates," *Proceedings of the IEEE Alessanfro Volta Memorial Workshop on Low-Power Design*, pp. 98-106, March 1999.