# Field Driven STT-MRAM Cell for Reduced Switching Latency and Energy

Ravi Patel, Engin Ipek, and Eby G. Friedman Department of Electrical and Computer Engineering University of Rochester Rochester, New York14627 Email: (rapatel, friedman, ipek)@ece.rochester.edu

Abstract—A field driven approach to STT-MRAM switching is proposed as a method for reducing the switching latency of an MTJ in high performance caches. An MRAM array model is presented to characterize the switching energy and maximum achievable reduction in energy using the field driven approach. The switching latency per bit is reduced by more than a factor of ten. The resultant switching energy per bit is reduced by 82% as compared to a standard STT-MRAM.

# I. INTRODUCTION

Spin torque transfer magnetoresistive RAM (STT-MRAM) is an emerging CMOS compatible memory technology with the potential to replace on-chip memory. Key features of STT-MRAM are non-volatility and unlimited write endurance. An issue constraining the use of STT-MRAM, however, is the long switching latency of the magnetic tunnel junction (MTJ) within each memory cell. The long latency causes the switching energy of an MTJ to be much greater than traditional CMOS SRAM.

To address these issues, the classic first generation MRAM field topology is utilized with an STT-MTJ where an additional field current destabilizes the MTJ prior to switching, thereby reducing the switching latency. An analytic framework for assessing and optimizing field driven writes in STT-MRAM arrays is described in this paper. Building on this framework, it is shown that the switching latency and energy can be reduced by amortizing the additional field current over many cells, leading to a significant reduction in energy consumed per bit.

Background on STT-MRAM and classical MRAM is provided in Section II. The field driven approach is compared with classical MRAM approaches in Section III, while a model of a memory cell is presented in Section IV. A model of an MRAM array is reviewed in Section V. Some conclusions are offered in Section VI.

# II. MTJ OPERATION

Magnetic tunnel junctions are two terminal resistive elements that operate on the principle of spin dependant conduction through magnetic domains [1]–[3]. The device is a stack of ferromagnetic metal on both sides of a tunneling oxide spacer. One of these layers has a fixed magnetization direction. The alternate ferromagnetic layer can flip between two opposite polarities, one polarity parallel to the fixed layer and the other polarity anti-parallel. These two states influence the electrons that pass through the oxide barrier, changing the resistance. From a circuit perspective, an MTJ acts as a bistable resistor. After switching is triggered, the resistance either settles to a high ( $R_{\rm off}$ ) or low ( $R_{\rm on}$ ) resistance and will remain at that resistance until another switching event.

In first generation MRAM circuits, the two large orthogonal currents generate magnetic fields within the free layer between adjacent metal lines. These fields are sufficiently strong to induce a torque on the magnetization, which eventually induces a reversal in polarity.

In modern spin torque transfer MTJs, the internal ferromagnetic layers generate a torque on the magnetization. The larger fixed ferromagnetic layer is capable of spin polarizing the incoming current, *i.e*, electrons from the incoming current attain spin. Electrons that pass through the fixed layer exhibit a net spin oriented with the fixed layer, while those electrons that reflect off the fixed layer exhibit a net anti-parallel spin. By controlling the direction of the current applied across the MTJ, either the reflected or passed electrons will contact the free layer and exert a torque on the magnetization.

### III. FIELD DRIVEN STT-MRAM CELL

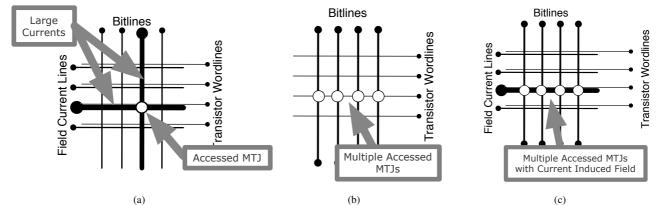

Since the spin transfer torque effect was first incorporated into MTJ switching [1], MRAMs have exclusively used this effect for writing. The STT effect, however, can complement the field driven excitation of the magnetic free layer within an MTJ. Classical MRAM approaches use two perpendicular currents with a single selected MTJ at the intersection to create a magnetic field that acts on the free layer of an MTJ (see Fig. 1(a)). This approach suffers from several problems: (1) the use of two currents to switch a single bit consumes a large amount of energy as compared to DRAM, (2) the MTJs in adjacent columns and rows are half-selected by the high fields caused by the write currents, potentially inducing erroneous writes, and (3) a checker read operation [4] is required to ensure that the correct state is written into the device. These issues have limited the scalability of classical MRAM devices.

The STT effect overcomes these problems by using a single current that passes through the MTJ. This technique enables many MTJs to be written in parallel, as illustrated in Fig. 1(b). Moreover, the direction of the applied current corresponds to the final state of the MTJ, *i.e.*, a forward bias exclusively sets the device to "1," whereas a reverse current exclusively sets the device to "0." The switching current is much lower than in classical MRAM, eliminating the half select problem. The write latency, however, remains significantly longer than the read latency, and the switching energy is also significantly greater than DRAM. Supplying a sufficiently large write current requires a large access transistor, which reduces the density of the circuit.

The approach proposed herein combines an STT-based current with a field-generating current used in classical MRAM circuits. In this approach, the field current produces an additional magnetic field that destabilizes the MTJs across a row. Each MTJ is biased with an STT current that controls the switching direction of the MTJs in each column. Use of a field current in this manner has two beneficial effects: (1) the

This research is supported in part by the Binational Science Foundation under Grant No. 2012139, the National Science Foundation under Grant No. CCF-1329374, and by grants from Qualcomm, Cisco Systems, and Samsung.

Fig. 1. Current biasing scheme for a) classical MRAM, b) standard STT-MRAM, and c) the proposed STT-MRAM

alignment of the field with respect to the MTJ can destabilize the device, which reduces both the write latency and energy, and (2) the field current is shared across the row, ensuring that the energy consumption of the field current is amortized across all of the cells within a row. This technique ensures that the energy consumption per bit is less than standard STT-MRAM.

A proof of concept for field-assisted switching was first demonstrated in [5] specifically for high-density, off-chip main memories. Andre et al. presented a similar structure that utilizes a field current to set the MTJ device to an initial reset state (either  $R_{on}$  or  $R_{off}$ ) prior to writing the device. This method enables the uni-directional cells and the use of diodes to select the individual memory cells [6]. The approach presented here requires CMOS transistors for bipolar switching, and utilizes magnetic fields to enhance the dynamic behavior of the switching process to reduce the energy of a write, while sharing the field current to amortize the energy across multiple rows. The device is not reset to a stable state but rather an additional torque is applied dynamically to enhance the switching process. The approach presented here explores the design and memory sizing aspects associated with utilizing a field assisted approach and a relevant context for using these methods.

### IV. MODEL OF MRAM MEMORY CELL

The MTJ element is modeled using the classical Landau-Lifshitz-Gilbert single domain model and the simulation tool  $M^3$  [7]. The MTJ free layer parameters are selected to ensure that the thermal stability factor ( $\Delta$ ) provides ten year retention of the device state ( $\Delta = 40$ ). The MTJ parameters for resistance and TMR (from ITRS [8]) are listed in Table I. The critical switching current of the MTJ is dependent on the geometric and material properties of the free layer, permitting the current to be determined from the free layer geometry. The resultant critical current agrees with the switching current targeted by the ITRS.

The predictive technology model (PTM) is used to characterize the cell access transistor [9]. A low threshold transistor is used for the selection device and is modeled with a 20% reduction in threshold voltage. The word line is bootstrapped to  $V_{DD} + V_{th}$ . The cell transistor width is set to provide a switching current 1.5 times greater than the critical switching current. This width is selected to ensure that the device operates in precessional mode [10], while allowing the access transistor to be small. The parameters are listed in Table II.

TABLE I. MTJ PARAMETERS

| Sa                                | turation Magnetization $(M_s)$ | $8 \ge 10^{5} A/m$   |

|-----------------------------------|--------------------------------|----------------------|

| Easy Axis                         |                                | 80 nm                |

| H                                 | ard Axis                       | 20 nm                |

| Tł                                | nickness                       | 2.9 nm               |

| $\mathbf{R}$                      | on                             | $5 \text{ k}\Omega$  |

| ΤI                                | MR                             | 150%                 |

| $I_{crit}$                        |                                | 39.4 µA              |

|                                   | TABLE II.   MEMORY CELL PA     | ARAMETERS            |

|                                   | Technology                     | 22 nm                |

| Supply Voltage (V <sub>DD</sub> ) |                                | 0.8 V                |

| NMOS (W)                          |                                | 68.2 nm              |

| NMOS (L)                          |                                | 22 nm                |

| Field current line spacing        |                                | 21 nm                |

| Cell length                       |                                | 161 nm               |

| Cell width                        |                                | 167 nm               |

| Nominal switching current         |                                | 59.1 µA              |

|                                   | Nominal switching latency      | 6.45 <sup>'</sup> ns |

|                                   |                                |                      |

Durlam *et al.* present a classical MRAM cell and memory. Measurements of the field observed by the free layer are demonstrated at a distance of  $0.3 \,\mu\text{m}$  in a  $0.6 \,\mu\text{m}$  process. Simple linear scaling of this dimension is not sufficient as the MTJ dimensions are proportionally larger than a classical MRAM. To compensate, the MTJ dimensions are scaled linearly and the thickness of the MTJ stack is assumed to occupy an additional 10 nm. This thickness is typical of many demonstrated STT-MTJ stacks [11], [12].

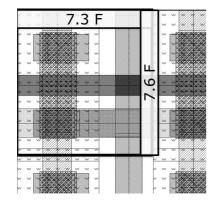

The cell layout is based on 45 nm FreePDK design rules and scaled to 22 nm, as shown in Fig 2. The cell area is  $55.5F^2$ . This cell has a relatively large cell density since the layout design rules originate from a logic process. In prior work, the area of a conventional 1T-1MTJ cell is shown to be  $49.9F^2$  with the same logic process rules, indicating that the area overhead of the metal line supporting the additional field current is small [13]. Note that a standalone memory process uses tighter design rules and provides greater density.

The magnetic field through a current loop can be approximated by the Bio-Savart's law [14],

$$B = \frac{\mu_0 I_{field}}{2\pi d}.$$

(1)

The current through the MTJ induces a spin torque on the

Fig. 2. Layout of a classical MRAM cell

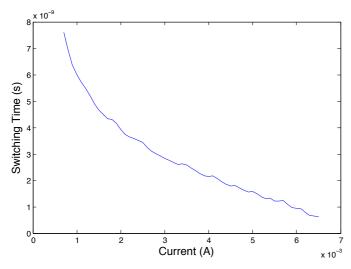

Fig. 3. Switching latency of a field driven classical MRAM cell. The STT switching current is 59.1  $\mu \rm A$

free layer, generating a magnetic field that adds linearly to the magnetic field generated by the field current. The magnetic field produced by the STT is assumed to be negligible for two reasons. The STT current is almost two orders of magnitude smaller than the field current, making the field generated by the STT current fairly small. Secondly, the field current is applied to the MTJ before the STT current is an unstable state prior to application of the STT current. As a result, the magnetic field of the STT current does not affect the destabilization process.

The switching latency with increasing field current is shown in Fig. 3. For a 59.1  $\mu A$  STT current, the MTJ switching latency is depicted as a function of increasing field current. The application of a field current is shown to dramatically reduce the switching time of the cell. Application of a 2 mA current reduces the nominal switching latency from 6.45 ns to 3.93 ns. A maximum applied current of 6.5 mA further reduces the switching latency to 617 *ps*.

#### V. MODEL OF MRAM ARRAY

Optimizing the energy consumed by an MRAM array with a field assisted write produces a tradeoff between the size of the array and the current bias that minimizes the switching time of an MTJ. The parasitic impedances of the array, extracted from the cell layout, are listed in Table III [9].

TABLE III. MEMORY ARRAY PARAMETERS

|                               | Base cell   Wide field lines |      |

|-------------------------------|------------------------------|------|

| $R_{\rm flcell}$ ( $\Omega$ ) | 1.7                          | 0.7  |

| C <sub>flcell</sub> (aF)      | 13.1                         | 28.8 |

The array is biased using a field current that traverses the entire row. As the size of the row increases, the energy associated with the field current is amortized over the entire row.

The energy associated with the field current is the sum of the dynamic energy to charge the line as well as the static current to generate the magnetic field. Expression (2) quantifies this dependance, where  $R_{flcell}$  and  $C_{flcell}$  describe the per cell parasitic resistance and capacitance, N describes the number of cells in a row,  $R_{access}$  describes the resistance of the access transistor,  $V_{DD}$  represents the supply voltage,  $t_{switching}$  is the MTJ switching latency, and  $I_{field}$  is the generated field current of the line. The dynamic component is a function of the array width and the DC voltage on the bitline during a write.

$$E_{field} = R_{flcell} C_{flcell} N \frac{N R_{flcell}}{N R_{flcell} + R_{access}} V_{DD} + V_{DD} I_{field}(t_{switching})$$

(2)

The energy of the static current is a function of the field current, supply voltage, and switching time of the MTJ. The static component is independent of array size as the supply voltage is constant and the voltage drop is across the peripheral write drivers and the array. The array field current is also constrained by the resistance of the field line,

$$I_{field}R_{flCell}N \le V_{DD}.$$

(3)

The energy to switch a single MTJ  $(E_{switch})$  is

$$E_{switch} = I_{STT} V_{DD} t_{switching},\tag{4}$$

where  $I_{STT}$  is the spin torque switching current.  $E_{switch}$  is dependent on the switching time of the MTJ. The total energy per bit is

$$E_{total} = E_{switch} + \frac{E_{field}}{N}.$$

(5)

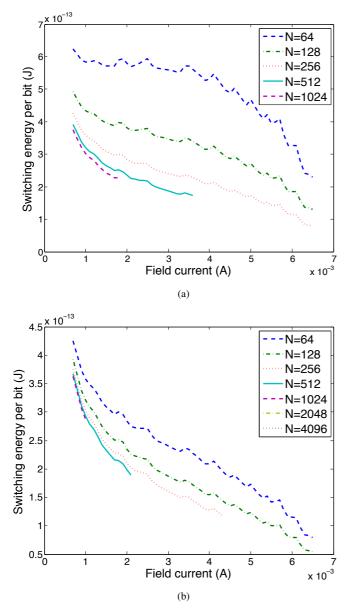

The switching energy is shown in Fig. 4(a). For comparison, the minimum energy to switch a nominal MTJ, as described by (4) for a non-field driven MRAM cell, is 0.3 pJ per bit. As illustrated in Fig. 4(a), the number of cells per row at which the field driven approach begins to reduce energy as compared to a nominal MTJ is approximately 64. For larger arrays, the resistance of the bitline constraints the amount of current that passed through the array. Despite this constraint on the maximum field current, the switching energy is reduced to 0.08 pJ per bit for a 64 cell wide array, a 73% reduction in switching energy.

While maintaining the same area and cell density, the metal lines used to generate the magnetic field can be increased to support a larger current. The resistance and capacitance of this

Fig. 4. Switching energy of a field driven classical MRAM cell with a) minimum metal pitch, and b) maximum allowed metal pitch

wide field current line are listed in Table III. The switching energy of the cell is further reduced to 0.054 pJ per bit (see Fig. 4(b)) with a corresponding switching latency of 617 ps. Due to the bitline resistance, larger rows support a maximum field current at a specific supply voltage. A sufficiently high field cannot be generated to reduce the switching latency of the MTJ, ensuring that the energy consumption is higher than with a shorter row. An optimum row length therefore exists that minimizes the overall switching energy of an array during a write. In the wide field line case, the optimum row length is 128 cells (see Fig. 4(b)).

#### VI. CONCLUSIONS

This proposed field-driven approach for enhancing latency and power in STT-MRAM is particularly useful for on-chip caches that require low latency, such as L1 caches, and register files within a pipeline. A high thermal stability factor is also required to provide a ten year state retention time. As demonstrated in [15], the retention time can be further reduced to lower the switching current. A reduced thermal switching factor, however, increases the likelihood of a half select problem [16].

The field driven approach utilized in classical MRAM cells is used to reduce the switching latency of an STT-MTJ. An array model is presented that is used to characterize the switching energy and energy consumption for different field currents and array sizes. It is shown that the per bit switching latency can be reduced by a factor of ten. As compared to nominal STT-MRAM, an 82% reduction in switching energy per bit is achieved. The reduction in both switching energy and latency provides significant performance enhancement for embedded high performance STT-MRAM based memories and enables the use of STT-MRAM in write latency critical applications.

#### REFERENCES

- M. Hosomi *et al.*, "A Novel Nonvolatile Memory with Spin Torque Transfer Magnetization Switching: Spin-RAM," *Proceedings of the IEEE International Electron Devices Meeting*, pp. 459–462, December 2005.

- [2] T. Kishi *et al.*, "Lower-Current and Fast Switching of a Perpendicular TMR for High Speed and High Density Spin-Transfer-Torque MRAM," *Proceedings of the IEEE International Electron Devices Meeting*, pp. 1–4, January 2008.

- [3] T. Kawahara et al., "2 Mb SPRAM (Spin-Transfer Torque RAM) with Bit-by-Bit Bi-Directional Current Write and Parallelizing-Direction Current Read," *IEEE Journal of Solid-State Circuits*, Vol. 43, No. 1, pp. 109–120, January 2008.

- [4] B. N. Engel et. al, "A 4-Mb Toggle MRAM Based On a Novel Bit and Switching Method," *IEEE Transactions on Magnetics*, Vol. 41, No. 1, pp. 132–136, January 2005.

- [5] W.C. Jeong, J.H. Park, J.H. Oh, G.T. Jeong, H.S. Jeong, and K. Kim, "Highly Scalable MRAM Using Field Assisted Current Induced Switching," *Proceedings of the IEEE Symposium on VLSI Technology*, pp. 184–185, June 2005.

- [6] T. Andre *et al.*, "Structures and Methods for a Field-Reset Spin-Torque MRAM," U.S. Patent 8,228,715, July 24, 2012.

- [7] C.K.A. Mewes and T. Mewes, "M<sup>3</sup> Micromagnetic Simulator," www. bama.ua.edu/~tmewes/Mcube/Mcube.shtml.

- [8] The ITRS Technology Working Groups, International Technology Roadmap for Semiconductors (ITRS), http://public.itrs.net.

- [9] W. Zhao and Y. Cao, "New Generation of Predictive Technology Model for Sub-45 nm Early Design Exploration," *IEEE Transactions* on Electron Devices, Vol. 53, No. 11, pp. 2816–2823, January 2006.

- [10] Y. Huai, "Spin-transfer torque MRAM (STT-MRAM): Challenges and prospects," AAPPS Bulletin, Vol. 18, No. 6, pp. 33–40, 2008.

- [11] H. Zhao et. al, "Low Writing Energy and Sub-Nanosecond Spin Torque Transfer Switching of In-Plane Magnetic Tunnel Junction for Spin Torque Transfer Random Access Memory," Journal of Applied Physics, Vol. 109, No. 7, pp. 07C720, April 2011.

- [12] S. Ikeda et. al, "A Perpendicular-Anisotropy CoFeB MgO Magnetic Tunnel Junction," *Nature Materials*, Vol. 9, No. 9, pp. 721–724, September 2010.

- [13] R. Patel, E. Ipek, and E. Friedman, "STT-MRAM Memory Cells with Enhanced On/Off Ratio," *Proceedings of the IEEE International System-on-Chip Conference*, pp. 148–152, September 2012.

- [14] F.T. Ulaby, E. Michielssen, and U. Ravaioli, Fundamentals of Applied Electromagnetics, Prentice Hall, 2010.

- [15] C W. Smullen et al., "Relaxing Non-Volatility for Fast and Energy-Efficient STT-RAM Caches," Proceedings of the IEEE International Symposium on High Performance Computer Architecture, pp. 50–61, June 2011.

- [16] D.D. Tang and Y.J. Lee, Magnetic Memory: Fundamentals and Technology, Cambridge University Press, 2010.