# HIGH INPUT VOLTAGE STEP-DOWN DC-DC CONVERTERS FOR INTEGRATION IN A LOW VOLTAGE CMOS PROCESS

Volkan Kursun, Siva G. Narendra<sup>1</sup>, Vivek K. De<sup>1</sup>, and Eby G. Friedman

Department of Electrical and Computer Engineering University of Rochester Rochester, New York 14627-0231 <sup>1</sup>Circuit Research, Intel Labs Intel Corporation Hillsboro, Oregon 97124

## ABSTRACT

A cascode bridge circuit for monolithic switching DC-DC converters operating at high input voltages is proposed in this paper. The proposed circuit can also be used as an I/O buffer to interface circuits operating at significantly different voltages. The circuit technique permits the full integration of the active and passive devices of a switching DC-DC converter with a high voltage conversion ratio in a standard low voltage CMOS technology. The cascode bridge structure guarantees the reliable operation of deep submicrometer MOSFETs without exposure to high voltage stress while operating at high input and output voltages. With the proposed circuit technique, steady-state voltage differences between the terminals of all of the MOSFETs in a switching DC-DC converter are maintained within a range imposed by a target low voltage CMOS technology. High-to-low DC-DC converters operating at input voltages up to three times as high as the maximum voltage that can be directly applied across the terminals of a MOSFET are described. An efficiency of 79.6% is achieved for 5.4 volts to 0.9 volts conversion assuming a 0.18 µm CMOS technology. The DC-DC converter operates at a switching frequency of 97 MHz while supplying a DC current of 250 mA to the load.

## **1. INTRODUCTION**

Supply voltage scaling is an essential step in the technology scaling process. Two primary reasons for scaling the supply voltage are to maintain the power density of an integrated circuit below a limit dictated by available cost effective cooling techniques and to guarantee the long term reliability of manufactured devices. Microprocessors, with increased power consumption and reduced supply voltages, demand greater amounts of current from external power supplies, creating an increasingly significant power generation and distribution problem (both onchip and off-chip) with each new technology generation [1], [2], [4]. Energy efficient, low noise power delivery has become increasingly challenging with the advancement of integrated circuit technologies.

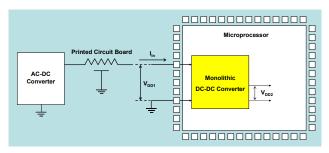

Voltages significantly higher than current board level voltages will become necessary to efficiently deliver greater levels of power to future high performance integrated circuits [1]. Distributing power at a higher voltage to the input pads of an integrated circuit reduces the supply current. At a reduced supply current, resistive voltage drops and parasitic power dissipation of the off-chip power distribution network is reduced, thereby enhancing the energy efficiency and quality of the distributed voltage [1]-[3]. Once the required energy reaches the input pads of a microprocessor, a lower supply voltage for the microprocessor circuitry can be generated by a monolithic DC-DC converter on the same die as the microprocessor, as shown in Fig. 1.

Fig. 1. High voltage off-chip power delivery and on-chip DC-DC conversion.

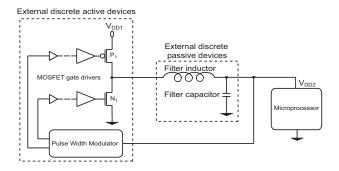

Monolithic DC-DC conversion on the same die as the load provides several desirable aspects [1], [2]. In a typical non-integrated switching DC-DC converter (as shown in Fig. 2), significant energy is dissipated in the parasitic impedances of the circuit board interconnect and among the discrete components of the regulator [1], [2]. As microprocessor current demands increase, the energy losses of the off-chip power generation increase, further degrading the efficiency of the DC-DC converters. Integrating both the active and passive devices of a DC-DC converter onto the same die as a microprocessor improves energy efficiency, enhances the quality of the voltage regulation, and decreases the number of I/O pads dedicated for power delivery on the microprocessor die. Furthermore, by employing an integrated circuit technology, the reliability of the voltage conversion circuitry can be enhanced, area can be reduced, and overall cost of the DC-DC converter can be decreased as compared to a discrete DC-DC converter [1], [2].

<sup>\*</sup>This research was supported in part by a grant from Intel Corporation.

Due to the advantages of high voltage power delivery on a circuit board and monolithic DC-DC conversion. next generation low voltage and high power microprocessors are likely to require high input voltage, large step down DC-DC converters monolithicly integrated onto the same die. The voltage conversion ratios attainable with standard non-isolated switching DC-DC converter circuits are, however, limited due to MOSFET reliability issues. In a standard buck converter circuit, as shown in Fig. 2, the input voltage  $V_{DD1}$  is limited to the maximum voltage  $V_{max}$  that can be directly applied across the terminals of a MOSFET in a specific fabrication technology. Provided that a DC-DC converter is integrated onto the same die as a microprocessor (fabricated in a low voltage deep submicrometer CMOS technology), the range of input voltages that can be applied to a standard DC-DC converter circuit is further reduced. A standard non-isolated switching DC-DC converter topology such as the standard buck converter circuit shown in Fig. 2 is, therefore, not suitable for future high performance integrated circuits. High efficiency monolithic switching DC-DC converters that can generate very low operating voltages from a significantly higher board level distribution voltage in a scaled nanometer CMOS technology are highly desirable.

Fig. 2. A standard off-chip buck converter circuit ( $V_{DD1} \le V_{max}$ ).

A cascode bridge circuit that can be used in a monolithic switching DC-DC converter providing a high voltage conversion ratio is proposed in this paper. The proposed circuit can also be used as an I/O buffer to interface circuits operating at significantly different voltages. The cascode circuit, when used as part of a voltage regulator, ensures that the voltages across the terminals of all of the MOSFETs in a DC-DC converter are maintained within the limits imposed by an available low voltage CMOS technology. With the proposed circuit technique, high-tolow non-isolated switching DC-DC converters have been designed based on a 0.18  $\mu$ m CMOS technology. An efficiency of 79.6% is demonstrated for a voltage conversion from 5.4 volts to 0.9 volts while supplying 250 mA of DC current. The paper is organized as follows. The cascode bridge circuit is described in Section 2. The operation and simulation results of the two voltage converters based on the proposed circuit technique are described in Section 3. Finally, some conclusions are offered in Section 4.

#### 2. CASCODE BRIDGE CIRCUIT

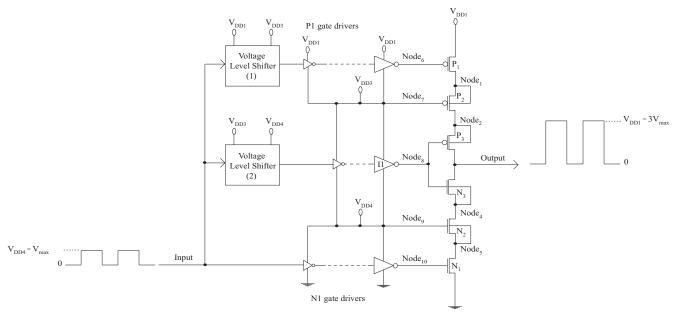

A cascode bridge circuit is described in this section. The circuit can operate at input voltages higher than the maximum voltage ( $V_{max}$ ) that can be applied directly across the terminals of a MOSFET in a deep submicrometer low voltage CMOS technology. The proposed cascode bridge circuit is shown in Fig. 3.

The cascode bridge circuit generates an output signal swinging between ground and  $V_{DD1}$  ( $V_{DD1} > V_{max}$ ) from an input control signal swinging between ground and  $V_{DD4}$ . The cascode bridge circuit guarantees that the voltages applied between the gate-to-source, gate-to-drain, gate-to-body, drain-to-body, and source-to-body terminals of the MOSFETs do not exceed the maximum voltage difference  $V_{max}$  permitted in a CMOS technology. As shown in Fig. 3, the input supply voltage  $V_{DD1}$  can be as high as three times  $V_{max}$  while complying with steady state voltage constraints across the terminals of all of the MOSFETs.

In Fig. 3,  $V_{DD1} = 3V_{max}$ ,  $V_{DD3} = 2V_{max}$ , and  $V_{DD4} = V_{max}$ . The number of inverters that drive Node<sub>8</sub> is even while the number of inverters that drive Node<sub>6</sub> and Node<sub>10</sub> is odd. The proposed circuit behaves in the following manner. When the input control signal transitions low, Node<sub>8</sub> is pulled down to  $V_{max}$ . Node<sub>6</sub> is pulled up to  $3V_{max}$ , turning off P<sub>1</sub>. Node<sub>10</sub> is pulled up to  $V_{max}$ , turning on N<sub>1</sub>. The output transitions low through N<sub>3</sub>, N<sub>2</sub>, and N<sub>1</sub>. Node<sub>2</sub> and Node<sub>1</sub> are discharged to  $V_{max}+|V_{tp}|$  and  $2V_{max}+|V_{tp}|$ , respectively.

When the input control signal transitions high, Node<sub>8</sub> is pulled up to  $2V_{max}$ . Node<sub>10</sub> is pulled down to ground, cutting off N<sub>1</sub>. Node<sub>6</sub> is pulled down to  $2V_{max}$ , turning on P<sub>1</sub>. The output is pulled up to  $3V_{max}$  through P<sub>1</sub>, P<sub>2</sub>, and P<sub>3</sub>. Node<sub>4</sub> and Node<sub>5</sub> are charged to  $2V_{max}$ -V<sub>tn</sub> and V<sub>max</sub>-V<sub>tn</sub>, respectively. The source and body terminals of P<sub>2</sub>, P<sub>3</sub>, N<sub>2</sub>, and N<sub>3</sub> are shorted to ensure that the maximum permitted source-to-body and drain-to-body junction reverse bias voltages and the maximum permitted gate-to-body voltage are not exceeded. With the proposed circuit technique, voltage differences between the terminals of all of the MOSFETs satisfy the steady-state voltage constraints dictated by a low voltage process technology while operating at high input and output voltages.

### 3. LARGE STEP-DOWN NON-ISOLATED SWITCHING DC-DC CONVERTER

A step-down DC-DC converter based on the cascode bridge circuit is presented in this section. The operation

Fig. 3. Cascode bridge circuit operating at an input supply voltage of  $V_{DD1} = 3V_{max}$  ( $V_{DD3} = 2V_{max}$  and  $V_{DD4} = V_{max}$ ).

of the DC-DC converter circuit is described in Section 3.1. Simulation results characterizing the maximum efficiency circuit configurations are presented in Section 3.2. A charge recycling mechanism in the cascode bridge circuit that significantly reduces the energy overhead of the proposed circuit technique is discussed in Section 3.3.

# 3.1. Operation of the DC-DC Converter

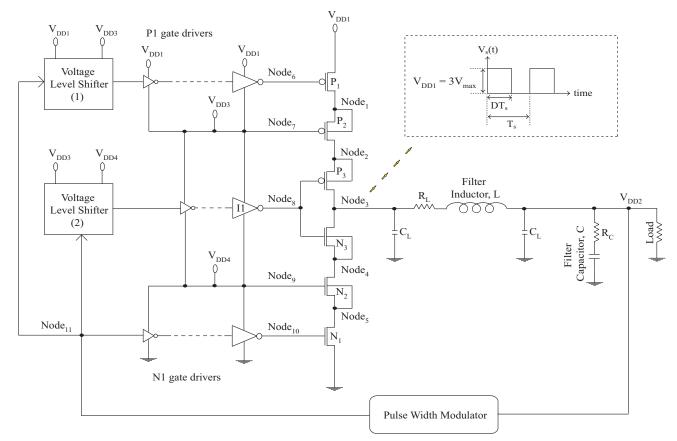

A high-to-low DC-DC converter operating at an input supply voltage of  $3V_{max}$  is shown in Fig. 4. The operation of the DC-DC converter circuit behaves in the following manner. The pull-up (P<sub>1</sub>, P<sub>2</sub>, and P<sub>3</sub>) and pull-down (N<sub>1</sub>, N<sub>2</sub>, and N<sub>3</sub>) network transistors produce an AC signal at Node<sub>3</sub> by a switching action controlled by a pulse width modulator. The AC signal at Node<sub>3</sub> is applied to a second order low pass filter composed of an inductor and a capacitor. The low pass filter passes the DC component of the AC signal at Node<sub>3</sub> to the output. A small amount of high frequency harmonics (assuming the filter corner frequency is much smaller than the switching frequency f<sub>s</sub> of the DC-DC converter) generated by the switching action of the MOSFETs also reaches the output due to the nonideal characteristics of the output filter.

The output voltage  $V_{DD2}(t)$  is

$$V_{DD2}(t) = V_{DD2} + V_{ripple}(t),$$

(1)

where  $V_{DD2}$  is the DC component of the output voltage and  $V_{ripple}(t)$  is the voltage ripple waveform observed at the output due to the nonideal characteristics of the output filter. The DC component of the output voltage is

$$V_{DD2} = \frac{1}{T_s} \int_{0}^{T_s} V_s(t) dt = DV_{DD1},$$

(2)

where  $V_s(t)$  is the AC signal generated at Node<sub>3</sub> and  $T_s$ , D, and  $V_{DD1}$  are the period, duty cycle, and amplitude, respectively, of  $V_s(t)$ . As given by (2), any positive DC output voltage less than  $V_{DD1}$  can be generated by the proposed DC-DC converter by varying the switching duty cycle D of the pull-up and pull-down network transistors.

#### 3.2. Simulation Results

Two high-to-low DC-DC converters have been designed based on the cascode bridge circuit. The maximum voltage that can be applied across the terminals of a MOSFET ( $V_{max}$ ) for a specific 0.18 µm CMOS technology is 1.8 volts. The DC-DC converter shown in Fig. 4 provides 5.4 volts ( $3V_{max}$ ) to 0.9 volts ( $V_{max}/2$ ) conversion while supplying 250 mA per phase DC current to the load.

Another DC-DC converter circuit has been designed for 4.5 volts  $(2.5V_{max})$  to 0.9 volts  $(V_{max}/2)$  conversion using a similar circuit topology as shown in Fig. 4. For the  $2.5V_{max}$  to  $V_{max}/2$  conversion,  $V_{DD3}$  and  $V_{DD4}$  are  $1.7V_{max}$  and  $0.8V_{max}$ , respectively, in order to enhance the gate drive of P<sub>1</sub>, P<sub>2</sub>, and P<sub>3</sub> and to further reduce the voltage stresses across the terminals of N<sub>1</sub>, N<sub>2</sub>, and N<sub>3</sub>.

Both DC-DC converters have been simulated assuming a 0.18 µm CMOS technology. Circuit parameters are

Fig. 4. Proposed DC-DC converter circuit operating at an input supply voltage of  $V_{DD1} = 3V_{max}$  ( $V_{DD3} = 2V_{max}$ ,  $V_{DD4} = V_{max}$ , and  $V_{DD2} < V_{DD1}$ ).

optimized to maximize efficiency while satisfying the output voltage and current requirements.

The efficiency of a DC-DC converter is

$$\eta = 100 \times \frac{P_{load}}{P_{load} + P_{internal}},$$

(3)

where  $P_{load}$  is the average power delivered to the load and  $P_{internal}$  is the average power dissipated in the internal parasitic impedances of a DC-DC converter. The optimized circuit configurations offering the highest efficiency are listed in Table 1.

As listed in Table 1, an efficiency of 79.6% is achieved with the proposed DC-DC converter circuit for 5.4 volts to 0.9 volts conversion. The circuit operates at a switching frequency of 97 MHz. The filter capacitor and inductor of this maximum efficiency circuit configuration are 3 nF and 15.5 nH, respectively. Similarly, an efficiency of 79.4% is observed for 4.5 volts to 0.9 volts conversion. The parasitic energy dissipation within the DC-DC converter is greater as the parasitic series resistances of the MOSFETs increase when the input supply voltage  $V_{DD1}$  is reduced from 5.4 volts to 4.5 volts. The efficiency achievable with the proposed DC-DC converter circuit is, therefore, slightly reduced when the conversion ratio is decreased from 6:1 to 5:1.

#### 3.3. Charge Recycling Mechanism

These high efficiencies achieved for such high voltage conversion ratios (6:1 and 5:1) are attributed to a charge recycling mechanism that exists in the cascode bridge circuit. At any time during a state changing transition of the pulse width modulator output (irrespective of the direction of the transition), a portion of the charge required by the inverters to drive Node<sub>8</sub> originates from discharging the parasitic capacitances of the gate drivers of P<sub>1</sub> rather than from the power supply  $V_{DD3}$ . Similarly, a significant portion of the charge required by the gate drivers of N1 for a low-to-high output transition originates from discharging the output parasitic capacitances of the gate drivers of P<sub>3</sub> and N<sub>3</sub> rather than from the power supply  $V_{DD4}$ . Most of the charge drawn from  $V_{DD1}$  during the low-to-high output transition of the buffers driving  $P_1$  is initially recycled for use inside the buffers driving Node<sub>8</sub>. This charge is eventually recycled for use within the buffers driving N<sub>1</sub> before finally being discharged to ground.

As listed in Table 1, the average current drawn from  $V_{DD3}$  and  $V_{DD4}$  is significantly smaller than the load current. The energy overhead of the two extra reference voltages required to properly operate the cascode bridge circuit is, therefore, small.  $V_{DD3}$  and  $V_{DD4}$  can be generated by simple integrated linear regulators without significantly affecting the overall efficiency of the DC-DC converters. For 5.4 volts to 0.9 volts conversion, the average current supplied by V<sub>DD3</sub> and V<sub>DD4</sub> are negative, meaning that the two extra power supplies essentially sink rather than supply current. For 4.5 volts to 0.9 volts conversion, the average current supplied by  $V_{DD3}$  and  $V_{DD4}$  are 7.6  $\mu$ A and 205  $\mu$ A, respectively. The primary purpose of V<sub>DD3</sub> and  $V_{DD4}$  is, therefore, to maintain the voltages at Node<sub>7</sub> and Node<sub>9</sub> at  $2V_{max}$  and  $V_{max}$  (1.7 $V_{max}$  and 0.8 $V_{max}$  for 4.5 volts to 0.9 volts conversion), respectively, rather than supplying current to the switching gate drivers.

TABLE 1 CIRCUIT CHARACTERISTICS OF THE MAXIMUM EFFICIENCY DC-DC CONVERTERS

| Conversion Ratio               | $2.5V_{max} \rightarrow V_{max}/2$ (5:1) | $\begin{array}{c} 3V_{max} \rightarrow V_{max}/2 \\ (6:1) \end{array}$ |

|--------------------------------|------------------------------------------|------------------------------------------------------------------------|

| V <sub>DD1</sub> (volts)       | 4.5                                      | 5.4                                                                    |

| V <sub>DD2</sub> (volts)       | 0.9                                      | 0.9                                                                    |

| V <sub>DD3</sub> (volts)       | 3.0                                      | 3.6                                                                    |

| V <sub>DD4</sub> (volts)       | 1.5                                      | 1.8                                                                    |

| I <sub>out</sub> (mA)          | 250                                      | 250                                                                    |

| Max $\eta$ (%)                 | 79.4                                     | 79.6                                                                   |

| f <sub>s</sub> (MHz)           | 97                                       | 97                                                                     |

| C (nF)                         | 3                                        | 3                                                                      |

| L (nH)                         | 14.8                                     | 15.5                                                                   |

| W <sub>N1</sub> (mm)           | 5.2                                      | 5.3                                                                    |

| W <sub>P1</sub> (mm)           | 7.2                                      | 4.8                                                                    |

| Total Transistor<br>Width (mm) | 41.3                                     | 34.1                                                                   |

| $I_{VDD3}$ ( $\mu A$ )         | 7.6                                      | -178                                                                   |

| $I_{VDD4}(\mu A)$              | 205                                      | -186                                                                   |

#### 4. CONCLUSIONS

A cascode bridge circuit for use in a monolithic switching DC-DC converter with a high voltage conversion ratio is proposed in this paper. The circuit can also be used as an I/O buffer to interface circuits operating at significantly different voltages without creating any MOSFET reliability issues due to the high voltage stress. The proposed circuit, when used as part of a voltage regulator, ensures that the voltages across the terminals of all of the MOSFETs in a monolithic DC-DC converter are maintained within the limits imposed by available low voltage CMOS technologies.

High-to-low DC-DC converters have been designed based on the cascode bridge circuit. Reliable operation of the DC-DC converters operating at an input supply voltage up to three times as high as the maximum voltage ( $V_{max}$ ) that can be directly applied across the terminals of a MOSFET is verified assuming a 0.18 µm CMOS technology. The energy overhead of the proposed circuit technique is low due to a charge recycling mechanism in the MOSFET gate drivers. An efficiency of 79.6% is demonstrated for a voltage conversion from 5.4 volts to 0.9 volts while supplying 250 mA of DC current.

## ACKNOWLEDGMENTS

The authors would like to thank Tanay Karnik and Peter Hazucha of Intel Corporation for their contributions to this work.

#### **5. REFERENCES**

[1] V. Kursun, S. G. Narendra, V. K. De, and E. G. Friedman, "Monolithic DC-DC Converter Analysis and MOSFET Gate Voltage Optimization," *Proceedings of the IEEE/ACM International Symposium on Quality Electronic Design*, pp. 279-284, March 2003.

[2] V. Kursun, S. G. Narendra, V. K. De, and E. G. Friedman, "Analysis of Buck Converters for On-Chip Integration with a Dual Supply Voltage Microprocessor," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, Vol. 11, No. 3, pp. 514-522, June 2003.

[3] Y. Panov and M. M. Jovanovic, "Design and Performance Evaluation of Low-Voltage/High-Current DC/DC On-Board Modules," *IEEE Transactions on Power Electronics*, Vol. 16, No. 1, pp. 26-33, January 2001.

[4] D. M. Monticelli, "Taking a System Approach to Energy Management," *Proceedings of the European Solid-State Circuits Conference*, pp. 15-19, September 2003.

[5] R. W. Erickson and D. Maksimovic, *Fundamentals of Power Electronics*, Norwell, MA: Kluwer Academic Publishers, 2001.

[6] V. Kursun, S. G. Narendra, V. K. De, and E. G. Friedman, "Low Voltage Swing Monolithic DC-DC Conversion," *IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing* (in press).

[7] V. Kursun, S. G. Narendra, V. K. De, and E. G. Friedman, "Efficiency Analysis of a High Frequency Buck Converter for On-Chip Integration with a Dual- $V_{DD}$  Microprocessor," *Proceedings of the European Solid-State Circuits Conference*, pp. 743-746, September 2002.