# Exploiting the On-Chip Inductance in High-Speed Clock Distribution Networks

Yehea I. Ismail, Member, IEEE, Eby G. Friedman, Fellow, IEEE, and Jose L. Neves

*Abstract*—On-chip inductance effects can be used to improve the performance of high-speed integrated circuits. Specifically, inductance improves the signal slew rate (the rise time), virtually eliminates short-circuit power consumption and reduces the area of the active devices and repeaters inserted to optimize the performance of long interconnects. These positive effects suggest the development of design strategies that benefit from on-chip inductance. An example of a clock distribution network is presented to illustrate the process in which inductance can be used to improve the performance of high-speed integrated circuits.

Index Terms—Clock distribution, CMOS, inductance, power, RLC.

#### I. INTRODUCTION

T HE importance of on-chip inductance is continuously increasing with faster on-chip rise times, wider wires, and the introduction of new materials for low resistance interconnect [1]–[16]. These increasing inductance effects are typically viewed as an added problem that must be reckoned with, which is accurate in many respects. Dealing with inductance requires efficient extraction methods [3]–[7], [11] and increases the processing time of computer-aided design (CAD) tools. Furthermore, underdamped responses can cause reliability issues and increase noise in integrated circuits. However, the concern over on-chip inductance is primarily due to the lack of a thorough understanding of the related effects and an insufficient sophistication of the tools and methods that are available for designing and analyzing high performance integrated circuits.

To date, much of the effort within industry has focused on limiting the effects of inductance, e.g., [1], [8], and [10]. However, suppressing inductance effects is typically at the expense of deteriorating the performance of an integrated circuit in terms of speed, power consumption, and/or device area. An example of a clock distribution network is presented toward the end of this paper that illustrates this point. As described here, inductance has beneficial effects on integrated circuits such as faster signal rise times, lower power consumption, and less active device area. Design methodologies can be developed to exploit these useful effects of on-chip inductance while maintaining noise at acceptable levels so as to guarantee the reliable performance of an integrated circuit.

Manuscript received March 27, 2001; revised June 6, 2001.

J. L. Neves is with IBM Microelectronics, Fishkill, NY 12533 USA.

Publisher Item Identifier S 1063-8210(01)04734-5.

The goal of this paper is to briefly describe these beneficial effects of inductance on the performance of an integrated circuit, which are presented in Section II. The design of a clock distribution network is presented in Section III to illustrate how inductance effects can significantly improve circuit performance. Finally, some conclusions are given in Section IV.

### **II. USEFUL INDUCTANCE EFFECTS**

The effects of inductance on the rise time of signals within an integrated circuit is discussed in Section II-A. It is shown that increasing inductance effects result in faster signal rise times. In Section II-B, the effects of inductance on the area of repeaters inserted to reduce signal degradation along long interconnects is discussed. It is shown that the total repeater area decreases as inductance effects increase. The effects of inductance on the power dissipated by CMOS gates is discussed in Section II-C, particularly the dramatic decrease in the short-circuit power consumption of CMOS gates. Also, the decreased device area required to drive inductive lines results in less device capacitance, which further decreases the total power consumption.

## A. Effects of Inductance on the Signal Rise Time

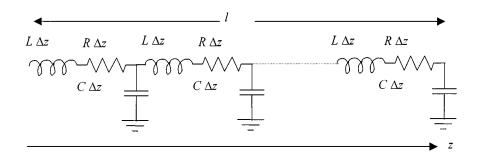

The faster rise times of signals in a high-speed integrated circuit as inductance effects increase can be best explained by examining the signal propagation characteristics in a lossy RLC transmission line (see Fig. 1). Signals propagating across an RLC transmission line travel with a frequency dependent velocity given by

$$v = \frac{1}{\sqrt{LC}\sqrt{(1/2)(\sqrt{(1+(R/\omega L)^2)}+1)}}$$

(1)

where R, L, and C are the resistance, inductance, and capacitance per unit length of the line, respectively, and  $\omega$  is the radial frequency. Furthermore, the signals attenuate as they travel across the line with an attenuation constant  $\alpha$  given by [13]

$$\alpha = \omega \sqrt{LC} \sqrt{\frac{1}{2} \left( \sqrt{\left( 1 + \left( \frac{R}{\omega L} \right)^2 \right)} - 1 \right)}.$$

(2)

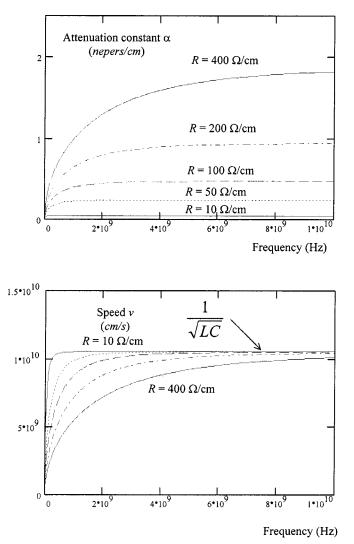

The attenuation constant and the speed of propagation as functions of frequency are plotted in Fig. 2 with L = 10 nH/cm, C = 1 pF/cm, and with variable R. The frequency components of a signal launched at the input of an RLC transmission line

Y. I. Ismail is with the Department of Electrical and Computer Engineering, Northwestern University, Evanston, IL 60208 USA (e-mail: ismail@ece.northwestern.edu).

E. G. Friedman is with the Department of Electrical and Computer Engineering, University of Rochester, Rochester, NY 14627 USA.

Fig. 1. RLC transmission line.

Fig. 2. The attenuation constant and propagation speed versus frequency. L = 10 nH/cm, C = 1 pF/cm, and R is 10, 50, 100, 200, and 400  $\Omega/$ cm, respectively.

travel at different speeds and suffer different levels of attenuation. As shown in Fig. 2, higher frequency components at the edges of a pulse suffer greater attenuation as compared to any low frequency components. The shape of a signal degrades as the signal travels across a lossy transmission line due to the loss of these high-frequency components. Both the attenuation constant and the speed of propagation become less frequency dependent as inductance effects increase or as  $R/\omega L$  decreases as shown in Fig. 2. In the limiting case of a lossless line representing maximum inductance effects, the attenuation constant  $\alpha$ is zero and the propagation speed becomes frequency independent and is

$$v = \frac{1}{\sqrt{LC}}.$$

(3)

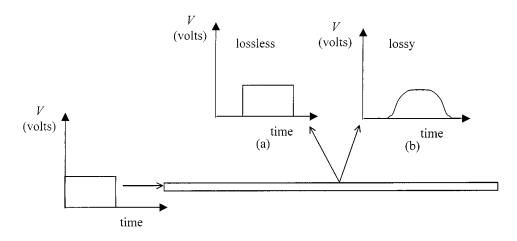

Thus, as inductance effects increase, a pulse propagating across an RLC line maintains the high-frequency components in the edges, improving the signal rise and fall times. This behavior is qualitatively illustrated in Fig. 3.

#### B. Effects of Inductance on the Repeater Insertion Process

Repeater insertion has become a common design methodology for driving long resistive interconnect [18]–[24]. Since the propagation delay has a square dependence on the length of an RC interconnect line, subdividing the line into shorter sections by inserting repeaters is an effective strategy for reducing the total propagation delay. Currently, typical high-performance circuits have a significant number of repeaters inserted along the global interconnect lines. These repeaters are large gates and consume a significant portion of the total circuit power.

The propagation delay from the input to the output of an RLC line of length l with an ideal power supply and an open circuit load is given by [25]

$$t_{\rm pd} = \sqrt{LC} (\exp\left[-2.9(\alpha_{\rm asym}l)^{1.35}\right] l + 0.74\alpha_{\rm asym}l^2)$$

(4)

where

$$\alpha_{\rm asym} = \frac{R}{2} \sqrt{\frac{C}{L}}.$$

(5)

$\alpha_{asym}$  is the asymptotic value at high frequencies of the attenuation per unit length of the signals as the signals propagate across a lossy transmission line as shown in Fig. 2.

For the limiting case where  $L \rightarrow 0$ , (4) reduces to  $0.37RCl^2$ . Again, note the square dependence on the length of an RC wire. For the other limiting case where  $R \rightarrow 0$ , the propagation delay is given by  $l\sqrt{LC}$ . Note the linear dependence on the length of the line. Inserting repeaters in an LC line only increases the total delay due to the added gate delay. Thus, an LC line requires zero repeater area to minimize the overall propagation delay.

In the general case of an RLC line, the optimal repeater area for minimum propagation delay is between the maximum repeater area in the RC case and the zero repeater area in the LC

Fig. 3. Signal dispersion of a square wave signal in a lossy transmission line. (a) Pulse shape after traveling along a lossless transmission line. (b) Pulse shape after traveling along a lossless transmission line.

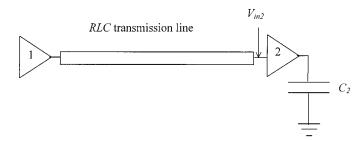

Fig. 4. A CMOS gate driving another CMOS gate with an RLC transmission line connecting the two gates. The second gate drives a capacitive load.

case. The repeater area for minimum propagation delay of an RLC line decreases as the inductance effects increase due to the subquadratic dependence of the propagation delay on the length of the interconnect [25]. Hence, inserting repeaters based on an *RC* model and neglecting inductance results in a larger repeater area than necessary to achieve a minimum delay. The magnitude of the excess repeater area when using an RC model depends upon the relative magnitude of the inductance within the RLCtree. The reduced number of inserted repeaters also simplifies the layout and routing constraints. Finally, the reduced repeater area greatly reduces the power consumed by the repeaters in an integrated circuit. A more thorough analytical analysis of the effect of inductance on the repeater insertion process can be found in [25]. Also, an algorithm was introduced in [26] to insert repeaters in tree structure *RLC* interconnect. The algorithm was applied to several industrial copper interconnect trees and the results illustrates that an increase in inductance effects decreases the number of repeaters inserted for optimum delay [26].

#### C. Effects of Inductance on Power Dissipation

Power consumption is an increasingly important design parameter with mobile systems and high performance, high complexity circuits such as leading edge microprocessors. If the frequency of switching is f cycles per second, then the dynamic power consumption is described by the well-known formula

$$P_{\rm dyn} = C_t V_{\rm DD}^2 f. \tag{6}$$

The dynamic power depends only on the total load capacitance, the supply voltage, and the operating frequency. As discussed in Section II-B, increasing inductance effects result in fewer number of repeaters as well as smaller repeater size. The smaller size and number of repeaters, therefore, significantly reduces the total capacitance of the repeaters and, consequently, reduces the total dynamic power consumption.

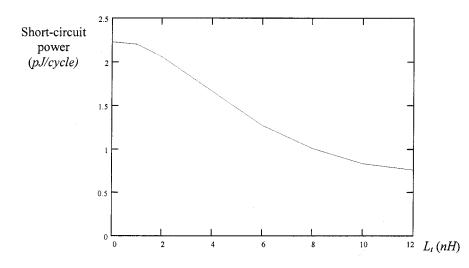

The short-circuit power [27]-[29] results from the NMOS and PMOS blocks of a CMOS gate being on simultaneously during the rise and fall times of the input signal, creating a current path between the power supply and ground. As discussed in Section II-A, the inductance reduces the rise time of the signals in an integrated circuit, reducing the short-circuit power. To quantify this effect, consider the circuit configuration shown in Fig. 4. A fast input signal drives CMOS gate 1, which in turn drives an *RLC* transmission line. The output at the far end of the *RLC* transmission line is the input to the second gate  $V_{in2}$ . Gate 2 drives a capacitive load  $C_2$ . The short-circuit energy consumed by gate 2 per cycle is listed in Table I, where the total inductance of the transmission line is varied while the resistance and capacitance are maintained constant. The data listed in Table I is also plotted in Fig. 5. Note that as inductance effects increase, the short-circuit power consumption significantly decreases due to the faster input rise time.

The effect of smaller repeater sizes on the short-circuit power consumption is significant. By decreasing the widths of the transistors, the short-circuit current decreases because the current drive of the NMOS and PMOS transistors is linearly proportional to the transistor width. Also, by decreasing the width of the transistors, the output transition time becomes slower which

Fig. 5. Simulations of the short-circuit energy consumed per cycle by gate 2 shown in Fig. 4 versus the inductance of the transmission line. The total resistance and capacitance of the line are maintained constant at 100  $\Omega$  and 1 pF, respectively.

TABLE I SIMULATIONS OF THE SHORT-CIRCUIT ENERGY CONSUMED PER CYCLE BY GATE 2 SHOWN IN FIG. 4. THE TOTAL INDUCTANCE OF THE TRANSMISSION LINE IS VARIED WHILE THE RESISTANCE AND CAPACITANCE ARE HELD CONSTANT AT 100  $\Omega$  and 1 pF, Respectively

| Total inductance of the line $L_t$ ( <i>nH</i> ) | Short-circuit power at gate 2 ( <i>pJ/cycle</i> ) |  |

|--------------------------------------------------|---------------------------------------------------|--|

| 1                                                | 2.20<br>2.05<br>1.66<br>1.27                      |  |

| 2                                                |                                                   |  |

| 4                                                |                                                   |  |

| 6                                                |                                                   |  |

| 8                                                | 1.00                                              |  |

| 10                                               | 0.83                                              |  |

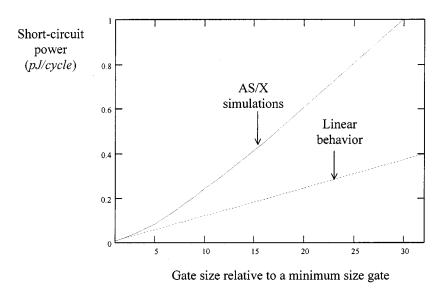

decreases the source-to-drain voltage of the transistor passing the short-circuit current. Since the output current is proportional to the source-to-drain voltage of a MOS transistor operating in the linear region, the short-circuit current is smaller with decreasing transistor size. Thus, decreasing the transistor sizes has a two fold effect on the short-circuit power. In general, the shortcircuit power has a super linear dependence on gate size. AS/X<sup>1</sup> [17] simulations of the short-circuit energy/cycle of a CMOS gate driving a constant capacitance of 0.2 pF with a 100-ps input rise time versus gate size are depicted in Fig. 6. The super linear behavior is evident in Fig. 6. Thus, the smaller repeater size and number significantly reduces the overall short-circuit power. Finally, it has been shown in [29] that the short-circuit power consumption of a CMOS gate decreases as the inductance of the driven net becomes more significant.

#### **III. CLOCK DISTRIBUTION NETWORK EXAMPLE**

The clock distribution network significantly affects the performance of an integrated circuit and consumes a large portion of the total chip power (typically 30 to 40%) [30], [31]. Designing an efficient and reliable clock distribution network is of primary importance for a high-performance integrated circuit. To illustrate the concepts discussed in Section II, the clock distribution network of an integrated circuit is investigated. The integrated circuit has been designed using a 0.18- $\mu$ m IBM CMOS technology with copper interconnect. The supply voltage for this technology is 1.8 V and the target frequency of the circuit is 250 MHz. The integrated circuit has four primary modules and several other smaller modules.

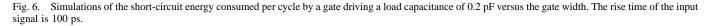

The clock distribution network at the top level is composed of a wide buffer that drives a four-node H tree carrying the clock signal to the center of the four quadrants of the integrated circuit. At the center of each of the four quadrants, a local central wide buffer receives the clock signal and drives the local clock distribution network of each quadrant. Each local central buffer drives a clock tree connected to an average of 1350 sinks. At each sink, a final buffer (a CMOS inverter) receives the clock signal and drives the final group of flip flops. Each of the final buffers drives a capacitive load of approximately 250 fF. The structure of the local clock distribution network of this module is schematically depicted in Fig. 7.

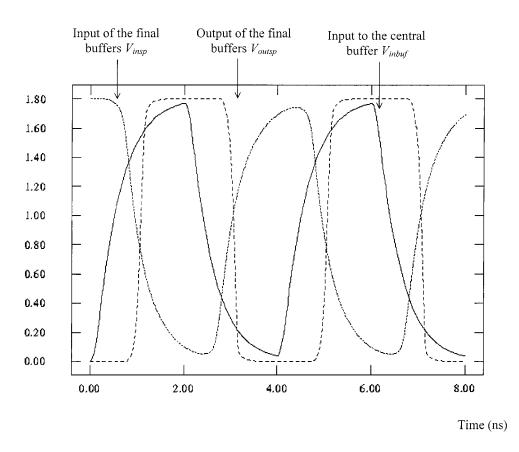

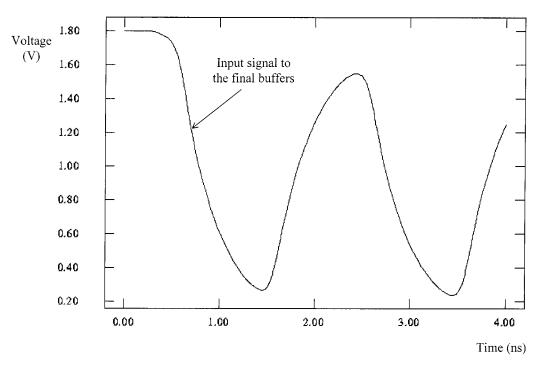

The top level and local clock distribution networks have been initially simulated with wires sized to satisfy the design constraints of the clock tree. The slew should be within 5% of the clock period at the input of the latches and the clock delay (or the phase delay) must be less than the clock period. AS/X [17] simulated waveforms at the input of the central buffer  $V_{inbuf}$  and at the inputs of the final buffers  $V_{insv}$  are shown in Fig. 8. The initial choice of wire sizes results in degraded signal waveforms on the internal nodes of the clock distribution network. Note that the rise time of the signals illustrated in Fig. 8 is greater than one ns. The final buffers restore the signal rise time to 200 ps at the input of the local flip flops  $V_{\text{outsp}}$ . This faster rise time is necessary to maintain stable operation of the flip flops. Thus, the performance of the clock distribution network satisfies a target cycle period of 4 ns. Note also that this clock distribution network suffers no inductance effects, therefore, an RC model can be used to model the clock distribution network.

<sup>&</sup>lt;sup>1</sup>AS/X is a dynamic circuit simulator developed and used by IBM. AS/X is similar to SPICE but has a specific emphasis on transmission line networks and uses the ASTAP language for describing the circuit in the input files.

Fig. 7. Local clock distribution network of a primary quadrant of a large integrated circuit.

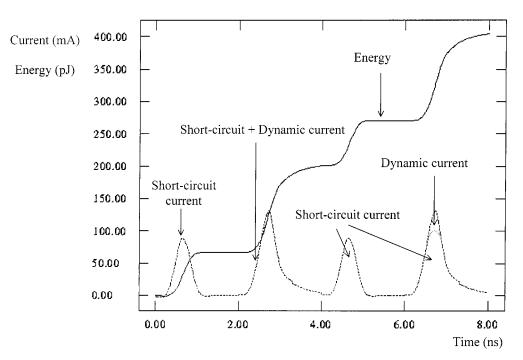

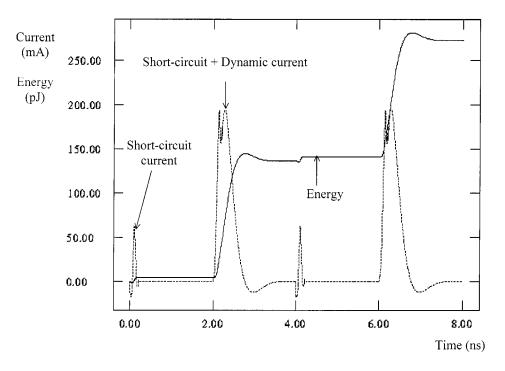

The power consumption of the clock distribution network, however, is excessively high due to the slow signal rise times at the inputs of the central buffer and the final buffers. AS/X simulations of the dynamic and short-circuit power consumption of the central buffer are shown in Fig. 9. The current depicted in Fig. 9 is drawn from the supply voltage  $V_{DD}$  through the PMOS network. When the output is pulled down, this current represents

the short-circuit current. When the output is pulled high, the current from the supply represents the sum of the short-circuit current (through the N-channel transistor) and the dynamic current charging the output capacitance. The energy shown in Fig. 9 is the integration of the supply current multiplied by the supply voltage and represents the total energy consumed by the gate at any given time. Note in Fig. 9 that the short-circuit power is

Fig. 8. AS/X [17] simulations of the signals at the input of the central buffer  $V_{inbuf}$ , at the input of the final buffers  $V_{insp}$ , and at the output of the final buffers  $V_{outsp}$  for the local clock distribution network shown in Fig. 7 with narrow wires.

Fig. 9. AS/X [17] simulations of the dynamic current, short-circuit current, and energy of the central buffer in the local clock distribution network depicted in Fig. 7 with narrow wires.

much higher than the dynamic power consumption, constituting about 80% of the total power consumption of the central buffer. This large amount of short-circuit current directly contradicts the common conception that the short-circuit power contributes less than 20% of the total power consumption [27], [28]. This 20% figure is typically true when the input and output rise times are close to each other. However, for this clock distribution network example, the input rise time is extremely slow and the final

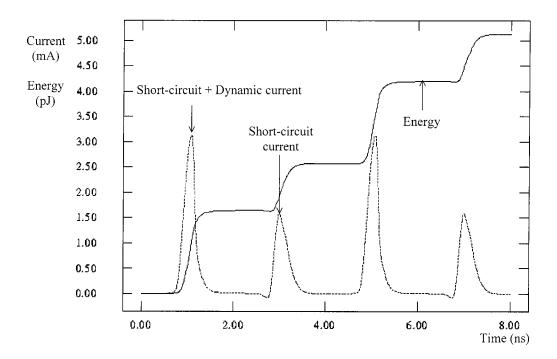

Fig. 10. AS/X [17] simulations of the dynamic current, short-circuit current, and energy of one of the final buffers in the local clock distribution network depicted in Fig. 7 with narrow wires.

TABLE II DYNAMIC AND SHORT-CIRCUIT ENERGY OF THE CENTRAL BUFFER AND THE FINAL BUFFERS IN THE LOCAL CLOCK DISTRIBUTION NETWORK DEPICTED IN FIG. 7 WITH NARROW WIRES

|                                                | Dynamic power<br>(pJ/cycle) | Short-circuit power<br>(pJ/cycle) | Total power<br>(pJ/cycle) |

|------------------------------------------------|-----------------------------|-----------------------------------|---------------------------|

| Central buffer                                 | 68                          | 133                               | 201                       |

| Single final buffer                            | 0.71                        | 1.86                              | 2.57                      |

| All final buffers                              | 958                         | 2511                              | 3469                      |

| Local clock<br>distribution network<br>(total) | 1026                        | 2644                              | 3670                      |

TABLE III

THE POWER CONSUMPTION OF THE CENTRAL BUFFER, THE FINAL BUFFERS, AND THE CLOCK DISTRIBUTION NETWORK IN FIG. 7 WHEN WIDER WIRES ARE USED AS COMPARED TO A NARROW WIRE IMPLEMENTATION

| Total power dissipation<br>(pJ/cycle) | Old design<br>(narrow wires) | New design<br>(wider wires) | % power savings |

|---------------------------------------|------------------------------|-----------------------------|-----------------|

| Central buffer                        | 201                          | 137                         | 31.8%           |

| All final buffers                     | 3469                         | 1445                        | 58.3%           |

| Local clock distribution network      | 3670                         | 1582                        | 56.9%           |

buffers provide sufficient current to enable small rise times of 200 ps at the inputs of the flip flops. AS/X simulations of the dynamic and short-circuit power of one of the final buffers are shown in Fig. 10. Note again that the short-circuit power dominates the dynamic power. The dynamic and short-circuit power consumption of the central buffer and the final buffers are listed separately in Table II.

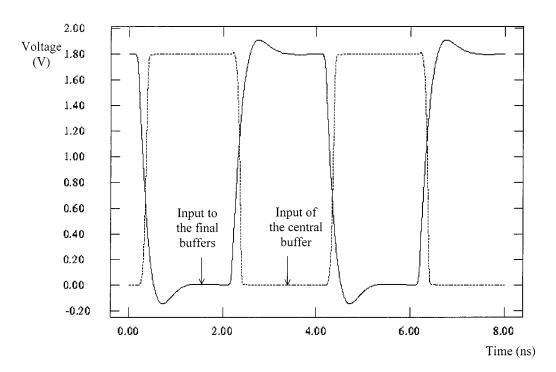

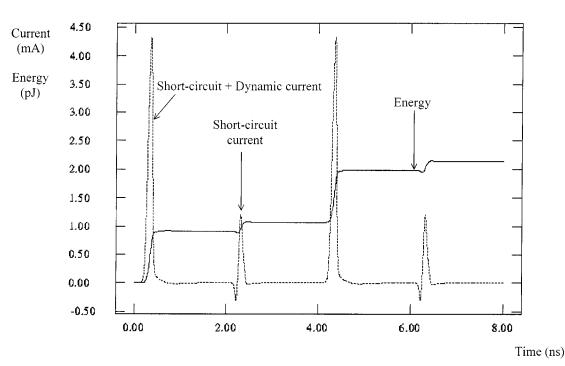

To decrease the power dissipated by the final buffers, the clock distribution network is rerouted with wires twice as wide as the original wires. Simulations of the signals at the input of the central buffer and the final buffers are shown in Fig. 11. The rise time of these signals is below 200 ps. The short-circuit and dynamic power of the central buffer and a single final buffer are shown in Figs. 12 and 13, respectively. Note that the dynamic power consumption of the central buffer has increased due to the increased capacitance of the wider wires driven by the central buffer. However, the faster input rise time has effectively eliminated the short-circuit power, reducing the total power consumption of the central buffer. The short-circuit power consumption of the central buffer. The short-circuit

Fig. 11. AS/X [17] simulations of the signals at the inputs of the central buffer and the final buffers in the local clock distribution network depicted in Fig. 7 with wider wires.

Fig. 12. AS/X [17] simulations of the dynamic current, short-circuit current, and energy of the central buffer in the local clock distribution network depicted in Fig. 7 with wider wires.

while the dynamic power remains constant since the load of the final buffers has not changed. The power consumption of the redesigned clock distribution network is compared to the power consumption of the original clock distribution network design in Table III.

Note that the effects of inductance are now prominent with the use of wider wires in the clock distribution network, requiring that inductance be included in the interconnect model. This example illustrates that exposing inductance effects can improve the performance of an integrated circuit and that penalties in rise time, delay, and/or power consumption are incurred if these effects are eliminated. The overshoot that appears in the signal waveforms shown in Fig. 13 does not cause any significant reliability problems. In certain cases, the increased power can be tolerated. However, if the original clock distribution network is intended to operate at 500 MHz, the signals at the inputs of the

Fig. 13. AS/X [17] simulations of the dynamic current, short-circuit current, and energy of one of the final buffers in the local clock distribution network depicted in Fig. 7 with wider wires.

Fig. 14. AS/X [17] simulations of the signal at the input of a final buffer in the local clock distribution network operating at 500 MHz as depicted in Fig. 7 with narrow wires.

final buffers become problematic as shown in Fig. 14. Note that the signals do not reach the required logic levels and the voltage swing is reduced, decreasing the noise margin. Such signals are unacceptable in a high-performance integrated circuit. In this case, wider wires are not only necessary to reduce the power but to also maintain reliable operation of the integrated circuit (IC). To achieve sufficiently fast signal rise times while maintaining reliable operation at high clock frequencies, wider drivers and wires should be used, resulting in greater inductance effects.

#### IV. SUMMARY

It is shown in this paper that on-chip inductance can be exploited to improve the performance of high-speed integrated circuits. Specifically, inductance improves the signal slew rate, dramatically reduces the short-circuit power consumption, and reduces the area of the active repeaters inserted to optimize the performance of long interconnects. These beneficial effects encourage design strategies that can exploit on-chip inductance. AS/X simulations of a clock distribution network have been presented to illustrate how inductance can be used to improve the performance of high speed integrated circuits. The power consumption of the clock distribution network decreases from 3670 pJ/cycle to 1582 pJ/cycle and the slew rate decreases from 1.2 ns to 200 ps on the internal nodes of the clock distribution network when wider, more inductive, wires are used.

#### REFERENCES

- D. A. Priore, "Inductance on silicon for submicron CMOS VLSI," in *Proc. IEEE Symp. VLSI Circuits*, May 1993, pp. 17–18.

- [2] D. B. Jarvis, "The effects of interconnections on high-speed logic circuits," *IEEE Trans. Electron. Comput.*, vol. EC-10, pp. 476–487, Oct. 1963.

- [3] M. P. May, A. Taflove, and J. Baron, "FD-TD modeling of digital signal propagation in 3-D circuits with passive and active loads," *IEEE Trans. Microwave Theory and Techniques*, vol. 42, pp. 1514–1523, Aug. 1994.

- [4] Y. Eo and W. R. Eisenstadt, "High-speed VLSI interconnect modeling based on S-parameter measurement," *IEEE Trans. Components, Hybrids, and Manuf. Technol.*, vol. 16, pp. 555–562, Aug. 1993.

- [5] A. Deutsch et al., "High-speed signal propagation on lossy transmission lines," *IBM J. Research Development*, vol. 34, no. 4, pp. 601–615, July 1990.

- [6] —, "Modeling and characterization of long interconnections for highperformance microprocessors," *IBM J. Research Development*, vol. 39, no. 5, pp. 547–667, Sept. 1995.

- [7] —, "When are transmission-line effects important for on-chip interconnections?," *IEEE Trans. Microwave Theory and Tech.*, vol. 45, pp. 1836–1846, Oct. 1997.

- [8] M. Shoji, *High-Speed Digital Circuits*. Reading, MA: Addison-Wesley, 1996.

- [9] A. Duetsch, A. Kopcsay, and G. V. Surovic, "Challenges raised by long on-chip wiring for CMOS microprocessors," in *Proc. IEEE Topical Meet. Electrical Performance of Electronic Packaging*, Oct. 1995, pp. 21–23.

- [10] Y. Massoud, S. Majors, T. Bustami, and J. White, "Layout Techniques for minimizing on-chip interconnect self inductance," in *Proc. IEEE/ACM Design Automation Conf.*, June 1998, pp. 566–571.

- [11] B. Krauter and S. Mehrotra, "Layout Based Frequency Dependent Inductance and Resistance Extraction for On-Chip Interconnect Timing Analysis," in *Proc. IEEE/ACM Design Automation Conf.*, June 1998, pp. 303–308.

- [12] A. Duetsch *et al.*, "Design Guidelines for Short, Medium, and Long On-Chip Interconnect," in *Proc. IEEE Topical Meet. Electrical Performance of Electronic Packaging*, Oct. 1996, pp. 30–32.

- [13] Y. I. Ismail, E. G. Friedman, and J. L. Neves, "Figures of merit to characterize the importance of on-chip inductance," in *Proc. IEEE/ACM De*sign Automation Conf., June 1998, pp. 560–565.

- [14] L. T. Pillage, "Coping with RC(L) interconnect design headaches," in Proc. IEEE/ACM Int. Conf. Computer-Aided Design, Sept. 1995, pp. 246–253.

- [15] J. Torres, "Advanced Copper Interconnections for Silicon CMOS Technologies," *Appl. Surface Sci.*, vol. 91, no. 1, pp. 112–123, Oct. 1995.

- [16] P. J. Restle and A. Duetsch, "Designing the best clock distribution network," in *Proc. IEEE VLSI Circuit Symp.*, June 1998, pp. 2–5.

- [17] AS/X User's Guide, IBM Corp., New York, 1996.

- [18] L. V. Ginneken, "Buffer Placement in Distributed RC-tree Networks for Minimal Elmore Delay," in *Proc. IEEE Int. Symp. Circuits and Systems*, May 1990, pp. 865–868.

- [19] V. Adler and E. G. Friedman, "Delay and power expressions for a CMOS inverter driving a resistive-capacitive load," *Analog Integrat. Circuits Signal Processing*, vol. 14, no. 1/2, pp. 29–39, Sept. 1997.

- [20] H. B. Bakoglu and J. D. Meindl, "Optimal interconnection circuits for VLSI," *IEEE Trans. Electron Devices*, vol. ED-32, pp. 903–909, May 1985.

- [21] H. B. Bakoglu, Circuits, Interconnections, and Packaging for VLSI. Reading, MA: Addison-Wesley, 1990.

- [22] V. Adler and E. G. Friedman, "Repeater design to reduce delay and power in resistive interconnect," in *Proc. IEEE Int. Symp. Circuits and Systems*, June 1997, pp. 2148–2151.

- [23] C. J. Alpert and A. Devgan, "Wire segmenting for improved buffer insertion," in *Proc. IEEE/ACM Design Automation Conf.*, June 1997, pp. 649–654.

- [24] S. Dhar and M. A. Franklin, "Optimum Buffer Circuits for Driving Long Uniform Lines," *IEEE J. Solid-State Circuits*, vol. 26, pp. 32–40, Jan. 1991.

- [25] Y. I. Ismail and E. G. Friedman, "Effects of inductance on the propagation delay and repeater insertion in VLSI circuits," *IEEE Trans. Very Large Scale Integration (VLSI) Syst.*, vol. 8, pp. 195–206, Apr. 2000.

- [26] Y. I. Ismail, E. G. Friedman, and J. L. Neves, "Repeater insertion in tree structured inductive interconnect," in *Proc. ACM/IEEE Int. Conf. Computer-Aided Design*, Nov. 1999, pp. 420–424.

- [27] H. J. M. Veendrick, "Short-circuit dissipation of static CMOS circuitry and its impact on the design of buffer circuits," *IEEE J. Solid-State Circuits*, vol. SC-19, pp. 468–473, Aug. 1984.

- [28] S. R. Vemuru and N. Scheinberg, "Short-circuit power dissipation estimation for CMOS logic gates," *IEEE Trans. Circuits Syst.*, vol. 41, pp. 762–765, Nov. 1994.

- [29] Y. I. Ismail, E. G. Friedman, and J. L. Neves, "Dynamic and short-circuit power of CMOS gates driving lossless transmission lines," *IEEE Trans. Circuits Syst. 1: Fundamental Theory and Applications*, vol. 46, no. 8, pp. 950–961, Aug. 1999.

- [30] E. G. Friedman, Clock Distribution Networks in VLSI Circuits and Systems. Piscataway, NJ: IEEE Press, 1995.

- [31] —, *High Performance Clock Distribution Networks*. Norwell, MA: Kluwer, 1997.

Yehea I. Ismail (M'00) was born in Giza, Egypt, on November 16, 1971. He received the B.Sc. degree in electronics and communications engineering w(ith distinction and honors) from the Department of Electronics and Communications, Cairo University, Cairo, Egypt, in 1993, the Masters degree in electronics (with distinction) from Cairo University, in 1996, and the Masters and Ph.D. degrees in electrical engineering from the University of Rochester, Rochester, NY, in 1998 and 2000, respectively.

As one of the top of his class, he was appointed as

a Teacher Assistant at the Department of Electrical and Computer Engineering, Cairo University, in August 1993. He is currently with Northwestern University, Evanston, IL, as an Assistant Professor. He was with IBM Cairo Scientific Center (CSC) from 1993 to 1996 on a part time basis and worked with IBM Microelectronics at East Fishkill, NY, the summers of 1997, 1998, and 1999. He has authored more than 35 technical papers and a book. His primary research interests include interconnect, noise, innovative circuit simulation, and related circuit level issues in high performance VLSI circuits.

Dr. Ismail is an Associate Editor for the IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, and an Associate Editor of the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS I, Fundamental Theory and Applications, and a guest editor for a Special Issue of the IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS on " "On-Chip Inductance in High-Speed Integrated Circuits"."

Eby G. Friedman (S'78–M'89–SM'90–F'00) received the B.S. degree from Lafayette College, Easton, PA, in 1979 and the M.S. and Ph.D. degrees from the University of California, Irvine, in 1981 and 1989, respectively, all in electrical engineering.

From 1979 to 1991, he was with Hughes Aircraft Company, rising to the position of Manager of the Signal Processing Design and Test Department, responsible for the design and test of high-performance digital and analog integrated circuits (ICs). He has been with the Department of Electrical and Computer

Engineering, University of Rochester, Rochester, NY, since 1991, where he is a Professor, the Director of the High-Performance VLSI/IC Design and Analysis Laboratory, and the Director of the Center for Electronic Imaging Systems. His current research and teaching interests are in high-performance synchronous digital and mixed-signal microelectronic design and analysis, with application to high-speed portable processors and low-power wireless communications. He is the author of more than 160 papers and book chapters and the author or editor of six books in the fields of high-speed and low-power CMOS design techniques, high-speed interconnect, and the theory and application of synchronous clock distribution networks.He is the Regional Editor of the *Journal of Circuits, Systems, and Computers* and a member of the editorial boards of *Analog Integrated Circuits and Signal Processing*, and the *Journal of VLSI Signal Processing*.

Dr. Friedman is the Editor-in-Chief of the IEEE TRANSACTION ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS and a member of the editorial board of IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS II: ANALOG AND DIGITAL SIGNAL PROCESSING. He is a member of the Circuits and Systems (CAS) Society Board of Governors and a member of the technical program committees of a number of a number of conferences. He was previously Chair of the IEEE TRANSACTIONS ON VLSI SYSTEMS Steering Committee, CAS liaison to the Solid-State Circuits Society, chair of the VLSI Systems and Applications CAS Technical Committee, Chair of the Electron Devices Chapter of the IEEE Rochester Section, program or technical chair of several IEEE conferences, editor of several special issues in a variety of journals, and a recipient of the Howard Hughes Masters and Doctoral Fellowships, an IBM University Research Award, an Outstanding IEEE Chapter Chairman Award, and a University of Rochester College of Engineering Teaching Excellence Award. He is a Senior Fulbright Fellow. Jose L. Neves, photograph and biography not available at the time of publication.