**INFORMATION TO USERS**

This manuscript has been reproduced from the microfilm master. UMI

films the text directly from the original or copy submitted. Thus, some

thesis and dissertation copies are in typewriter face, while others may be

from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the

copy submitted. Broken or indistinct print, colored or poor quality

illustrations and photographs, print bleedthrough, substandard margins,

and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete

manuscript and there are missing pages, these will be noted. Also, if

unauthorized copyright material had to be removed, a note will indicate

the deletion.

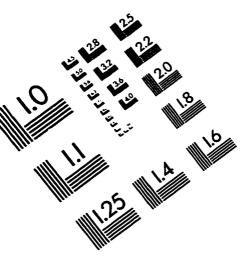

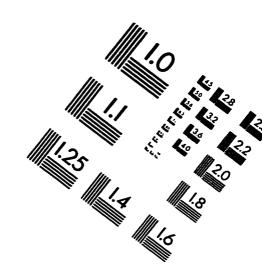

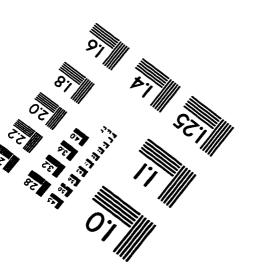

Oversize materials (e.g., maps, drawings, charts) are reproduced by

sectioning the original, beginning at the upper left-hand corner and

continuing from left to right in equal sections with small overlaps. Each

original is also photographed in one exposure and is included in reduced

form at the back of the book.

Photographs included in the original manuscript have been reproduced

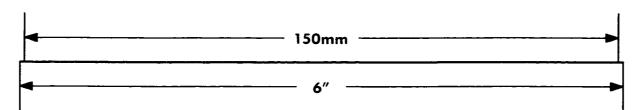

xerographically in this copy. Higher quality 6" x 9" black and white

photographic prints are available for any photographs or illustrations

appearing in this copy for an additional charge. Contact UMI directly to

order.

UMI

A Bell & Howell Information Company 300 North Zeeb Road, Ann Arbor MI 48106-1346 USA 313/761-4700 800/521-0600

#### Repeater Insertion for Driving Resistive Interconnect in CMOS VLSI Circuits

by

#### Victor Adler

Submitted in Partial Fulfillment

of the

Requirements for the Degree

Doctor of Philosophy

Supervised by Professor Eby G. Friedman

Department of Electrical and Computer Engineering

The College

School of Engineering and Applied Sciences

University of Rochester Rochester, New York 1998 UMI Number: 9916575

UMI Microform 9916575 Copyright 1999, by UMI Company. All rights reserved.

This microform edition is protected against unauthorized copying under Title 17, United States Code.

UMI 300 North Zeeb Road Ann Arbor, MI 48103

# Dedication

This work is dedicated to my parents, Carolyn and Eric, and my sister, Sara.

### Curriculum Vitae

The author was born in Burlington, Vermont on February 5, 1970. He attended Duke University, Durham, North Carolina from 1988 to 1992 and graduated cum laude with a Bachelor of Science degree in Electrical Engineering and a Bachelor of Arts in Computer Science in 1992. He received the I.B.M. T. J. Watson Memorial Scholarship from 1988 through 1992. From 1988 to 1992, he worked preprofessionally at IBM Microelectronics, Burlington, Vermont. He came to the University of Rochester in the fall of 1992 and began graduate studies in Electrical Engineering. In 1993, he received his Master of Science degree. In 1997 he performed research with Intel Corporation, Santa Clara, California, and in 1998 with Ultima Interconnect Technologies, Sunnyvale, California. He pursued research in very large scale high performance integrated circuits under the direction of Professor Eby G. Friedman from 1994 to 1998 in the areas of superconductive design methodologies and repeater insertion in CMOS integrated circuits.

## Acknowledgments

The time that I have spent at the University of Rochester has enriched my life greatly. My thanks and acknowledgments to those who have made my stay here educational, challenging, and fun.

First, my greatest thanks to my advisor, Professor Eby G. Friedman. He has guided my research and academic and personal growth with the care that few students are fortunate enough to receive. Beyond his knowledge and ideas about integrated circuit design, he has been the positive support required to complete a PhD. An excellent foil for my pessimism, I am grateful to have had the opportunity to work with him.

I thank Mark Bocko for service on my committee and working with me on my superconductive research. My thanks to David Albonesi for serving on my committee and taking his time out to talk to me about microprocessors and work related to my research. I would also like to thank Adam Frank for service on my committee.

To those who filled everyday of my graduate school career with help, challenge, and distraction in every area, I thank my previous and current officemates: Brian Cherkauer, Jose Neves, Tolga Soyata, Ivan Kourtev, Radu Secareanu, Yehea Ismail, and Tianwen (Kevin) Tang. I also thank my water polo teammates throughout the years for keeping me physically fit.

Finally, I would like to thank my family for their support throughout my life.

I have been able to accomplish what I have because of them.

This work was supported in part by the Army Research Office through Grant # DAAH04-MIP-9423886.

#### Abstract

The progress of CMOS integrated circuit technology has permitted transistors to operate at extremely high speeds. Simultaneously, improvements in technology have enlarged circuit die sizes and the number of transistors, thus increasing the length (hence the delay) of on-chip interconnections. This decrease in transistor delay and increase in interconnect delay has shifted the performance bottleneck of CMOS integrated circuits from transistors to interconnect. The circuit level design strategy of repeater insertion to reduce the delay of on-chip interconnect and improve the performance of leading edge CMOS technologies is described in this dissertation. An inverter-interconnect model and optimization algorithms are presented to provide a repeater insertion methodology to reduce interconnect delay.

As the length of the interconnections increases, the resistance and capacitance of that interconnect increases linearly with length. Thus the RC delay increases quadratically, severely degrading circuit performance. This RC delay can be reduced through the insertion of repeaters along an interconnect line. A CMOS inverter is used as a repeater to reduce this quadratic increase of RC delay.

A repeater-interconnect model based on the short-channel  $\alpha$ -power law transistor model is developed to describe repeater insertion in a resistive interconnect line. A closed form expression describing the number and size of repeaters to in-

sert along an interconnect line is presented. The analytical expression is generally within 10% of SPICE.

The repeater insertion model for RC lines is expanded for the more general purpose of repeater insertion in RC tree structures. Local and global optimization algorithms are presented to insert repeaters into RC trees. Applications of the repeater insertion methodologies can be used to either minimize average delay or achieve a target delay. Repeater insertion methods reduce delay over typical cascaded buffers by 25% to 60% and are accurate to within 10% of SPICE. Expressions to analytically determine dynamic and short-circuit power dissipation of repeaters in RC trees are also presented. Thus, an integrated methodology for repeater insertion composed of circuit models, insertion algorithms, and demonstration examples is presented for application to high performance VLSI circuits.

# Contents

| D  | edica | tion                                               | ii  |

|----|-------|----------------------------------------------------|-----|

| Cı | urric | ulum Vitae                                         | iii |

| A  | cknov | wledgments                                         | iv  |

| A۱ | bstra | et                                                 | vi  |

| Li | st of | Tables                                             | x   |

| Li | st of | Figures                                            | xii |

| 1  | Intr  | roduction                                          | 1   |

| 2  | Mo    | dels of Transistors and Interconnect               | 8   |

|    | 2.1   | High Level Repeater Models                         | 9   |

|    | 2.2   | Interconnect Models                                | 10  |

|    | 2.3   | CMOS Transistor I-V Models                         | 15  |

| 3  | Sho   | rt-Channel Model for a Repeater Driving an RC Load | 19  |

|    | 3.1   | Transient Analysis of an RC Loaded CMOS Inverter   | 19  |

|    |       | 3.1.1 Derivation of Analytical Expressions         | 20  |

|    |       | 3.1.2 Analytical Delay Expressions                 | 24  |

|    |       | 3.1.3 Analysis of Delay Expressions                | 24  |

|    | 3.2   | Power Estimation of a CMOS Inverter                | 26  |

|    |       | 3.2.1 Dynamic Power                                | 27  |

|    |       | 3.2.2 Short-Circuit Power                          | 27  |

|    |       | 3.2.3 Resistive Power Dissipation                  | 33  |

|    | 3.3   | Determining the Parameters $I_{do}$ and $V_{do}$   | 35  |

|    | 3 /   | Conclusions                                        | 36  |

| 4            | -     | peater Design for Optimal Speed and        |                          | 37  |

|--------------|-------|--------------------------------------------|--------------------------|-----|

|              | 4.1   | Expressions for an Inverter Driving an R   |                          | 39  |

|              | 4.2   | Delay of a Repeater Chain Driving an Re    |                          | 41  |

|              | 4.3   | Analytical Delay Model Versus SPICE .      |                          | 46  |

|              | 4.4   | Uniform Repeaters Versus Tapered Buffe     | rs and Tapered-Buffer    |     |

|              |       | Repeaters                                  |                          | 50  |

|              | 4.5   | Power Dissipation in Repeater Chains       |                          | 53  |

|              | 4.6   | Conclusions                                |                          | 56  |

| 5            | Rep   | peater Insertion in RC Trees to Minir      | nize Delay               | 57  |

|              | 5.1   | Local Branch Repeater Insertion Algorit    | hm                       | 58  |

|              | 5.2   | Global Tree Repeater Insertion Algorith    | m                        | 63  |

|              | 5.3   | Effectiveness, Accuracy, and Application   | ns of Repeater Insertion |     |

|              |       | Methodologies                              |                          | 68  |

|              |       | 5.3.1 Applications                         |                          | 68  |

|              |       | 5.3.2 Accuracy and Effectiveness           |                          | 70  |

|              |       | 5.3.3 Comparison of Global Optimization    | on to Exhaustive Search. | 72  |

|              | 5.4   | Power Dissipation of Repeaters in RC Tr    |                          | 73  |

|              | 5.5   | Conclusions                                |                          | 75  |

| 6            | Cor   | nclusions                                  |                          | 80  |

| 7            | Fut   | ure Research                               |                          | 83  |

|              | 7.1   | Model Improvements                         |                          | 83  |

|              |       | 7.1.1 Modeling a Repeater Driving an       | RC Load with a Slow      |     |

|              |       | Ramp Input Signal                          |                          | 84  |

|              |       | 7.1.2 Consideration of Saturation Region   | on                       | 84  |

|              |       | 7.1.3 Improved RC Model                    |                          | 86  |

|              | 7.2   | Optimization Algorithms                    |                          | 87  |

|              |       | 7.2.1 Simulated Annealing                  |                          | 87  |

|              |       | 7.2.2 Dominant Frontier                    |                          | 88  |

|              | 7.3   | Calculation of the Overall Cost of Inserti |                          | 88  |

|              | 7.4   | Development of a CAD Tool                  | <del></del>              | 88  |

|              |       | 7.4.1 Simultaneous Wire Sizing             |                          | 89  |

|              |       | 7.4.2 Including Placement Information      |                          | 89  |

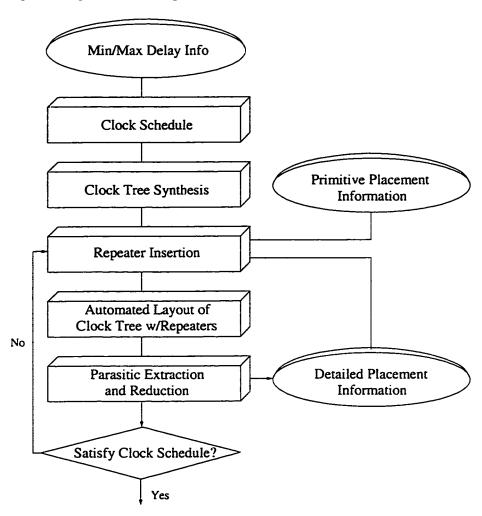

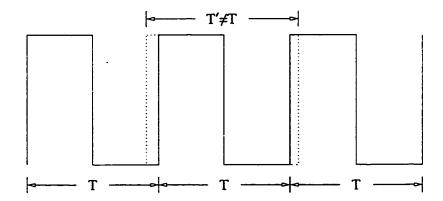

|              |       | 7.4.3 Clock Signal Variations              |                          | 91  |

|              | 7.5   | Conclusions                                |                          | 94  |

| R            | blice | graphy                                     |                          | 95  |

|              |       |                                            |                          |     |

| $\mathbf{A}$ | ppen  | idix Publications                          |                          | 105 |

# List of Tables

| 3.1 | Propagation delay $t_{PD}$ and transition time $t_t$ of a minimum-sized inverter driving an $RC$ load (0.8 $\mu$ m CMOS technology)                                                                                                                                                                               | 25 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Estimate of short-circuit power dissipated by a CMOS inverter (0.8 $\mu$ m CMOS technology)                                                                                                                                                                                                                       | 31 |

| 3.3 | The resistive power dissipated by a CMOS inverter driving an $RC$ load (0.8 $\mu$ m CMOS technology)                                                                                                                                                                                                              | 34 |

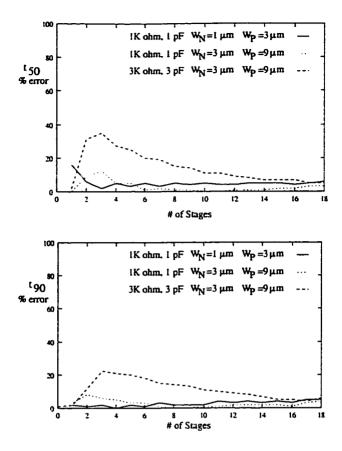

| 4.1 | Per cent error between analytical total delay model (both 50% and 90% output delay) versus SPICE for a given number of repeater stages, a repeater size of ( $W_N=1~\mu\mathrm{m},~W_P=3~\mu\mathrm{m}$ ), and an interconnect load of $R=1~\mathrm{K}\Omega$ and $C=1~\mathrm{pF}$ . (0.8 $\mu\mathrm{m}$ CMOS   |    |

| 4.0 | technology)                                                                                                                                                                                                                                                                                                       | 48 |

| 4.2 | Per cent error between analytical total delay model (both 50% and 90% output delay) versus SPICE for a given number of repeater stages, a repeater size of $(W_N = 3 \mu \text{m}, W_P = 9 \mu \text{m})$ , and an interconnect load of $R = 1 \text{ K}\Omega$ and $C = 1 \text{ pF}$ . (0.8 $\mu \text{m}$ CMOS |    |

|     | technology)                                                                                                                                                                                                                                                                                                       | 49 |

| 4.3 | Per cent error between analytical total delay model (both 50% and 90% output delay) versus SPICE for a given number of repeater stages, a repeater size of $(W_N = 3 \mu m, W_P = 9 \mu m)$ , and an                                                                                                              |    |

|     | interconnect load of $R=3$ K $\Omega$ and $C=3$ pF. (0.8 $\mu$ m CMOS technology)                                                                                                                                                                                                                                 | 50 |

| 4.4 | The 90% output time for optimally sized uniform repeaters, tapered-                                                                                                                                                                                                                                               |    |

|     | buffer repeaters, and tapered buffers for various loads as compared                                                                                                                                                                                                                                               | 52 |

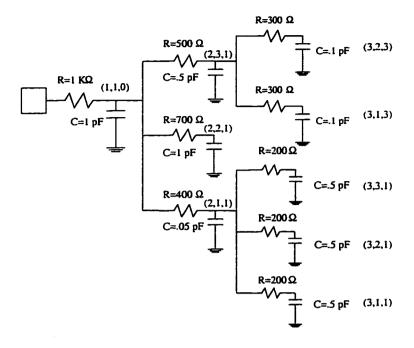

| 5.1 | The size and number of repeaters as determined by the local op-      |    |

|-----|----------------------------------------------------------------------|----|

|     | timization algorithm for three different RC tree topologies. (The    |    |

|     | propagation delay is in nanoseconds, # is the number of repeaters    |    |

|     | in a branch, size is the geometric width of the N-channel device     |    |

|     | of the uniform repeater for that branch, and the P-channel to N-     |    |

|     | channel ratio is 3:1.)                                               | 77 |

| 5.2 | The size and number of repeaters as determined by the global op-     |    |

|     | timization (downhill simplex and simulated annealing) algorithms     |    |

|     | for three different RC tree topologies. (The propagation delay is in |    |

|     | nanoseconds, # is the number of repeaters in a branch, size is the   |    |

|     | geometric width of the N-channel device of the uniform repeater      |    |

|     | for that branch, and the P-channel to N-channel ratio is 3:1.)       | 78 |

| 5.3 |                                                                      |    |

|     | timization algorithm to meet a terminal branch target delay of 2.0   |    |

|     | ns for the given RC tree topologies. (The propagation delay is in    |    |

|     | nanoseconds, # is the number of repeaters in a branch, size is the   |    |

|     | geometric width of the N-channel device of the uniform repeater      |    |

|     | for that branch, and the P-channel to N-channel ratio is 3:1.)       | 79 |

| 5.4 | Repeater insertion as determined by the downhill simplex method      |    |

|     | and an exhaustive search for the RC tree shown in Figure 5.10.       | 79 |

# List of Figures

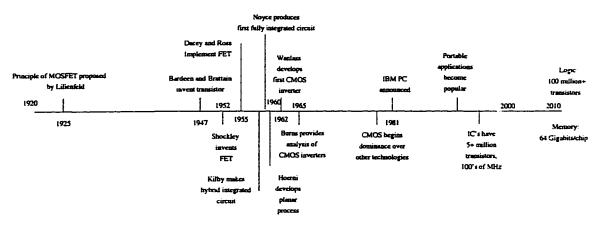

| 1.1 | A timeline of some of the major events in integrated circuit development from 1920 to 2010                                                 | 2  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------|----|

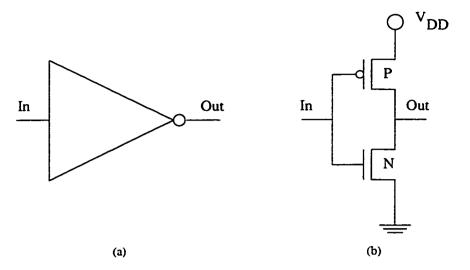

| 1.2 | An inverter. (a) The logical symbol for an inverter. (b) The equivalent CMOS transistor diagram.                                           | 5  |

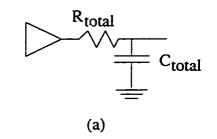

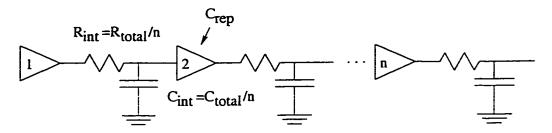

| 2.1 | n equal sized CMOS inverting repeaters driving an $RC$ load                                                                                | 10 |

| 2.2 | A schematic example of RC interconnect lines within an integrated circuit                                                                  | 12 |

| 2.3 | Different models to describe $RC$ interconnect: (a) the distributed model representation of an $RC$ load, (b) lumped load model, (c) $\Pi$ | 14 |

| 2.4 | model (d) T model (e) $\Pi$ -2 model (f) T-2 model (g) $\Pi$ -3 model Coupling capacitance between adjacent interconnect lines             | 15 |

| 2.5 | The characteristic current-voltage transfer curves of an enhance-                                                                          |    |

|     | ment N-channel MOSFET                                                                                                                      | 16 |

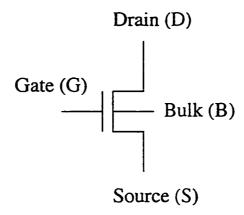

| 2.6 | A basic MOSFET with four terminals, gate, drain, source, and bulk (substrate)                                                              | 17 |

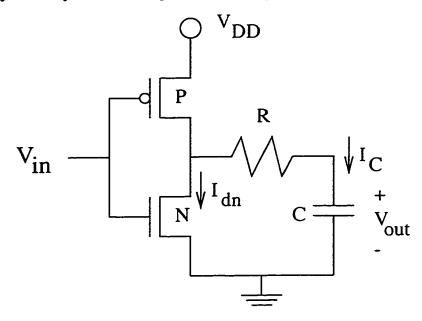

| 3.1 | A CMOS inverter driving a large RC load representative of a long interconnect                                                              | 20 |

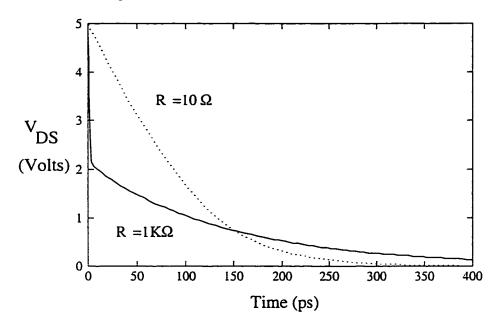

| 3.2 | Comparison of $V_{DS}$ for a CMOS inverter driving different load resistances $R$ and a constant load capacitance ( $C = 100 \text{ fF}$ ) | 21 |

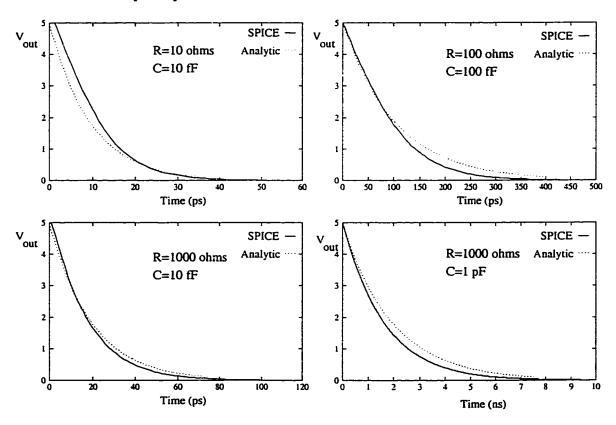

| 3.3 | Output response of a CMOS inverter driving an RC load                                                                                      | 23 |

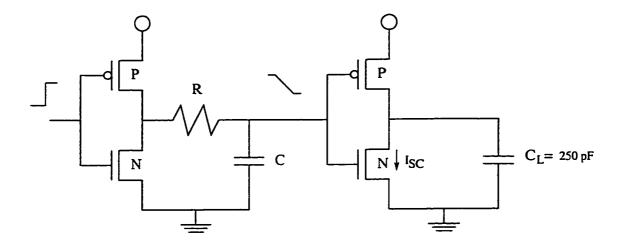

| 3.4 | Non-step input driving CMOS inverter stage creates short-circuit power                                                                     | 28 |

| 3.5 | Graphical estimation of short-circuit current (0.8 $\mu$ m CMOS technology)                                                                | 29 |

| 3.6 | Ratio of short-circuit power to total transient power versus inter-<br>connect resistance for varying interconnect capacitance             | 32 |

| 4.1 | A CMOS inverter driving an RC load                                                                                                         | 40 |

| 4.2 | n equal sized CMOS inverting repeaters driving an $RC$ load                                                                                | 42 |

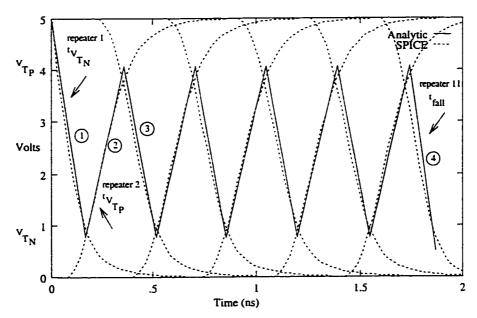

| 4.3        | The analytic and SPICE derived output waveforms of an 11-stage repeater chain driving an evenly distributed $RC$ load of 1 K $\Omega$ and                                                                                                                                                                                    | 42       |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

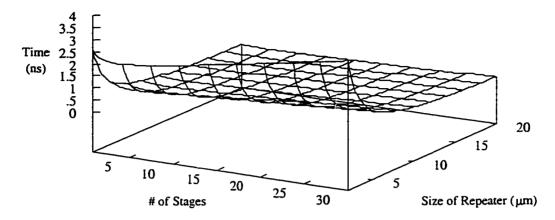

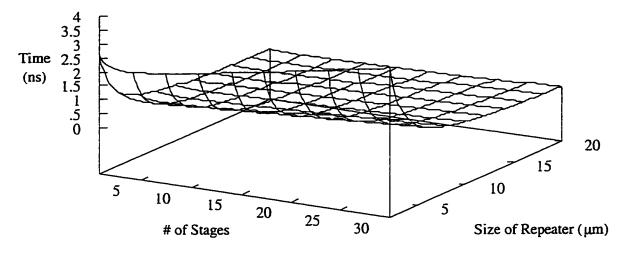

| 4.4        | The 90% output delay time for an interconnect line as a function                                                                                                                                                                                                                                                             | 43       |

|            | of the number of repeaters and repeater width. $(R = 1 \text{ K}\Omega, C = 1 \text{ pF}, 0.8 \ \mu\text{m CMOS technology})$                                                                                                                                                                                                | 46       |

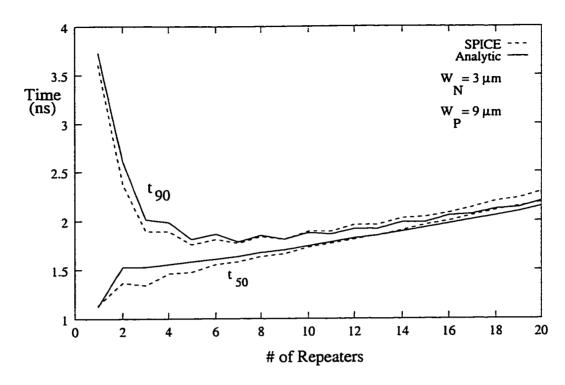

| 4.5        | The analytical and simulated 50% and 90% delay times for a 1 K $\Omega$ and 1 pF load evenly distributed across a number of uniformly sized repeaters.                                                                                                                                                                       | 47       |

| 4.6        | The per cent error of the analytical value of the 50% and 90% output delays versus SPICE for various loads and repeater sizes.                                                                                                                                                                                               | 51       |

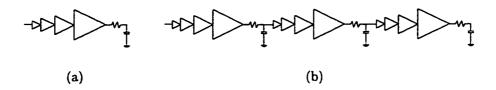

| 4.7        | Two methods of driving interconnections with tapered buffers: (a) A single tapered buffer (b) A three stage tapered-buffer repeater system. The first stage is a minimum sized repeater. The tapering factor is e                                                                                                            | 52       |

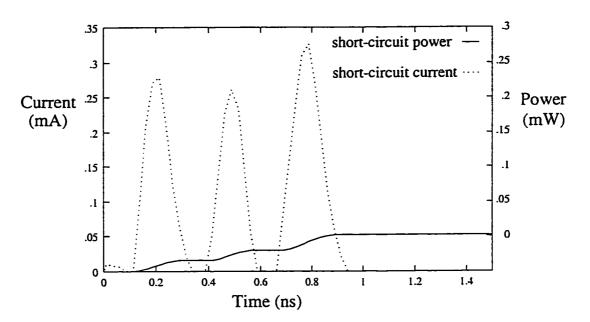

| 4.8        | Short-circuit current and power dissipated in a four-stage repeater with $W_N = 5 \mu \text{m}$ and $W_P = 15 \mu \text{m}$ , $f = 10 \text{ MHz}$                                                                                                                                                                           | 54       |

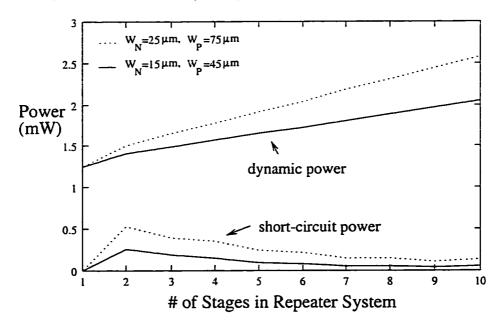

| 4.9        | The short-circuit and dynamic power dissipation versus the number of stages in a repeater system. Note the small increase in short-circuit power from nine to ten stages due to the increase in peak current with negligible improvement in transition time                                                                  | 55       |

| 5.1        | An example of an $RC$ tree. Ordered triplets $(i, j, k)$ are used to identify specific branches (note that the downstream nodes are to the right of the upstream nodes)                                                                                                                                                      | 59       |

| 5.2        | n equal sized CMOS inverting repeaters driving a branch in an $RC$                                                                                                                                                                                                                                                           | 59       |

| 5.3        | The total delay for a branch as a function of the number of repeaters and repeater sizes. 0.8 $\mu$ m CMOS technology, $C_{rep} = 0$ , $R = 1 \text{ K}\Omega$ ,                                                                                                                                                             |          |

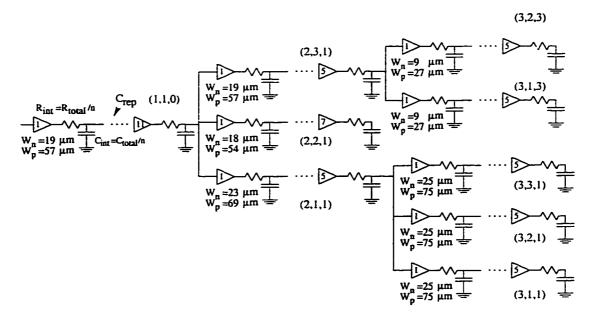

| 5.4        | and $C = 1$ pF                                                                                                                                                                                                                                                                                                               | 61<br>62 |

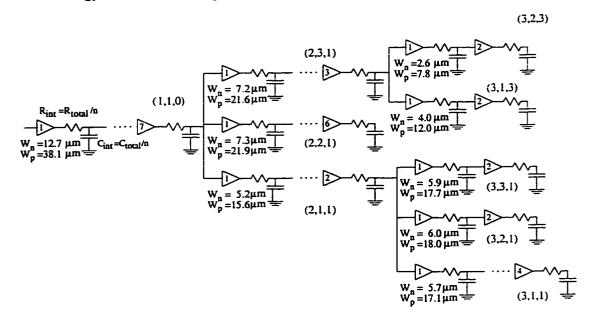

| 5.5        | The RC tree shown in Figure 5.1 synthesized by the local branch repeater insertion system. The transistor widths are shown below the first repeater of each branch, and the number of repeaters per                                                                                                                          |          |

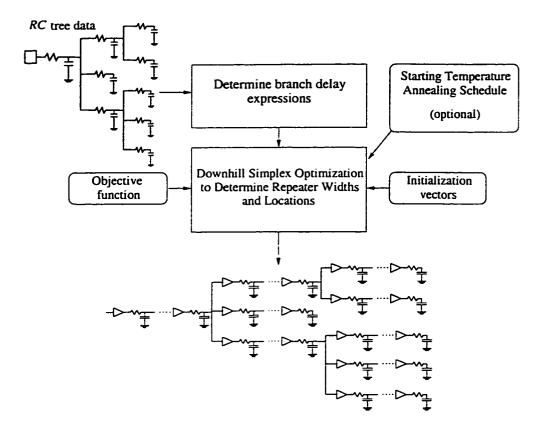

| 5.6<br>5.7 | branch is shown inside the last repeater of each branch A methodology for globally optimal repeater insertion The <i>RC</i> tree shown in Figure 5.1 synthesized by the global repeater insertion system. The transistor widths are shown below the first repeater of each branch, and the number of repeaters per branch is | 63<br>64 |

|            | shown inside the last repeater of each branch                                                                                                                                                                                                                                                                                | 66       |

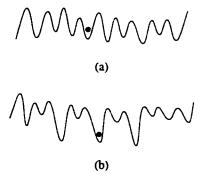

| 5.8  | Two possible solution spaces for a non-convex function. (a) An objective function with nearly equivalent minima. (b) Several outstanding minima among many ordinary minima                                   | 68 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

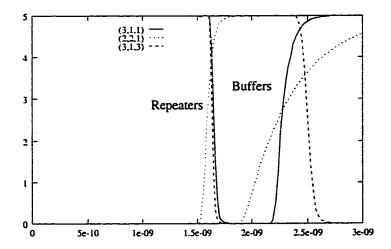

| 5.9  | The delay from the input of the RC tree to specific leaves of the tree based on the repeater insertion system as compared to applying optimally tapered buffers. Triplets indicate the leaf nodes as labeled |    |

|      | in Figure 5.5                                                                                                                                                                                                | 71 |

| 5.10 | A section of the RC tree shown in Figure 5.1 used to compare the                                                                                                                                             |    |

|      | global optimization algorithms versus the exhaustive search                                                                                                                                                  | 74 |

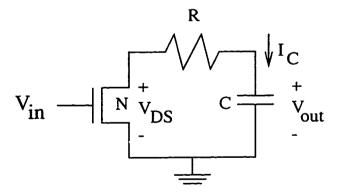

| 7.1  | The N-channel transistor of a CMOS inverter driving a large RC                                                                                                                                               |    |

|      | load representative of a long interconnect. $V_{DS}$ is the output voltage                                                                                                                                   |    |

|      | of the operating transistor of a repeater.                                                                                                                                                                   | 85 |

| 7.2  | The clock distribution network design flow of an integrated circuit                                                                                                                                          |    |

|      | modified to include repeater insertion.                                                                                                                                                                      | 90 |

| 7.3  | A variation in the period of the clock signal T is clock jitter                                                                                                                                              | 91 |

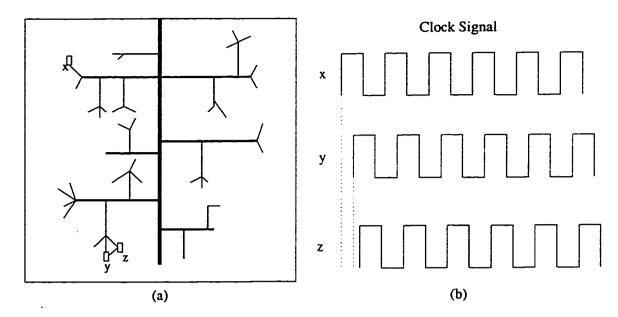

| 7.4  | Clock signal distribution in integrated circuits: (a) Schematic of                                                                                                                                           |    |

|      | the clock distribution network with three clocked elements x, y, z                                                                                                                                           |    |

|      | (b) The variation in clock arrival times between sequentially non-                                                                                                                                           |    |

|      | adjacent registers (x and y) and (x and z) is global clock skew,                                                                                                                                             |    |

|      | between sequentially adjacent registers (y and z) is local clock skew.                                                                                                                                       | 93 |

# Chapter 1

#### Introduction

The miniaturization of transistor technology has so far been able to keep up with the desire for increased speed of operation in microelectronic circuits. Because the die size of integrated circuits has become large as compared to the size of the transistor, the speed roadblock has shifted from the speed of the transistor to the delay through the connections among the transistors [1–3].

In 1947 when Bardeen, Brattain, and Shockley first discovered the transistor [4], not only the world of electronics changed, but the impetus for rapid world change was made. William Shockley soon invented the two types of transistors that would become widely used, the bipolar junction transistor (BJT) and the idea for the field-effect transistor (FET) in 1952 [5–7]. Shockley's concept for the FET was implemented by Dacey and Ross in 1955 [8].

The ubiquitous use of FET technology was delayed for several years due to technological processing roadblocks. By the end of the 1950's, a good process for producing FETs was developed by Atalla, Tannenbaum, and Scheibner [9], and later modified by Hoerni in 1960 [10]. This mature process allowed the mass production of silicon FETs to proceed [11].

Of the few initial scientists and engineers who pioneered the development of

Valley in Northern California. It was there at the end of the 50's, that Noyce of Fairchild Semiconductor produced the first fully integrated monolithic circuit. It should be noted, for historical purposes, that Noyce's claim to be the first to invent the integrated circuit did not go unchallenged. Jack Kilby of Texas Instruments produced a hybrid integrated circuit in which the interconnections were made of gold wire rather than part of a planar process [11, 12]. Although these first circuits were initially made with BJT's, monolithic circuits using MOSFET (Metal-Oxide Semiconductor FETs) were soon produced [11].

Figure 1.1: A timeline of some of the major events in integrated circuit development from 1920 to 2010

In 1962, Frank Wanlass developed the first Complementary MOS (CMOS) inverter. The CMOS inverter has become the ubiquitous circuit technology used today, and is fundamental to the research described in this dissertation. By the end of 1964, J. R. Burns provided further analysis of CMOS technology [13]. The advantages of CMOS were shown to be significantly lower power, ease of design, equal rise and fall times, and the ability to produce pull-up devices without having to fabricate area consuming resistors. A disadvantage of CMOS is that more devices are needed to implement a function as compared to NMOS technology,

and thus more area is required. This aspect was a major disadvantage since physical area on a chip was at a high premium at the time and hindered the development of CMOS until the late 70's when the power consumption of the IC's began to become a significant problem, particularly since the level of integration was approaching many tens of thousands of transistors.

Today CMOS is the predominate technology in digital integrated circuits. Integrated circuits can contain tens of millions of transistors. These devices have become small enough that circuit speed is no longer dictated by the size of the transistors on the chip, but rather by the long interconnections carrying the data and control (e.g., clock) signals from one section of a chip to another [3]. As these signals propagate through the interconnect, the waveform shape degrades. These long interconnects therefore greatly affect both the speed and power of the microelectronic circuits.

The microelectronics industry has demonstrated tremendous gains since the early 60's, but in order to continue the advancement of both microelectronics and related application areas, such as computers, integrated circuits must not only operate fast, but also consume as little power as possible. One strategy to improve both of these criteria can be accomplished by examining the methods by which both data and clock signals are distributed. With the continuously increasing size of integrated circuits, the distance that these signals travel has quickly become a limiting factor for both speed and power. Long wires not only create large capacitive loads but create a non-negligible resistive component, degrading the signal waveform properties.

Although the effects of a capacitive load on CMOS circuits have been studied extensively, the importance of resistance is still being fully recognized due to the

increasing size of integrated circuits and the smaller physical size of the transistor dimensions. These large resistances can occur in the long metal wires in large integrated circuits or in the shorter polysilicon connections. There are additional detrimental effects of large interconnect resistance, resulting in increased delay and power dissipation.

With respect to increased delay, with a linear increase in interconnect length, both the interconnect capacitance (C) and interconnect resistance (R) increase linearly, making the RC delay increase quadratically. Although the RC delay is not a precise measure of the time necessary for a signal to propagate through a wire, the total RC delay of a section of a line may be useful as a figure of merit. In order to increase the operating speed of a integrated circuit, it is necessary to reduce the RC delay.

In addition to increased signal propagation, increased power dissipation is another effect of large interconnect impedance. In addition to the inevitable dynamic switching power that may be dissipated, there is a passive power component dissipated by the resistive interconnect. This resistive power dissipation has gone unstudied, and, depending on the size of the interconnect resistance, can make a significant contribution to the total power dissipated within an IC.

Another contribution to the total power dissipation that has come under recent scrutiny is the power attributed to short-circuit (or cross-over) current [14]. Due to the slower, degraded waveforms (from long interconnections), the N-channel and P-channel transistors in the CMOS circuits switch on and off more slowly, forming a direct DC path from power to ground. This short-circuit power component can be a sizable portion of the total power dissipated by a CMOS-based IC.

The total RC delay of an interconnect line can be reduced drastically with

Figure 1.2: An inverter. (a) The logical symbol for an inverter. (b) The equivalent CMOS transistor diagram.

the insertion of a signal amplifier known as a repeater. In CMOS technology, the simplest form of a repeater is produced from a two transistor inverter. Its symbol is shown in Figure 1.2a and the CMOS equivalent circuit is shown in Figure 1.2b. That is, the multiplicative effect that resistance and capacitance has on RC delay can be reduced with the placement of inverters in appropriate locations along an RC interconnect line, thus increasing the speed of the signal propagation. Repeaters accomplish this effect by breaking up the interconnect line such that the resistive and capacitive components do not become excessively large. For example, assume a long interconnect has 5 units of resistance and 10 units of capacitance. The total RC delay would be 50 units. However, if five repeaters are inserted within this line to break the interconnect into five equal pieces, the RC delay would be  $1 \times 2 + 1 \times 2 + 1 \times 2 + 1 \times 2 = 10$  units. If the delay of the five repeaters is less than 40 units, then there is a speed benefit to inserting CMOS repeaters.

An additional benefit of increasing the signal speed due to the placement of

repeaters is reducing short-circuit power. With faster signal transition times, the time during which a DC path exists between the power supply and ground during which short-circuit current flow is decreased.

In order to achieve desired clock frequencies of 100's of MHz or even speeds greater than a GHz, the problem of resistive interconnect must be overcome. Furthermore, given these target clock frequencies, minimal power must be dissipated in portable applications to increase battery life as well as for heat removal purposes.

The topic of the dissertation is research in circuit techniques, specifically repeaters, to reduce the problem of resistive interconnect in high performance CMOS circuits. Some background on CMOS inverter models, interconnect models, inverters, and repeaters is presented in Chapter 2. The interconnect model used in the repeater insertion algorithm described in the following chapters is also explained.

In Chapter 3, a model for an inverter driving a lumped resistive capacitive load is introduced as the foundation for the repeater analysis and placement found in later chapters. The derivation of the analytical expression for a repeater driving RC interconnect is described and compared to SPICE simulations. Dynamic, short-circuit, and resistive power dissipation in interconnect are also investigated. In addition, the short-channel device parameters of the  $\alpha$ -power law are outlined.

Repeater models that consider optimal speed and power are presented in Chapter 4. The model presented in Chapter 3 is expanded to describe repeater insertion in RC lines. The effectiveness of uniform repeater insertion in RC lines is compared to tapered buffers and tapered buffer repeater insertion. The accuracy of the repeater model is compared to SPICE. Power dissipation in repeater chains is also examined.

A repeater insertion methodology for RC trees rather than lines to minimize (or target) delay and an analysis of the power dissipated in RC trees is described in Chapter 5. Both a local and a global repeater insertion method are described for the tree structure. Applications of both methods and power dissipation characteristics in RC trees are discussed.

Conclusions of the thesis are presented in Chapter 6. And, finally, future work that would further improve these research results is discussed in Chapter 7.

## Chapter 2

# Models of Transistors and Interconnect

In order to determine the optimal placement and size of the repeaters to be inserted in an interconnect line, a physical model must be developed and applied. Before proceeding to this model, it is instructive to examine earlier models. A repeater is essentially a digital amplifier. In CMOS technology, the output of a two transistor inverter with an input signal below some threshold  $V_{IL}$  (input low voltage) will be restored to the supply voltage  $V_{OH}$  (output high voltage). Likewise, if the input is above some threshold voltage  $V_{IH}$ , the output will be forced to ground.

The transistor and inverter models which permit the analysis of the operation of a CMOS repeater are reviewed in this chapter. Although many transistor and inverter models have been proposed in the literature [15–22], most of these models are sufficiently complex such that the analysis of a circuit more complex than a simple inverter is often intractable. Therefore attention is focused on applying those models that provide a high degree of both tractability and accuracy. These transistor and interconnect models are used together to analyze various repeater systems. The very simplest models used for repeater analysis will be presented

first to provide some motivation followed by more accurate models for interconnect and transistors.

A description of high level repeater models is presented in Section 2.1. Some models for interconnect are described in Section 2.2. Finally, two major transistor I-V equations are reviewed in Section 2.3.

#### 2.1 High Level Repeater Models

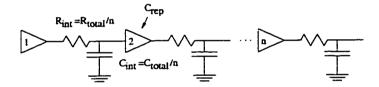

Before discussing interconnect models and transistor current-voltage (I-V) equations, it is useful to examine some higher level models. If the width of an interconnect line in an integrated circuit is constant, both the resistance and capacitance increase linearly with length  $(l_{int})$ ; therefore, delay is proportional to RC which quadratically increases with length as  $l_{int}^2$ . As previously discussed in Chapter 1, the insertion of repeaters can reduce the quadratic nature of the interconnect delay. A single inverter driving a large RC load  $(R_{total}, C_{total})$  is shown in Figure 2.1a. The same load broken up with n repeaters is shown in Figure 2.1b. A simple characterization of delay of an RC line with repeaters inserted along the line is

$$t_{total} = nt_{rep} + n\frac{t_{int}}{n^2} = nt_{rep} + \frac{t_{int}}{n} \qquad (2.1)$$

where  $t_{total}$  is the delay from the input of the first repeater to the output of the last repeater [3, 23].  $t_{rep}$  is the delay of each repeater and  $t_{int}$  is the total RC delay of the complete interconnect. n is the number of repeaters, where n has been placed both above and below the fraction of  $t_{int}$  to indicate that each of the n pieces of interconnect quadratically reduces the delay.

Equation (2.1) is differentiated and set equal to zero to determine a min/max

$$\begin{array}{c|c} R_{total}/n \\ \hline \\ \hline \\ C_{total}/n \end{array}$$

Figure 2.1: n equal sized CMOS inverting repeaters driving an RC load.

value of  $t_{total}$ . The optimal value for n is

$$n = \sqrt{\frac{t_{int}}{t_{rep}}} . {(2.2)}$$

This equation implies that the total delay through a long interconnection with repeaters is minimized when the delay of each repeater is equivalent to the delay of each section of interconnect. Frequently,  $t_{rep}$  is modeled as a resistance (the output resistance of the inverter) and capacitance (the gate capacitance of the inverter). This model may be acceptable for coarse timing information, but more precise knowledge is required for a more accurate placement of the repeaters.

#### 2.2 Interconnect Models

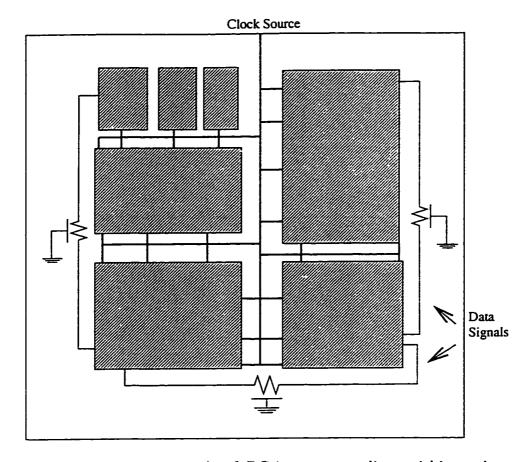

In integrated circuits, the term interconnect refers to the wire that connects various points within the chip die. An example of where RC interconnect occurs on a chip is shown in Figure 2.2. In this example, long resistive interconnect commonly occurs in the clock distribution network that synchronously drives each

block, and resistive interconnect also are common in the global data lines between blocks. In addition, there can be significant resistive interconnect within each block.

In a CMOS technology, different materials are used as wires depending on the type of interconnection. For instance, polysilicon can be used as an interconnection material. Polysilicon is the material used to define the gate electrode of a CMOS transistor and is characterized by a high resistance (approximately 40 ohms per square) and capacitance, so its use as a wire is typically limited. It is convenient to use polysilicon when connecting the gates of transistors with the same input because only a single wire is required. The same gate connection with metal requires much more area, thus the added area of using metal for a local connection often outweighs the reduced line impedance. Furthermore, situations arise where local metal wire can not be used due to the density of a circuit, thus polysilicon would be used as the interconnection material. These cases represent examples of where a high impedance interconnection might be used.

When long interconnections are required, such as global connections between two large functional blocks, some type of metal wire with low resistance and capacitance may be preferable. Polysilicon is typically avoided because the convenience of local connections described above does not exist, and the RC characteristics of polysilicon would significantly degrade the signal shape. Although metal has a low impedance (typically less than 0.1 ohms per square), the length of a inetal wire may still produce a large RC delay. In either case, whether the interconnect is intrablock or interblock wiring, resistive interconnect poses a problem.

There are several ways to model resistive interconnect. A wire could be modeled as a transmission line. The characteristics of a transmission line model are

Figure 2.2: A schematic example of RC interconnect lines within an integrated circuit.

described in [24, 25] and are appropriate when analyzing circuits operating at sufficiently high frequencies where the transition time of the signals is comparable to or less than the time of flight down a wire. A transmission line model is both highly complex and difficult to use in conjunction with a large-signal transistor I-V model, making intractable the development of closed form solutions of a repeater system. Furthermore, as is shown in [26], simpler interconnect models can provide sufficient accuracy while remaining useful at current operating frequencies of large integrated circuits (e.g., greater than 300 MHz). The point at which a resistive model will no longer be useful depends upon the geometry of the driven interconnect. Inductance will need to be considered in extremely long and wide

lines with low resistance. Thus, a hard limit on frequency at which a transmission line model is necessary can not be given but is well above 500 MHz.

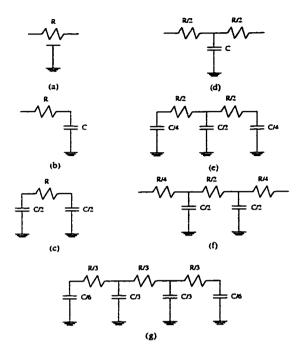

A discrete element model to describe the distributed nature of a resistive-capacitive interconnect load is presented in [26]. A small resistor-capacitor network can be used to analyze a distributed load with small error. The number and placement of the resistors and capacitors depends upon the ratio of the interconnect resistance and capacitance to the transistor output resistance and input capacitance, respectively. Some examples of RC networks used to model distributed RC loads are shown in Figure 2.3. The symbol for a distributed RC load (one with infinite sections) is shown in Figure 2.3a. A lumped RC load is shown in Figure 2.3b. RC models of increasing complexity and accuracy, approaching a distributed RC model, are shown in Figures 2.3c through 2.3g.

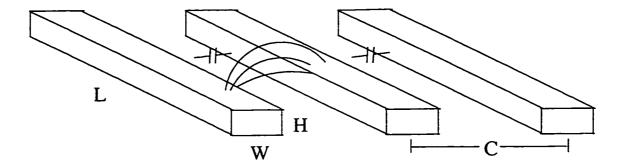

Another source of impedance in interconnect is coupling capacitance. Coupling capacitance occurs when two or more interconnect lines run adjacent to each other over some distance [27, 28] or are closely spaced with respect to each other [29]. A schematic description of coupling capacitance between adjacent lines is shown in Figure 2.4. The magnitude of the coupling capacitance or signal noise is determined by the following: the area of adjacency, hence the length of adjacency; the distance between the interconnect lines; and the direction of the adjacent signals. Inserting repeaters can drastically reduce the length of adjacency between two interconnect lines. Thus, decreased coupling capacitance is an added benefit of inserting repeaters. Although overcoming coupling capacitance is not a topic of research that is specifically discussed in this dissertation, this benefit of repeater insertion should be noted.

The analysis used in the following chapters further simplifies these intercon-

Figure 2.3: Different models to describe RC interconnect: (a) the distributed model representation of an RC load, (b) lumped load model, (c)  $\Pi$  model (d) T model (e)  $\Pi$ -2 model (f) T-2 model (g)  $\Pi$ -3 model

nect models. The interconnect is considered to be a lumped element, *i.e.*, a single resistor and capacitor. Although this model may create more error than a more complex model, it yields sufficiently accurate results as compared to similar models in SPICE [30]. A lumped load is generally a pessimistic approximation of a distributed load because in a lumped load, all of the interconnect resistance "sees" or is upstream to all of the interconnect capacitance. Practically, only the initial incremental portion of the interconnect,  $\Delta R$ , sees all of the downstream interconnect capacitance, with each successive  $\Delta R$  seeing less capacitance while moving down the interconnect line. For instance, in Figure 2.3g,  $\frac{1}{6}C$  is upstream to all of the resistance,  $\frac{1}{3}C$  is upstream of  $\frac{2}{3}R$ , and so on.

•

Figure 2.4: Coupling capacitance between adjacent interconnect lines.

#### 2.3 CMOS Transistor I-V Models

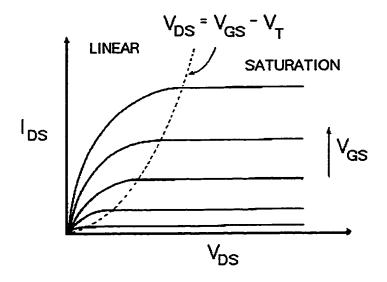

In order to more accurately model a repeater system, I-V equations that describe the operation of a transistor are required. In 1968, the Shichman-Hodges transistor I-V equations were published [31] which were based on Shockley's original I-V model [6]. Three regions of operation are described: 1) cutoff, 2) linear, and 3) saturation. The operation of a transistor in these three regions is presented here with reference to Figures 2.5 and 2.6. The analysis that follows is for an N-channel silicon MOSFET with the source node connected to ground.

When the input voltage at the gate  $V_{GS}$  is less than some threshold voltage  $V_T$ , the transistor is said to be cutoff, and no drain current can flow. That is, other than a very small leakage current, no current flows from the source to the drain, so  $I_{DS} \approx 0$ .

Once the gate voltage increases above  $V_T$ , the region in which the transistor operates is determined by the relative values of the drain-to-source voltage  $V_{DS}$  and the gate-to-source voltage  $V_{GS}$ . If  $V_{DS} < V_{GS} - V_T$ , the transistor operates in the linear region and the drain current is described by the expression,  $I_{DS} = K(V_{GS} - V_T)V_{DS} - \frac{V_{DS}^2}{2}$ . If  $V_{DS} > V_{GS} - V_T$ , the transistor operates in the saturation region, and  $I_{DS} = \frac{K}{2}(V_{GS} - V_T)^2$  [32]. Summarizing,

Figure 2.5: The characteristic current-voltage transfer curves of an enhancement N-channel MOSFET

$$I_{DS} = \begin{cases} 0 & (V_{GS} \le V_T & : \text{ cutoff region}) \\ K(V_{GS} - V_T)V_{DS} - \frac{V_{DS}^2}{2} & (V_{GS} > V_T, V_{DS} < V_{GS} - V_T & : \text{ linear region}) \\ \frac{K}{2}(V_{GS} - V_T)^2 & (V_{GS} > V_T, V_{DS} > V_{GS} - V_T & : \text{ saturation region}) \end{cases}$$

(2.3)

There are a number of inaccuracies in the Shichman-Hodges equations. Two important inaccuracies are these equations 1) only work well for long-channel FETs and 2) become intractable when analyzing RC loaded inverters if no simplifying assumptions are made.

Sakurai has developed I-V equations for describing the behavior of a short-channel CMOS transistor [33]. The Sakurai  $\alpha$ -power law model overcomes some of the problems associated with the Shichman-Hodges model. First, the  $\alpha$ -power law model takes into account the important short-channel effect of velocity saturation. When a short-channel MOSFET operates in the saturation region, the drain current is no longer proportional to the square of the gate-to-source voltage  $V_{GS}$  due to the effects of velocity saturation. Velocity saturation occurs because

Figure 2.6: A basic MOSFET with four terminals, gate, drain, source, and bulk (substrate).

the electric field of a short-channel transistor is sufficiently great such that the current carriers are unable to travel from the source to the drain due to collisions with the crystal lattice of the semiconductor. Therefore, an increase in the gate voltage only increases the number of carriers and not the velocity of the carriers, so the current no longer increases quadratically with the effective gate voltage  $V_{GS} - V_T$  [34]. Secondly, parasitic drain and source resistances within the transistor must be taken into consideration. Lastly, the  $\alpha$ -power law provides fairly simple expressions that can be used to analyze the behavior of nonlinear digital circuits. The I-V equations for the  $\alpha$ -power law are:

$$I_{DS} = \begin{cases} 0 & (V_{GS} \leq V_T : \text{cutoff region}) \\ (I'_{D0}/V'_{D0})V_{DS} & (V_{DS} < V'_{D0} : \text{linear region}) \\ I'_{D0} & (V_{DS} \geq V'_{D0} : \text{saturation region}) \end{cases}$$

(2.4)

where

$$I'_{D0} = I_{D0} \left( \frac{V_{GS} - V_T}{V_{DD} - V_T} \right)^{\alpha} \tag{2.5}$$

$$V'_{D0} = V_{D0} \left( \frac{V_{GS} - V_T}{V_{DD} - V_T} \right)^{\alpha/2} (2.6)$$

In the  $\alpha$ -power law model,  $I_{do}$  represents the drive current of the MOS device,  $V_{do}$  represents the drain-to-source voltage at which velocity saturation occurs, and  $\alpha$  models the process dependent degree to which velocity saturation affects the drain-to-source current.

With accurate and general transistor and interconnect models, a repeater model that describes CMOS devices driving long resistive interconnect is developed in Chapter 3. This repeater model is expanded to explore the speed and power advantages of inserting repeater chains in interconnect in the following chapters.

# Chapter 3

# Short-Channel Model for a Repeater Driving an RC Load

In this chapter a foundation for modeling an RC loaded repeater is presented. The development and analysis of an analytical expression describing a short-channel CMOS inverter driving a resistive interconnect is presented in Section 3.1. In Section 3.2, the power dissipated by this system is investigated. Short-circuit power is emphasized in this section since this power component has been given little attention until recently and can represent a significant contribution to the total power dissipation, important in today's portable applications. Finally, a procedure for determining the circuit parameter values used in the  $\alpha$ -power law I-V model is provided in Section 3.3.

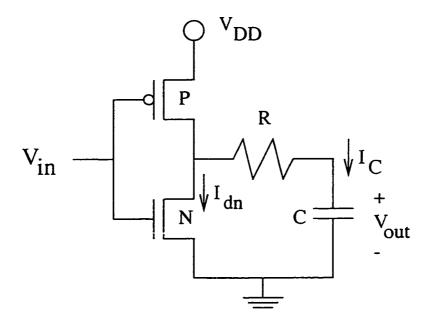

# 3.1 Transient Analysis of an RC Loaded CMOS Inverter

An analytical expression describing the behavior of an inverter driving a lumped RC load based on Sakurai's  $\alpha$ -power law model is presented in [33]. A diagram of this circuit is shown in Figure 3.1. In subsection 3.1.1, the device model is described and an analytical expression for the output voltage or a transition time to

reach  $V_{out}$  is derived. In subsection 3.1.2, several expressions that characterize the temporal properties of the circuit are presented. In subsection 3.1.3, some results of the analytical expressions are presented along with comparisons to SPICE.

Figure 3.1: A CMOS inverter driving a large RC load representative of a long interconnect

# 3.1.1 Derivation of Analytical Expressions

The  $\alpha$ -power law model [33] accurately describes the effects of short-channel behavior, such as velocity saturation, while providing a tractable equation. The linear region form of the  $\alpha$ -power model is used to characterize the I-V behavior of the ON transistor sourcing or sinking an RC load since a large portion of the circuit operation occurs within this region under the assumption of a step or fast ramp input signal. When the input to the inverter is a unit step or fast ramp,  $V_{out}$  is initially larger than  $V_{GS} - V_T$  for a shorter period of time than if the input to the inverter is a slow ramp. Therefore, the circuit operates in the linear region for a greater portion of the total transition time for a large RC load, particularly for

large load resistances. When the load resistance is large, a large IR voltage drop occurs across the load resistor once the capacitor begins to discharge, thus  $V_{DS}$  is nearly immediately less than  $V_{GS} - V_T$ , as shown in Figure 3.2. The N-channel device operates in the linear region once the step input goes high when driving large RC loads. Note however if the input waveform increases slowly or the load impedance is small, the inverter operates in the saturation region for a longer time before switching into the linear region. In addition, the  $\alpha$ -power law model is less accurate with slow input waveforms.

Figure 3.2: Comparison of  $V_{DS}$  for a CMOS inverter driving different load resistances R and a constant load capacitance (C = 100 fF)

Only the falling output (rising input) waveform is considered in this chapter. The following analysis, however, is equally applicable to a rising output (failing input) waveform. The lumped load is modeled as a resistor in series with a capacitor. The current through the output load capacitance is the same magnitude and opposite sign as the N-channel drain current (the P-channel current is ignored

under the assumption of a step or fast ramp input). The capacitive current is

$$i_C = C \frac{dV_{out}}{dt} = -i_d, (3.1)$$

where C is the output capacitance,  $V_{out}$  is the voltage across the capacitance C,  $i_C$  is the current discharged from the capacitor, and  $i_d$  is the drain current through the N-channel device.

The N-channel linear drain current is given by [33]

$$-C\frac{dV_{out}}{dt} = i_d = \frac{I_{do}}{V_{do}} \left(\frac{V_{GS} - V_T}{V_{DD} - V_T}\right)^{\alpha} V_{ds}, \quad \text{for } V_{GS} \ge V_T, V_{GS} - V_T \ge V_{DS}.$$

(3.2)

In the  $\alpha$ -power law model,  $I_{do}$  represents the drive current of the MOS device and is proportional to W/L,  $V_{do}$  represents the drain-to-source voltage at which velocity saturation occurs with  $V_{GS} = V_{DD}$  and is a process dependent constant, and  $\alpha$  models the process dependent degree to which velocity saturation affects the drain-to-source current.  $\alpha$  is within the range  $1 \le \alpha \le 2$  where  $\alpha = 1$  corresponds to a device operating strongly under velocity saturation, while  $\alpha = 2$  represents a device with negligible velocity saturation.  $V_{DD}$  is the supply voltage, and  $V_T$  is the MOS threshold voltage (where  $V_{TN}$  ( $V_{TP}$ ) is the N-channel (P-channel) threshold voltage). An empirical method to determine technology specific values for  $I_{do}$  and  $V_{do}$  is described in Section 3.3.

Assuming a unit step input is applied to the circuit shown in Figure 3.1,  $V_{out}$  can be derived from (3.2). The equation, rewritten in Laplace form, is

$$SCV_{out} + SU_{do}RCV_{out} + U_{do}V_{out} = CV_{out}(0) + U_{do}RCV_{out}(0), \qquad (3.3)$$

where  $\mho_{do} = \frac{I_{do}}{V_{do}}$  is the saturation conductance.

Equation (3.3) yields

$$V_{out}(t) = V_{out}(0)e^{\frac{-U_{do}}{U_{do}RC+C}t} (3.4)$$

Graphs of  $V_{out}(t)$  for a wide range of resistances and capacitances (within practical limits) driven by a minimum-sized inverter with balanced rise and fall times are shown in Figure 3.3. The analytical expression shown in (3.4) closely approximates SPICE for most of the region of operation for a wide range of load impedances from 10  $\Omega$  to 1000  $\Omega$  and from 10 fF to 1 pF. The maximum error of the output response derived from (3.4) as compared with SPICE (shown in Figure 3.3) is 25% for the specific case where the RC load is 10  $\Omega$  and 10 fF, approaching the unloaded case. As a means of comparison, the capacitance of metal interconnect in a 0.8  $\mu$ m technology is approximately .02 fF/ $\mu$ m<sup>2</sup> with polysilicon being about three times as capacitive. The resistance of metal in the same technology is approximately 0.08 ohms per square with polysilicon being about 10 ohms per square.

Figure 3.3: Output response of a CMOS inverter driving an RC load

### 3.1.2 Analytical Delay Expressions

From (3.4), the propagation delay of a CMOS inverter calculated at the 50% point  $t_{PD}$  is

$$t_{PD} = .693 \frac{C + \mathcal{V}_{do}RC}{\mathcal{V}_{do}} \tag{3.5}$$

The transition time of a CMOS inverter driving a lumped RC load calculated at the 90% point  $t_t$  is

$$t_t = 2.3 \frac{C + \mathcal{V}_{do}RC}{\mathcal{V}_{do}} \qquad . \tag{3.6}$$

Additional delay expressions that are used in section 3.2.2 for determining the short-circuit power are

$$t_{V_{TN}} = \ln\left(\frac{V_{TN}}{V_{DD}}\right) \frac{C + \mathcal{V}_{do}RC}{\mathcal{V}_{do}}$$

(3.7)

and

$$t_{V_{TP}} = \ln\left(\frac{V_{DD} + V_{TP}}{V_{DD}}\right) \frac{C + \mathcal{O}_{do}RC}{\mathcal{O}_{do}} \qquad (3.8)$$

These equations describe the time for the output voltage to change by a threshold voltage from either ground or  $V_{DD}$  for an N-channel or P-channel device, respectively. Note that  $V_{TP}$  is negative.

## 3.1.3 Analysis of Delay Expressions

The accuracy of the analytic model as compared with SPICE is tabulated in Table 3.1 for a wide range of output load resistances and capacitances. The interconnect resistance and capacitance are described in the first two columns of Table 3.1, respectively. The transition times determined by the analytical expression and by SPICE are shown in the third and fourth columns, respectively. The propagation delay times determined by the analytical expression and by SPICE

| verter driving an 1to load (0.5 \(\mu\)in Olylos technology) |             |          |        |          |        |         |          |  |

|--------------------------------------------------------------|-------------|----------|--------|----------|--------|---------|----------|--|

| Load                                                         | Load        | $t_t$    |        | $t_{PD}$ |        | % Error |          |  |

| Resistance                                                   | Capacitance | Analytic | SPICE  | Analytic | SPICE  | $t_t$   | $t_{PD}$ |  |

| 10 Ω                                                         | .01 pF      | 21 ps    | 22 ps  | 6.5 ps   | 8.7 ps | 4%      | 25%      |  |

| 10 Ω                                                         | .1 pF       | 215 ps   | 176 ps | 65 ps    | 70 ps  | 22%     | 7%       |  |

| 10 Ω                                                         | 1 pF        | 2 2 ns   | 1.7 ns | 649 ps   | 680 ps | 27%     | 4%       |  |

| 100 Ω                                                        | .01 pF      | 24 ps    | 22 ps  | 7.2 ps   | 8.8 ps | 6%      | 19%      |  |

| 100 Ω                                                        | .1 pF       | 235 ps   | 187 ps | 71 ps    | 73 ps  | 25%     | 2%       |  |

| 100 Ω                                                        | 1 pF        | 2.4 ns   | 1.9 ns | 712 ps   | 711 ps | 25%     | 0%       |  |

| 1000 Ω                                                       | .01 pF      | 44 ps    | 39 ps  | 13 ps    | 13 ps  | 13%     | 0%       |  |

| 1000 Ω                                                       | .1 pF       | 444 ps   | 365 ps | 133 ps   | 115 ps | 22%     | 16%      |  |

| 1000 Ω                                                       | 1 pF        | 4.4 ns   | 3.6 ns | 1.3ns    | 1.1 ns | 22%     | 18%      |  |

Table 3.1: Propagation delay  $t_{PD}$  and transition time  $t_t$  of a minimum-sized inverter driving an RC load (0.8  $\mu$ m CMOS technology)

are listed in columns five and six, respectively. The error of the analytical expressions versus SPICE for the transition time and propagation delay is shown in the final two columns. A 0.8  $\mu$ m CMOS technology is assumed. Note that the maximum error of the transition time  $t_t$  as compared with SPICE is 27%, and the maximum error of the propagation delay  $t_{PD}$  as compared with SPICE is 25%.

As noted above, (3.5) and (3.6) can be used to estimate the propagation delay and transition time of a CMOS inverter driving a resistive-capacitive interconnect line. Since the shape of the output waveform is now known, (3.7) and (3.8) can also be used with (3.6) to estimate the short-circuit power dissipation of a CMOS gate loading the high impedance interconnect line, as is described in Section 3.2.

The maximum error for the transition time for RC loads ranging from 10  $\Omega$  to 1000  $\Omega$  and 10 fF to 1 pF and for two different short-channel CMOS technologies (0.8  $\mu$ m and 1.2  $\mu$ m CMOS) is 27%. The maximum error for the propagation delay is 25% over the same ranges and technologies. As the capacitance increases to 1 pF, the error of the propagation delay generally decreases to less than 20%. A

similar decrease occurs for the transition time. Furthermore, both errors generally decrease with increasing load resistance.

The improved accuracy with increasing load resistance and capacitance is due to the RC load dominating the device parasitic impedances, specifically, the source and drain capacitance, thereby improving the accuracy of the transistor I-V model for large RC loads. These device parasitic impedances are not included in the I-V model described in (3.2) but are considered by SPICE. This behavior also explains why the accuracy improves as the geometric size of the transistors becomes smaller, making the parasitic device resistances and capacitances smaller. Thus, these expressions for the propagation delay and transition time of a CMOS inverter driving an RC load become more accurate for higher RC loads and more aggressive sub-micrometer technologies, the regime of greatest interest.

# 3.2 Power Estimation of a CMOS Inverter

Power consumption has become one of the premier issues in the design of VLSI circuits. There are two primary contributions to the total transient power dissipated by a CMOS inverter, dynamic power dissipation and short-circuit power dissipation [14, 35–39]. The short-circuit power is often neglected since the dynamic power is assumed to be dominant. As described below and in [14, 35–39], the magnitude of the short-circuit power is load dependent, and it is shown in this chapter that short-circuit power can be a significant portion of the total transient power dissipation.

Dynamic power is briefly discussed in subsection 3.2.1. In subsection 3.2.2, an analysis of short-circuit power is presented, and a closed-form model is proposed. In subsection 3.2.3, the power dissipated by the lossy resistive element of the

RC load is discussed and modeled. Finally, some concluding remarks pertaining specifically to estimating the power of an RC loaded CMOS inverter are offered.

### 3.2.1 Dynamic Power

Dynamic power is due to the energy required to charge and discharge a load capacitance C and is characterized by the familiar equation,  $CV^2f$ , where V is the source voltage and f is the switching frequency. The dynamic power is independent of the load resistance. For example, the dynamic power dissipation of a single CMOS inverter driving an RC load ranges from 35  $\mu$ W to 125  $\mu$ W for capacitive loads ranging from 0.3 pF to 1 pF and assuming a 5 volt power supply with the inverter switching at 10 MHz.

### 3.2.2 Short-Circuit Power

In this subsection an expression for modeling the short-circuit power in a CMOS inverter is presented. This expression is also analyzed and compared to SPICE. Also in this subsection, a comparison of the short-circuit power to the total transient power dissipation as a function of load resistance is presented.

### Analytic Expression of Short-Circuit Power

The logic stage following a large RC load may dissipate significant amounts of short-circuit power due to the degraded waveform originating from the CMOS inverter driving an RC load (see Figure 3.4). During the region where the input signal is transitioning between  $V_{TN}$  and  $V_{DD} + V_{TP}$ , a DC current path exists between  $V_{DD}$  and ground. The excess current dissipated during this region is called the short-circuit (or crossover) current [14]. Short-circuit current occurs

Figure 3.4: Non-step input driving CMOS inverter stage creates short-circuit power

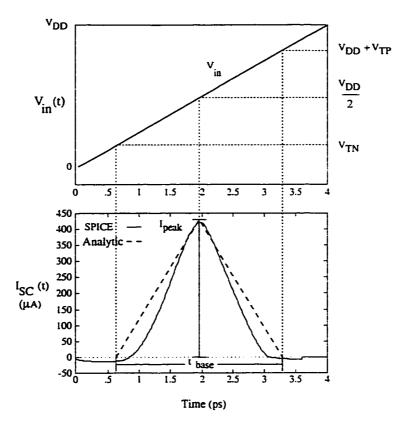

due to a slow input transition, and for a balanced inverter, the peak current occurs near the middle of the input transition. An example of short-circuit current is shown by the solid line in the lower graph of Figure 3.5, *i.e.*, the SPICE-derived data.

The total short-circuit current  $I_{SC}$  can be estimated by modeling  $I_{SC}$  as a triangle. Therefore, the integral of  $I_{SC}$  is the area of a triangle,  $\frac{1}{2}base \times height$ . In terms of the short-circuit current, the height can be modeled as  $I_{peak}$  and the base can be modeled as  $t_{base}$  (see Figure 3.5).  $I_{peak}$  is the maximum saturation current of the load transistor and depends on both  $V_{GS}$  and  $V_{DS}$ , therefore  $I_{peak}$  is both input waveform and load dependent.  $t_{base}$  is the time during which both the P-channel and the N-channel transistors are turned on, permitting a DC current path to exist between  $V_{DD}$  and ground. This time occurs over the region,  $V_{TN} \leq V_{in} \leq V_{DD} + V_{TP}$ . Therefore,  $t_{base}$  is found from the difference between (3.7) and (3.8),  $|(t_{V_{TP}} - t_{V_{TN}})|$ . The area defined by this triangle is  $\frac{1}{2}I_{peak} \times t_{base}$ , which models the total short-circuit current  $I_{SC}$  sourced by a CMOS inverter due to a non-step input [38].

Figure 3.5: Graphical estimation of short-circuit current (0.8  $\mu$ m CMOS technology)

The total short-circuit current multiplied by f and  $V_{DD}$  is the short-circuit power. The short-circuit power dissipation  $P_{SC}$  of the following stage for one transition (either rising or falling edge) can therefore be approximated by

$$P_{SC} = \frac{1}{2} I_{peak} t_{base} V_{DD} f. \tag{3.9}$$

Subtracting (3.7) from (3.8) forms the logarithmic quotient,

$$t_{base} = \left| \ln \left( \frac{V_{TN}}{V_{DD} + V_{TP}} \right) \right| \frac{C + \mathcal{O}_{do}RC}{\mathcal{O}_{do}}. \tag{3.10}$$

By inserting this expression for  $t_{base}$  into (3.9), the short-circuit power dissipation  $P_{SC}$  of a CMOS inverter following a lumped RC load over both the rising

and falling transitions is

$$P_{SC} = \left| \ln\left(\frac{V_{TN}}{V_{DD} + V_{TP}}\right) \right| \frac{C + \mathcal{V}_{do}RC}{\mathcal{V}_{do}} I_{peak} f V_{DD} \qquad (3.11)$$

#### Analysis of the Expression for Short-Circuit Power Dissipation

The short-circuit power derived from (3.11) for a wide range of RC loads between the CMOS inverter stages shown in Figure 3.4 is compared with SPICE in Table 3.2. The RC load of the driving inverter is described in the first two columns of Table 3.2. The short-circuit power predicted by (3.11) and derived from SPICE is shown in the third and fourth columns, respectively. The per cent error between the analytical expression and SPICE is shown in the final column.

For smaller RC loads, hence, faster transition times, there is negligible short-circuit power since a direct path from the power supply to ground does not exist for any significant time. The short-circuit power becomes non-negligible when larger interconnect loads between the two CMOS stages cause a transition time of significant magnitude e.g., a  $t_t$  greater than 0.5 ns for a 0.8  $\mu$ m CMOS inverter. At this borderline value, the analytical  $P_{SC}$  differs from SPICE by a maximum of 41%. As the RC load and transition time increase, the analytical model more closely predicts the short-circuit current derived from SPICE. For RC delays exceeding 0.1 ns, errors less than 15% are attained. Furthermore, the short-circuit power becomes a significant portion of the total power dissipation when the CMOS inverter is loaded by larger RC loads, creating long transition times. It is this condition that is of greatest interest when considering short-circuit power in resistively loaded CMOS inverters.

The error of the analytical expression for  $P_{SC}$  can be bounded by the RC

Table 3.2: Estimate of short-circuit power dissipated by a CMOS inverter (0.8  $\mu$ m CMOS technology)

| Interconnect | Interconnect | Pow      | er (µW)                                    | % Error |

|--------------|--------------|----------|--------------------------------------------|---------|

| Resistance   | Capacitance  | f = 10MF | $f = 10 \text{MHz}, V_{DD} = 5.0 \text{V}$ |         |

|              |              | Analytic | SPICE                                      |         |

| 10 Ω         | .3 pF        | 1.4      | .99                                        | 41%     |

| 10 Ω         | .5 pF        | 3.9      | 3.22                                       | 21%     |

| 10 Ω         | 1 pF         | 12.4     | 11.1                                       | 12%     |

| 100 Ω        | .3 pF        | 1.71     | 1.23                                       | 39%     |

| 100 Ω        | .5 pF        | 4.68     | 3.83                                       | 22%     |

| 100 Ω        | 1 pF         | 13.8     | 12.7                                       | 9%      |

| 1000 Ω       | .3 pF        | 5.85     | 5.2                                        | 12%     |

| 1000 Ω       | .5 pF        | 13.0     | 12.2                                       | 7%      |

| 1000 Ω       | 1 pF         | 34.2     | 33.8                                       | 1%      |

time constant describing the interconnect load impedance. For a 0.8  $\mu$ m CMOS technology, the per cent error is less than 15% for an RC time constant more than 0.1 ns. For an RC time constant less than 0.1 ns, the per cent error increases to approximately 40%.

One source of error in estimating the short-circuit power derived from (3.9) can be found by examining the transition time. The analytical solution to the transition time, (3.6), generally yields pessimistic results when compared to SPICE (see Table 3.1). By inserting these pessimistic transition times into (3.9), the resulting short-circuit power is also pessimistic, as demonstrated in Table 3.2.

Another source of error is caused by signal undershoot of fast transient waveforms. This parasitic-induced undershoot may increase  $V_{DS}$  above  $V_{DD}$  or below ground. This undershoot occurs early during the transition time and causes current to flow opposite to the expected direction, thereby reducing the total shortcircuit current. This behavior, in turn, reduces the total short-circuit power, increasing the discrepancy between SPICE and (3.11), which does not consider transient undershoot. The phenomenon of signal undershoot, where the current is negative, can be seen in Figure 3.5.

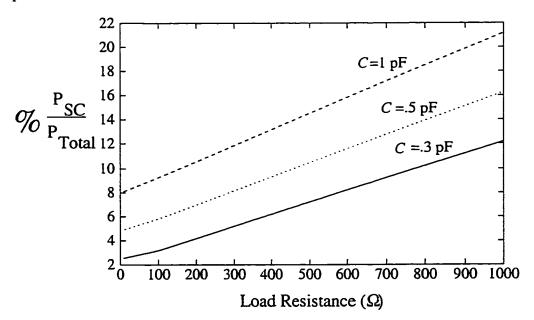

#### Short-Circuit Power as Compared to the Total Transient Power

For a given supply voltage and frequency, dynamic power dissipation depends only on the load capacitance and does not depend on the input waveform shape or load resistance. In contrast, the short-circuit power dissipation changes with both input waveform shape and output load resistance and capacitance. The ratio of the short-circuit power to the total transient power (the sum of the dynamic and short-circuit power) of a CMOS inverter with respect to the load resistance R for a given load capacitance C is shown in Figure 3.6. Note that with increasing load resistance, the short-circuit power dissipation cannot be neglected, since, as shown in Figure 3.6, it can comprise more than 20% of the total transient power dissipation.

Figure 3.6: Ratio of short-circuit power to total transient power versus interconnect resistance for varying interconnect capacitance

### 3.2.3 Resistive Power Dissipation

In resistive interconnect, power is not only dissipated when charging and discharging the load capacitance, but power is also dissipated by the load resistance. This power dissipation can be quantified by  $f \int_t (i^2 R)$ , where i is the current through the load resistance and f is the frequency of operation. The identical current that is discharged by the capacitor flows through the resistor. This capacitive current is  $I_C = C \frac{dV_{out}}{dt}$ . Therefore, by taking the derivative of (3.4), the instantaneous current through a resistive load  $i_R(t)$  is given by

$$i_R(t) = \frac{-\mathcal{O}_{do}}{1 + \mathcal{O}_{do}R} V_{out}(0) e^{\frac{-\mathcal{O}_{do}}{\mathcal{O}_{do}RC + C}t} \qquad , \tag{3.12}$$

and the average resistive power dissipation is given by